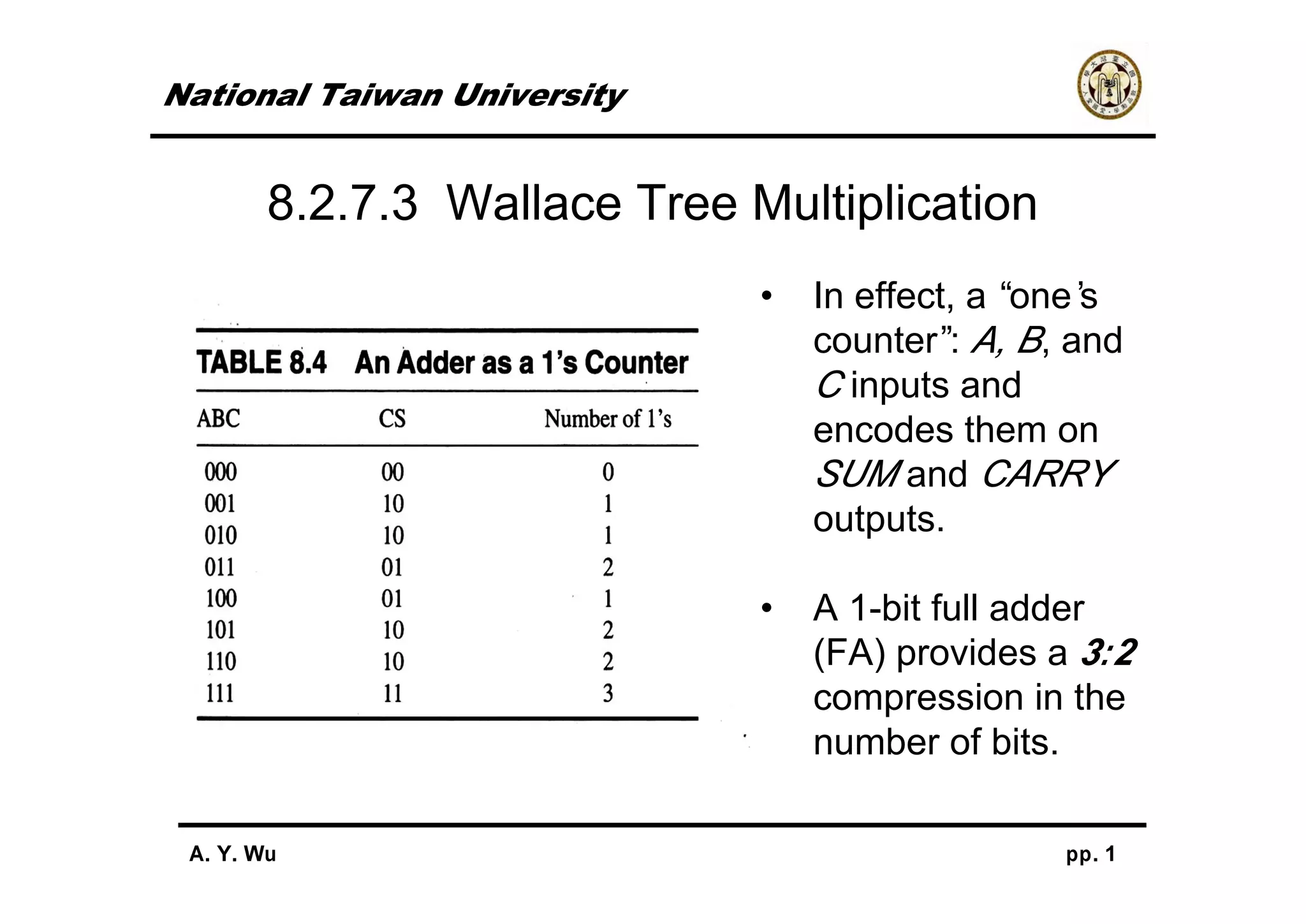

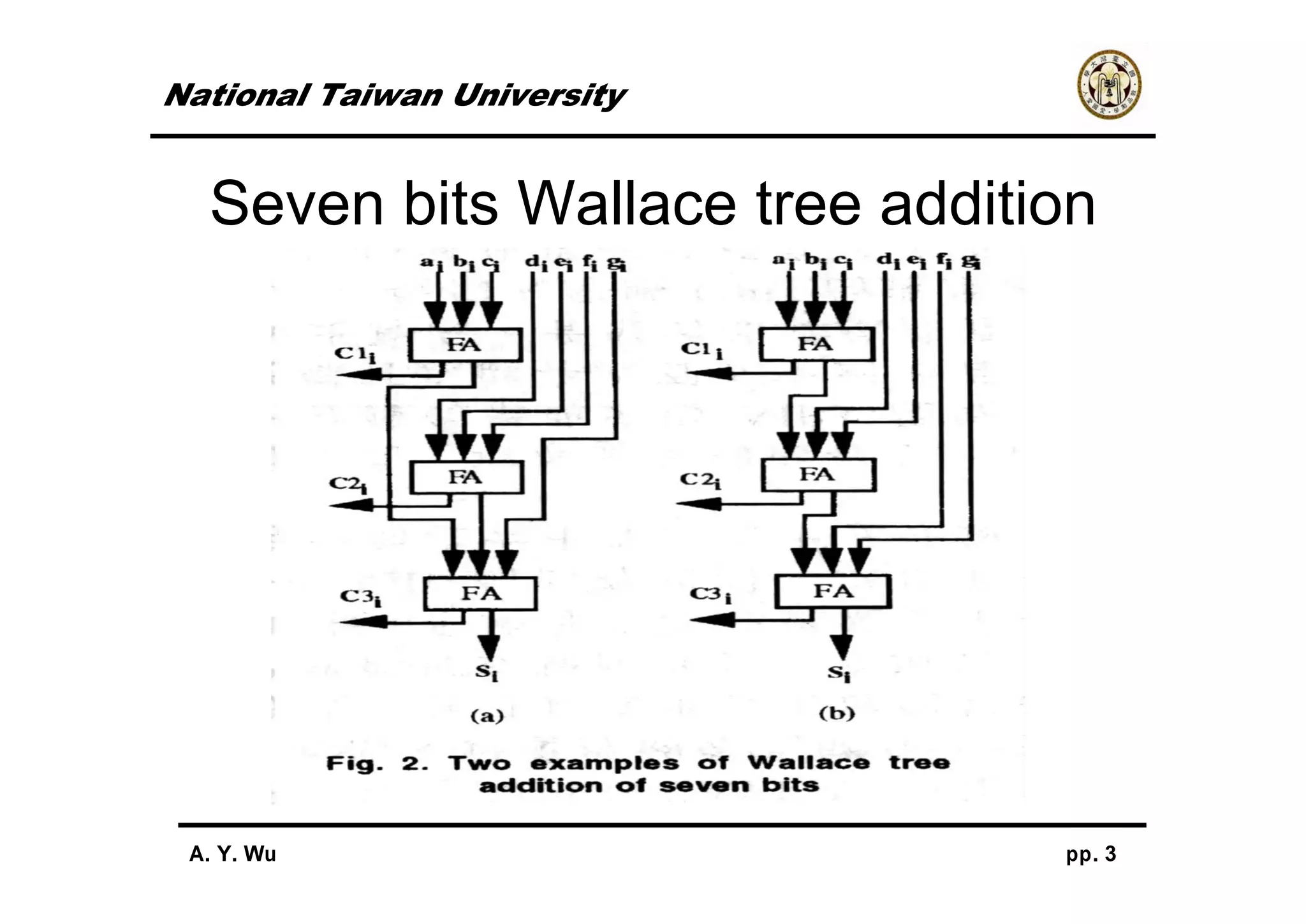

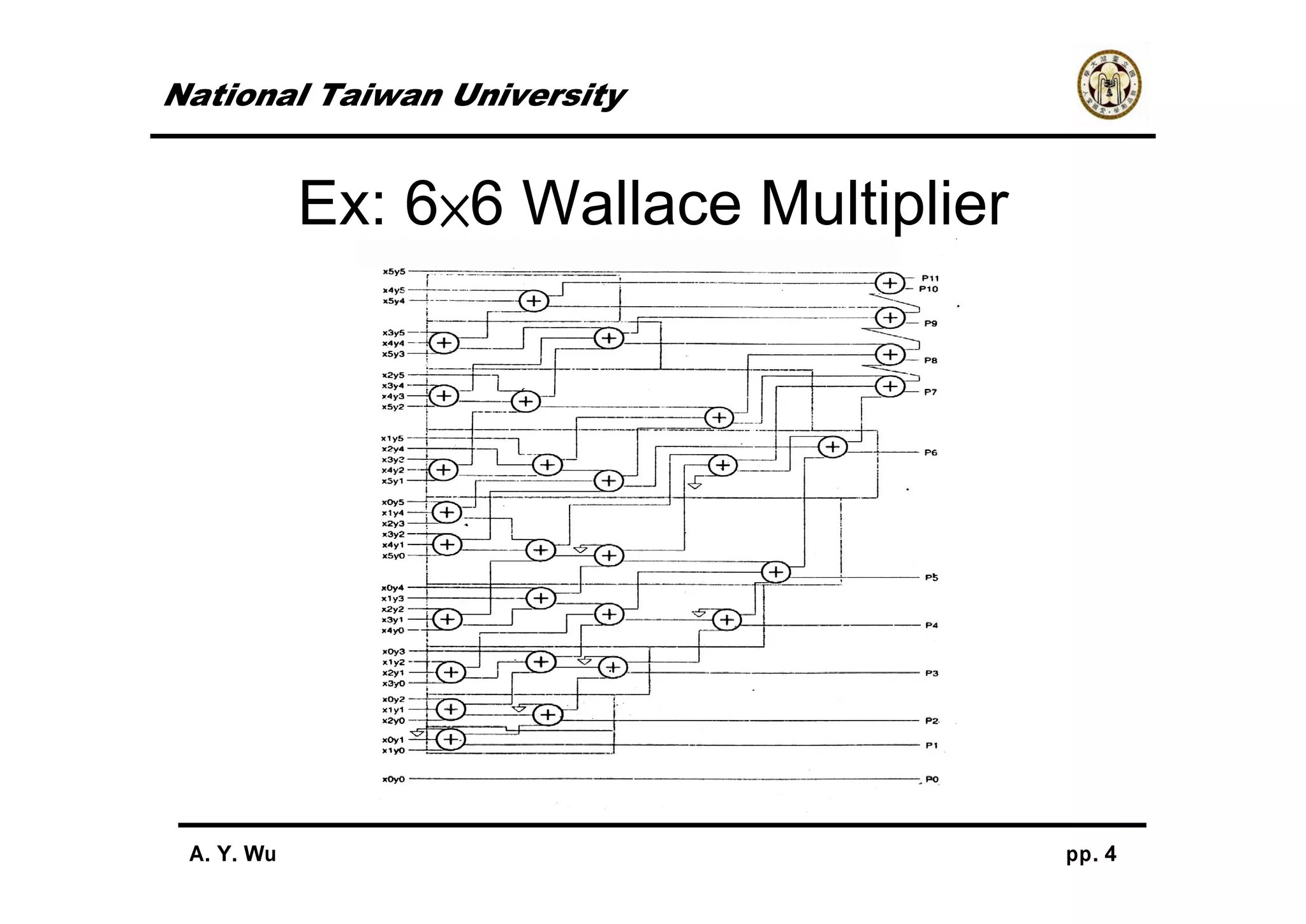

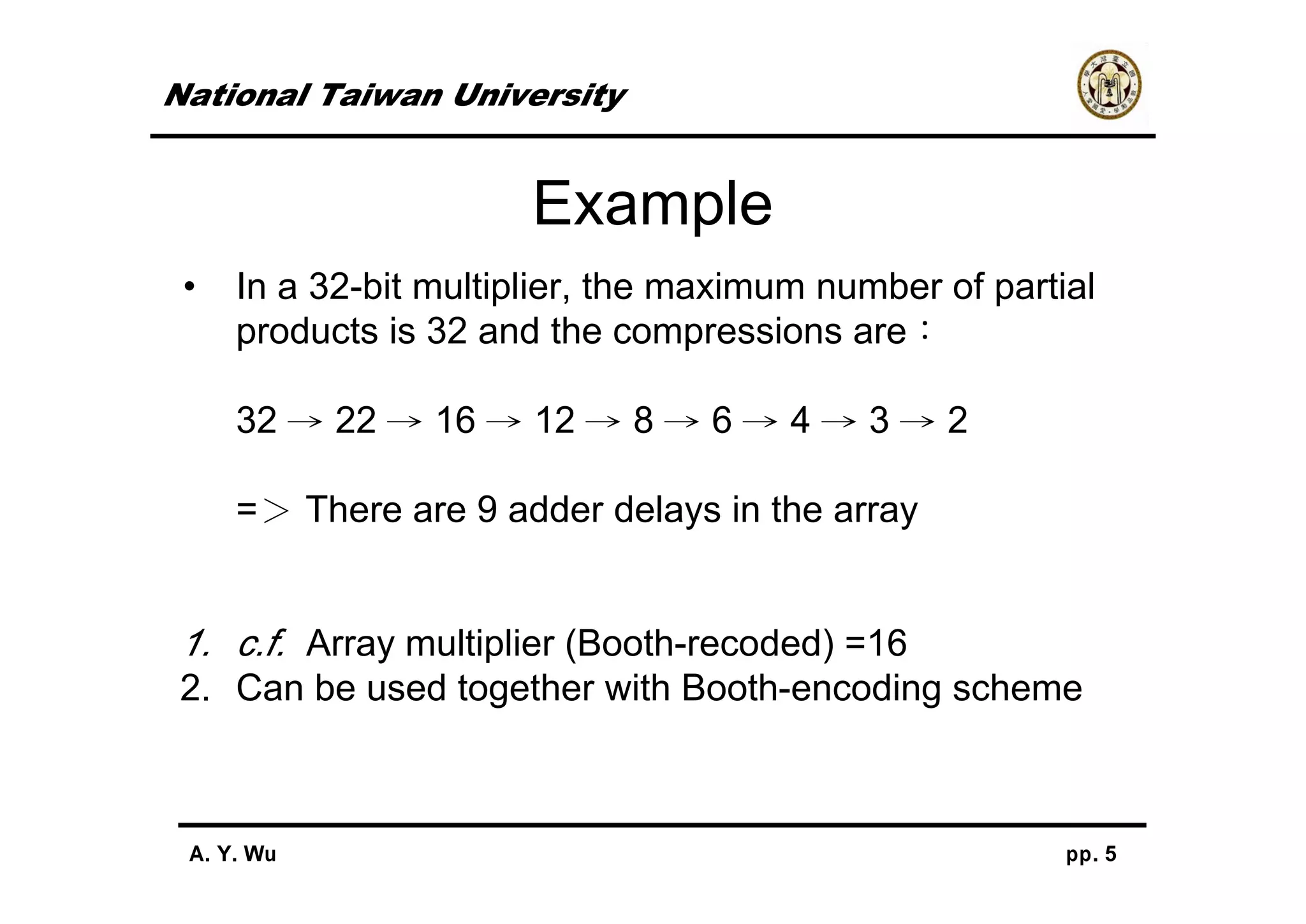

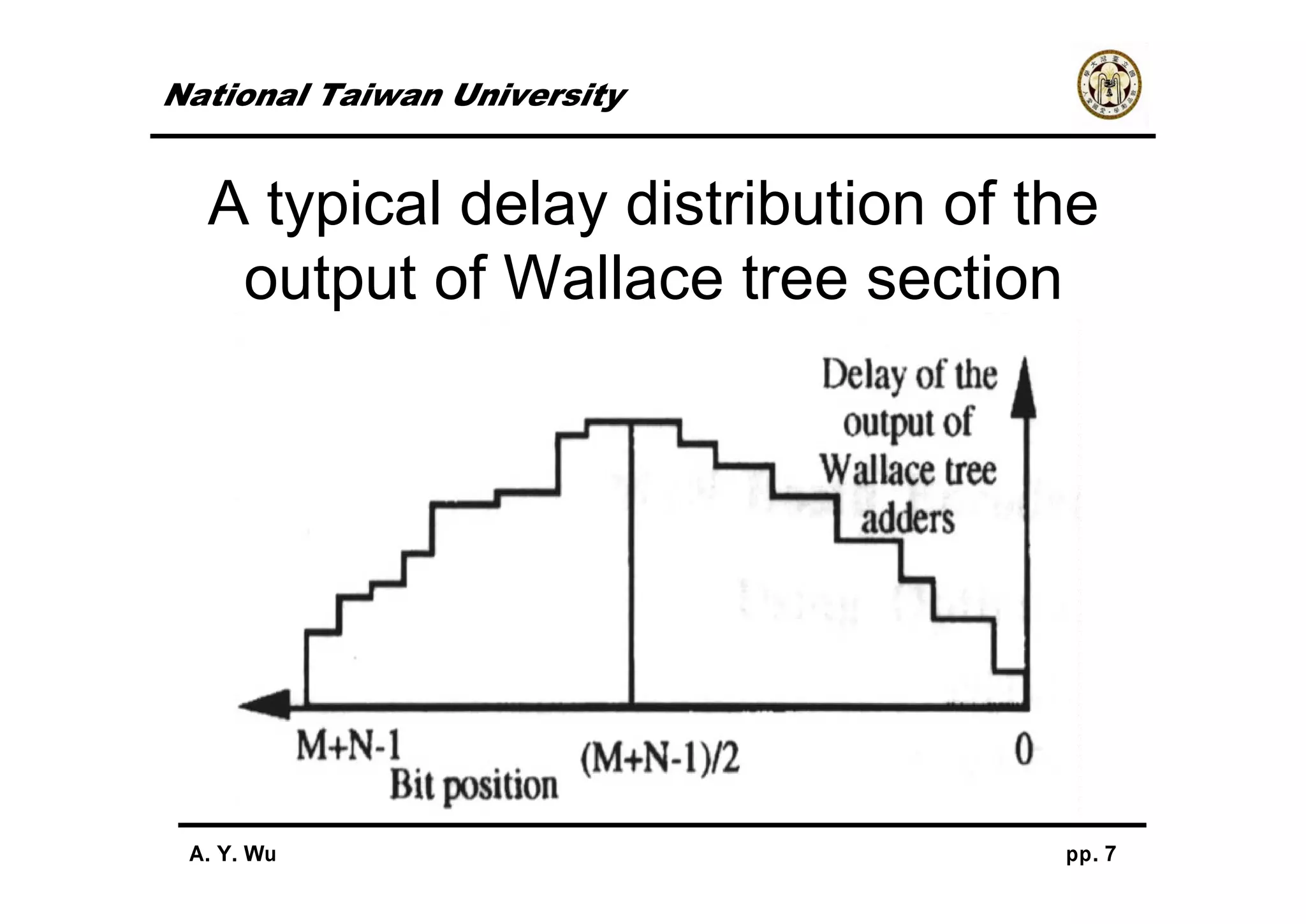

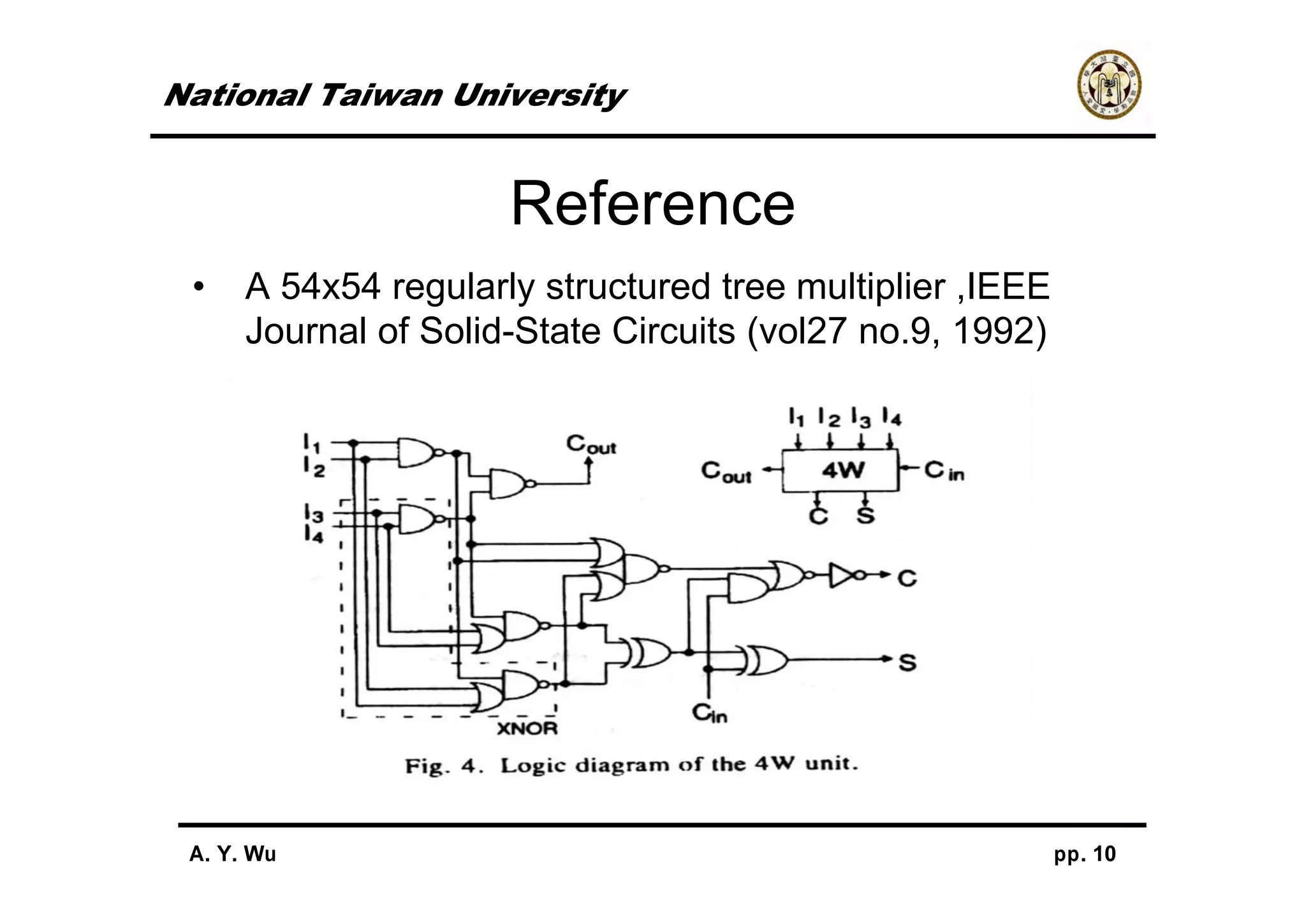

This document discusses Wallace tree multiplication. It begins by explaining the basic concept of a Wallace tree multiplier using 1-bit full adders to compress the number of bits at each stage. It then provides examples of 6x6 multipliers using Wallace trees. It notes that a 32-bit multiplier using this method would have 9 adder delays. Finally, it asks questions about extending this to a 64-bit multiplier and whether other compression schemes could reduce the delay further.