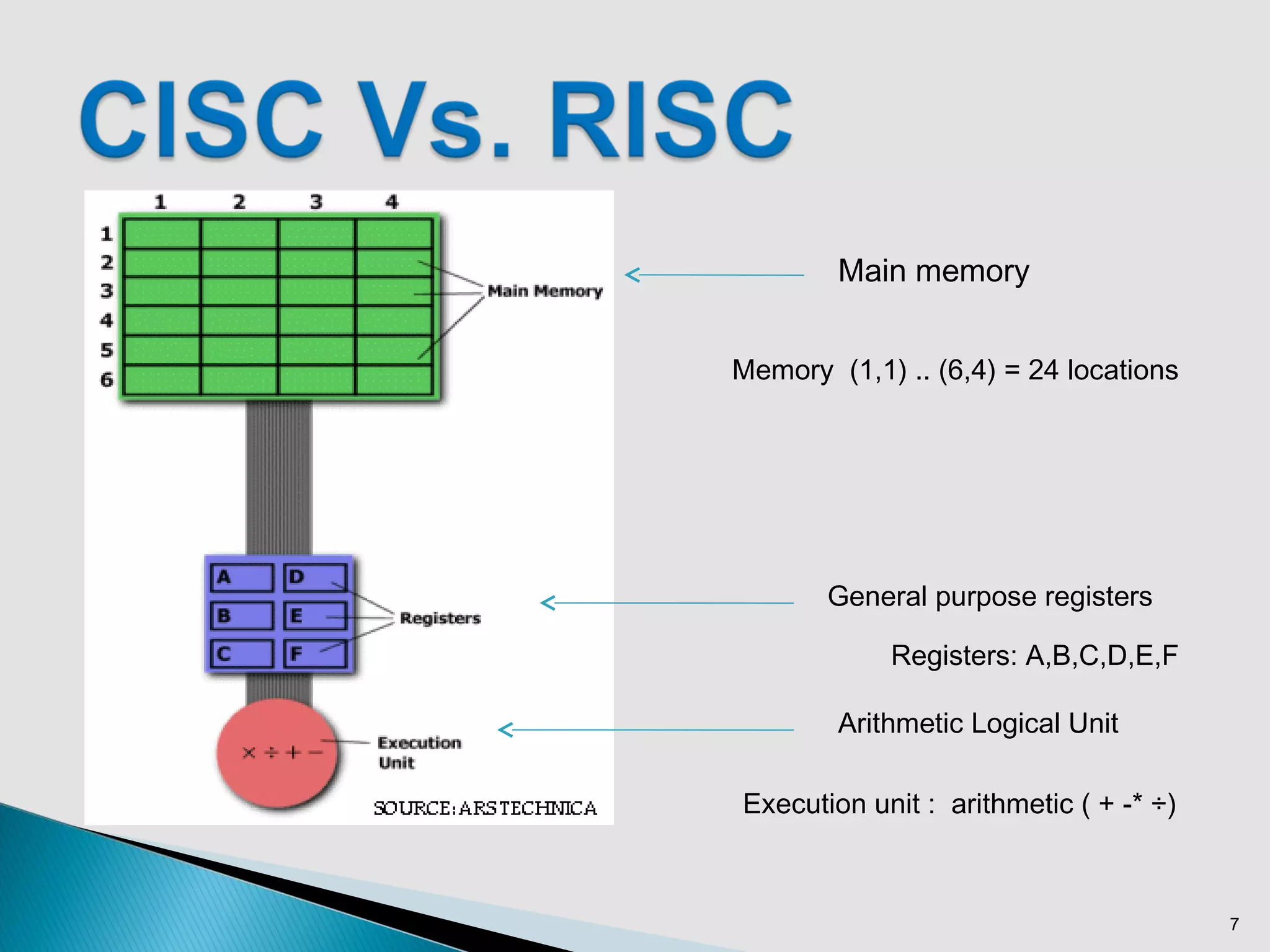

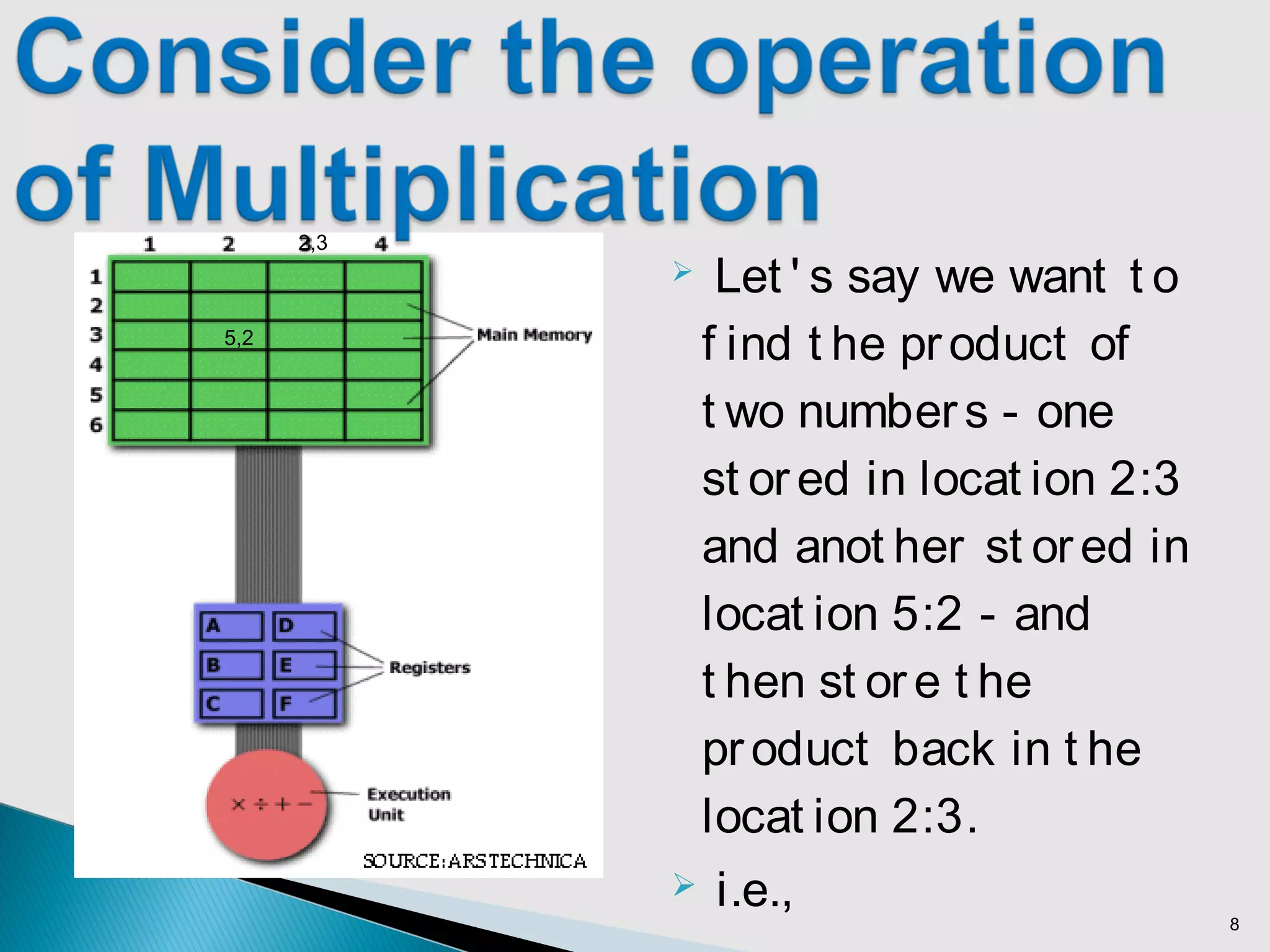

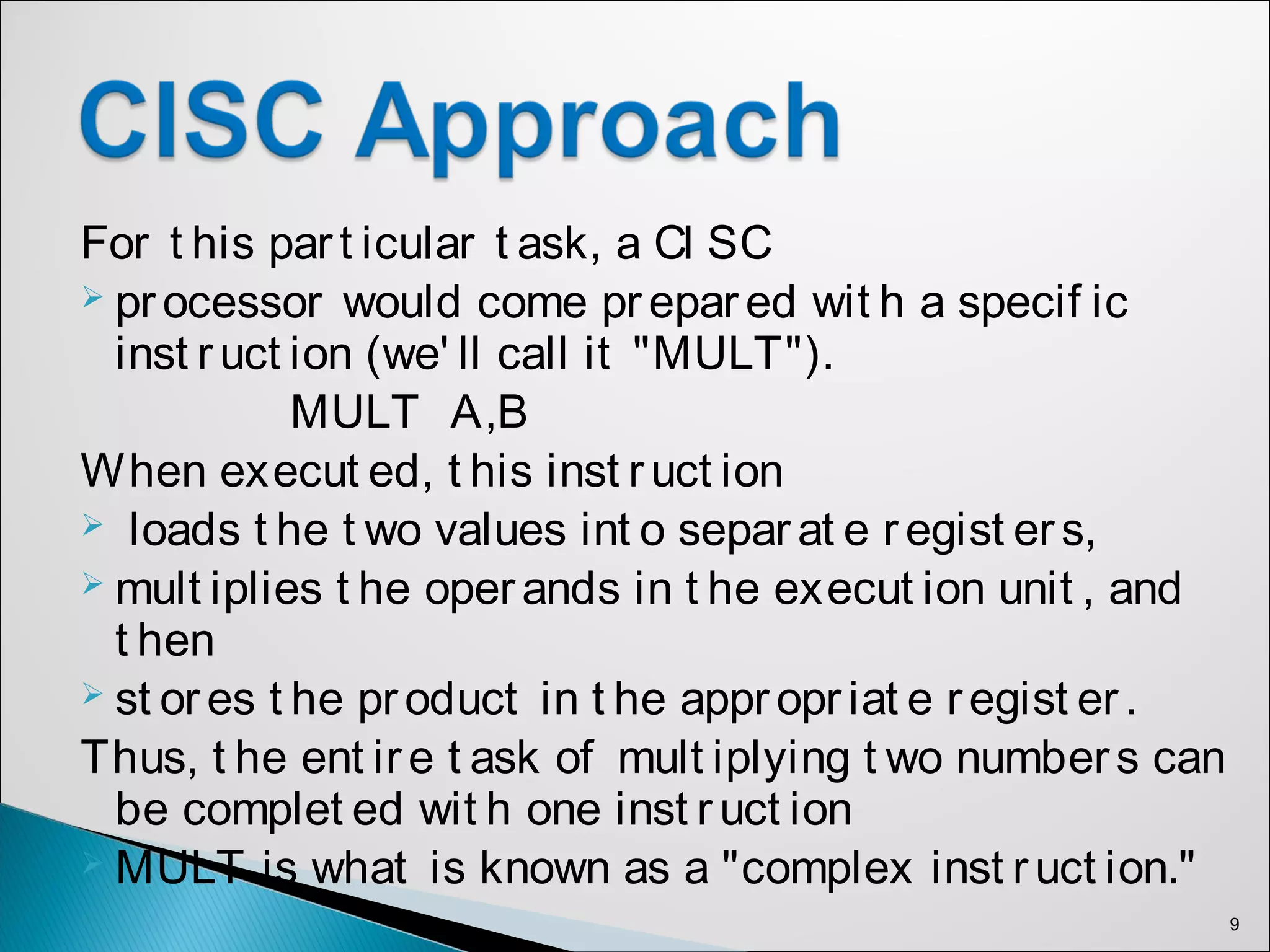

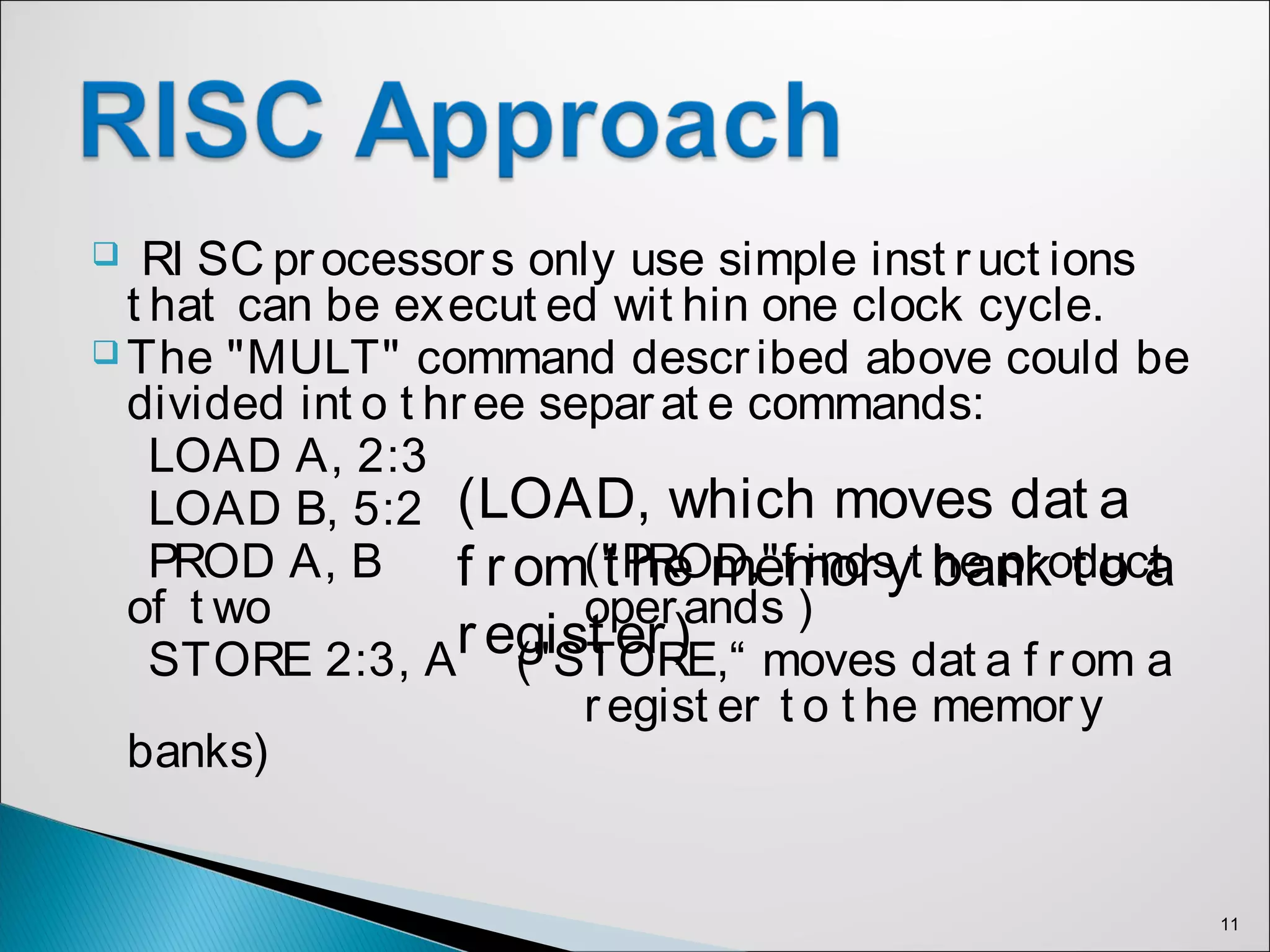

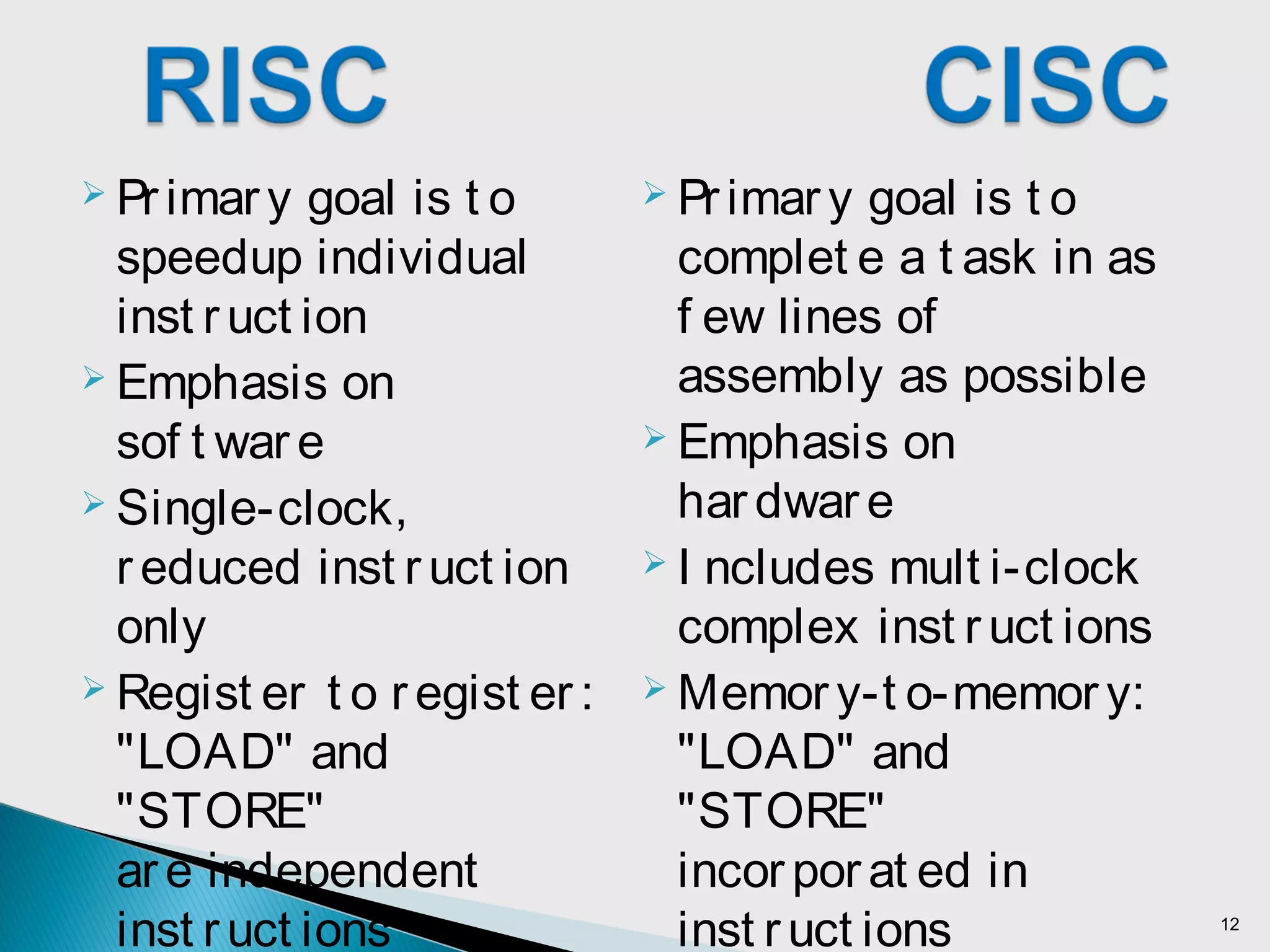

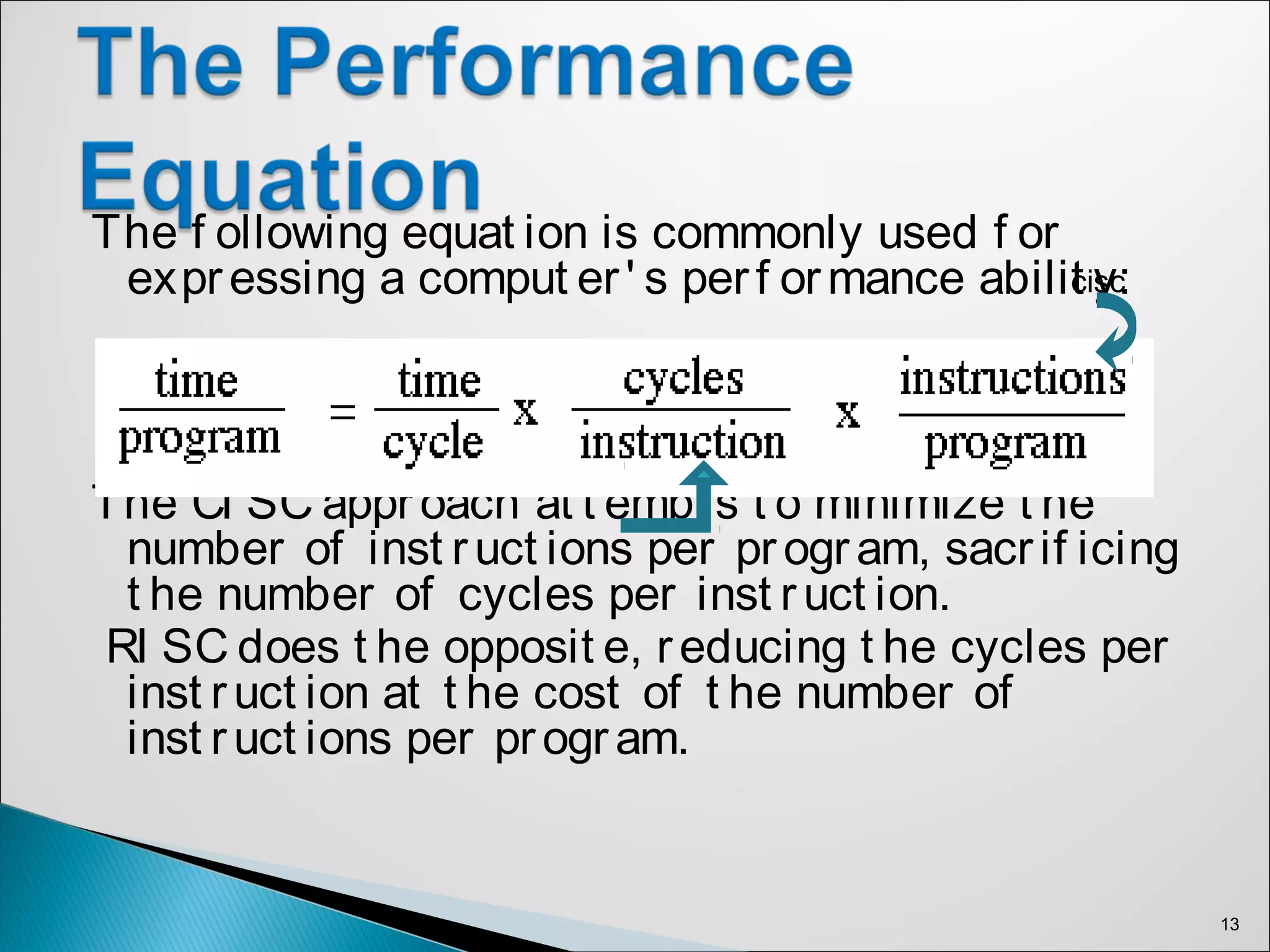

The document discusses Complex Instruction Set Computers (CISC) and their advantages over Reduced Instruction Set Computers (RISC). CISC processors use complex instructions that can perform multiple operations like loading from memory, arithmetic, and storing in a single instruction. This reduces the number of instructions per program at the cost of multiple clock cycles per instruction. In contrast, RISC processors use simpler single-cycle instructions, increasing the number of instructions but reducing clock cycles per instruction. There is ongoing debate about the performance of CISC vs RISC architectures as they incorporate each other's features over time.