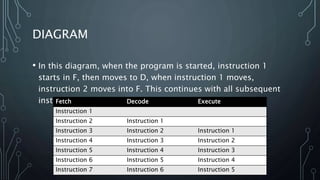

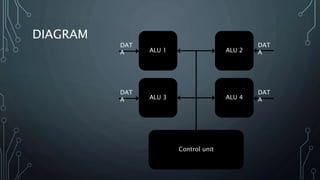

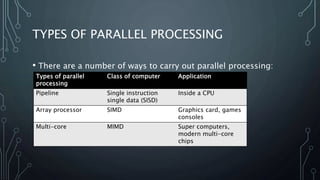

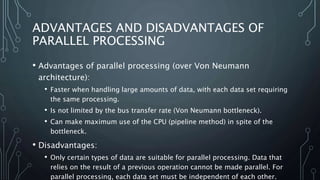

Pipelining allows multiple instructions to be processed simultaneously by splitting the fetch-decode-execute cycle into stages so different instructions can be at different stages. Array or vector processors can perform the same operation on multiple data elements in parallel using multiple ALUs. Parallel processing can happen at different levels from pipelining within a CPU to multi-core and multiprocessor systems that distribute work across CPUs. RISC processors use simpler instructions that can complete in one cycle while CISC processors have more complex instructions implemented in hardware.