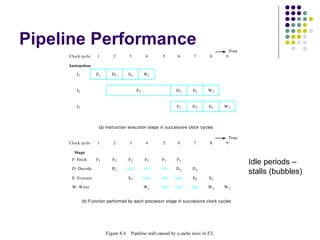

Pipelining allows the execution of multiple instructions simultaneously by dividing instruction processing into discrete stages. This improves processor throughput. Common pipeline stages include fetch, decode, execute, and writeback. Pipelining is used in modern CPUs but hazards like structural, data, and branch hazards can cause the pipeline to stall, degrading performance. Coprocessors are secondary processors that supplement the main CPU by accelerating tasks like floating-point arithmetic, graphics processing, and encryption. The Intel 8087 was an early numeric coprocessor that offloaded floating-point operations from the 8086/8088 CPU.