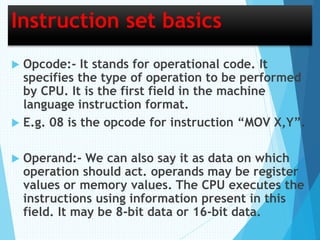

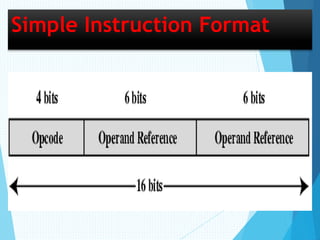

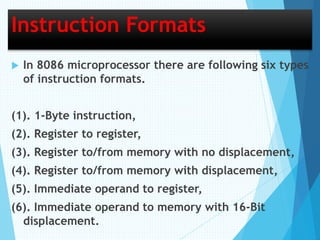

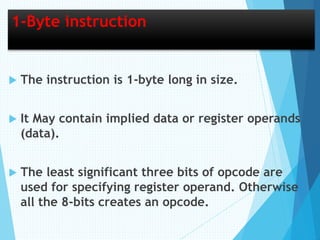

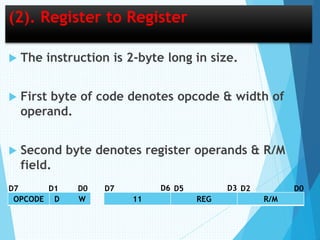

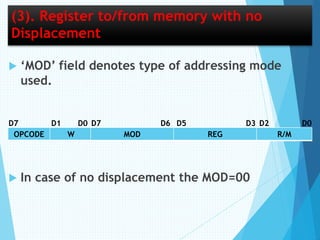

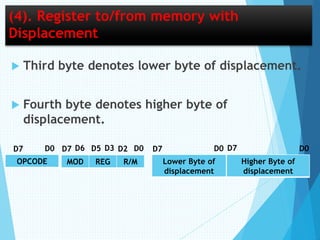

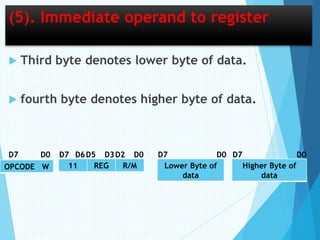

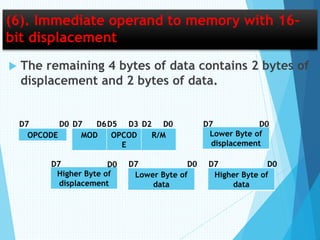

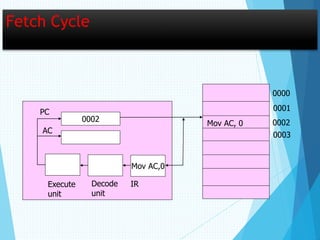

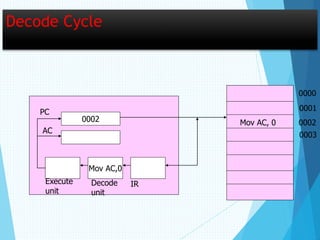

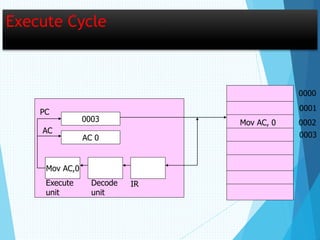

The document describes the instruction set of the 8086 microprocessor. It discusses that an instruction set consists of instructions understood by the CPU. The 8086 has six instruction formats - 1-byte, register to register, register to/from memory with no displacement, register to/from memory with displacement, immediate operand to register, and immediate operand to memory with 16-bit displacement. Each instruction format specifies the opcode, operands, and other fields to indicate the operation to be performed. The instruction cycle of the 8086 involves fetching an instruction from memory, decoding the instruction, and executing the instruction.