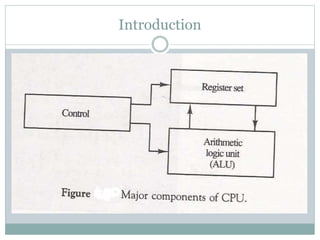

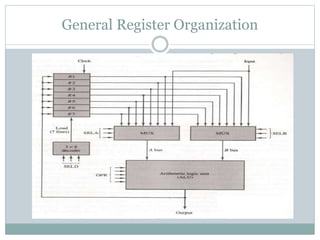

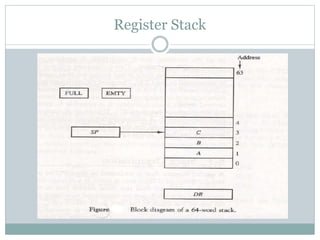

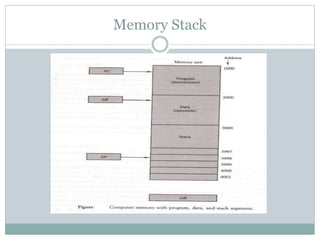

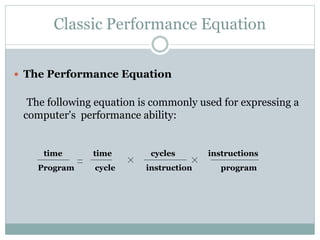

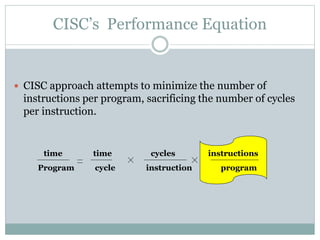

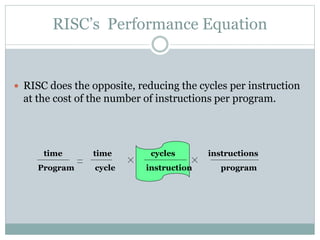

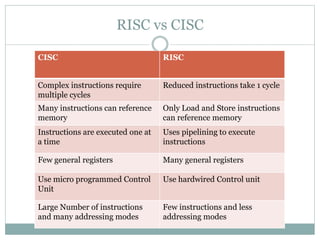

This document discusses CPU organization, instruction formats, addressing modes, and characteristics of RISC and CISC architectures. It covers general register and stack organizations, different instruction formats like zero, one, two, and three address formats. It also covers various addressing modes and describes key differences between RISC and CISC designs like instruction complexity, number of registers, and use of microprogramming versus hardwired control units. The document discusses performance considerations for RISC versus CISC in terms of instructions per program and cycles per instruction.