Embed presentation

Downloaded 14 times

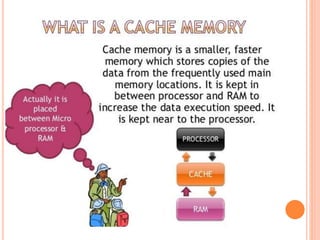

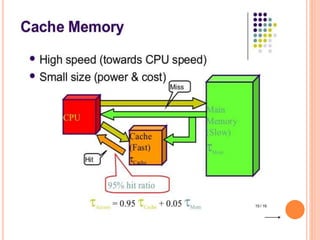

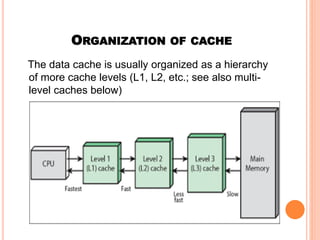

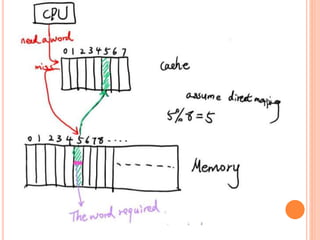

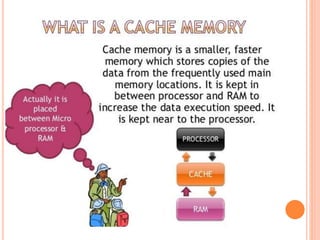

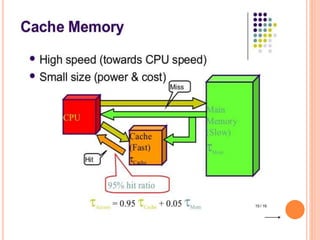

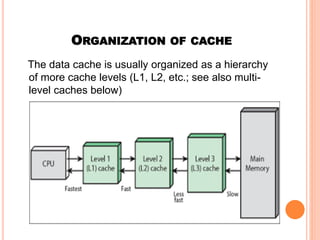

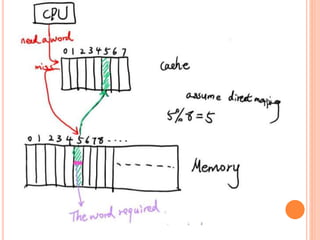

Cache memory is a type of fast memory located between the CPU and main memory that stores recently accessed data. It was developed in the 1970s by Maurice Wilkes to address the issue of main memory access times increasing as memory sizes grew. Modern CPUs typically have three levels of cache - an instruction cache to speed up fetching of executable instructions, a data cache to speed up data fetching and storing, and a translation lookaside buffer to speed up virtual-to-physical address translation for both instructions and data. Cache is organized hierarchically and transfers data between memory and cache in fixed-size blocks called cache lines.