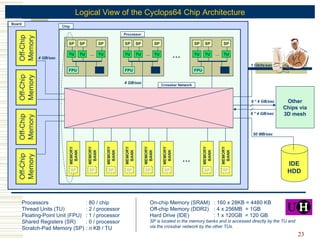

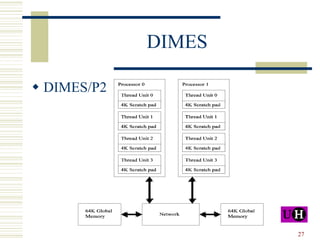

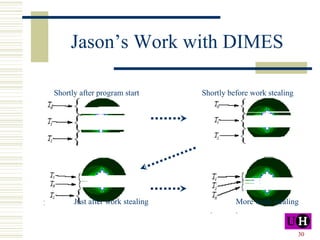

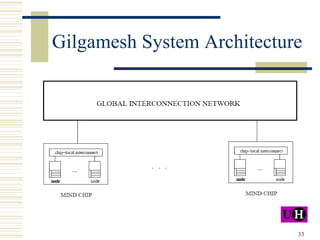

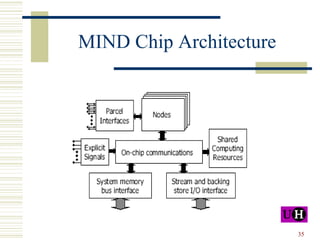

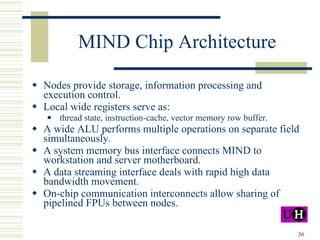

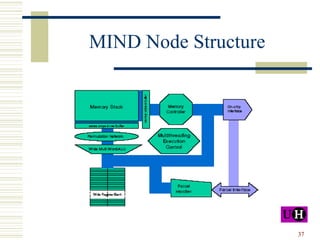

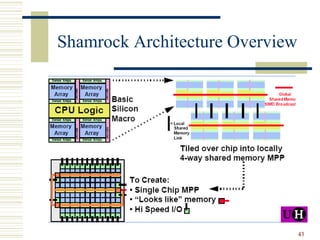

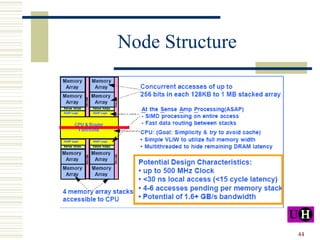

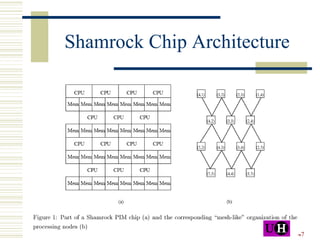

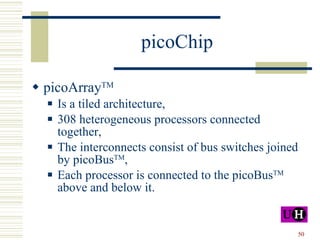

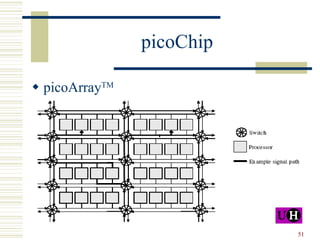

This document discusses massively parallel architectures and processing in memory (PIM) as ways to overcome the memory wall problem. It describes several PIM and cellular architectures including Cyclops, Gilgamesh, Shamrock, picoChip and DIMES. DIMES is an FPGA implementation of a simplified cellular architecture that was used by Jason McGuiness to test programming approaches. The talk concludes with an invitation for questions.