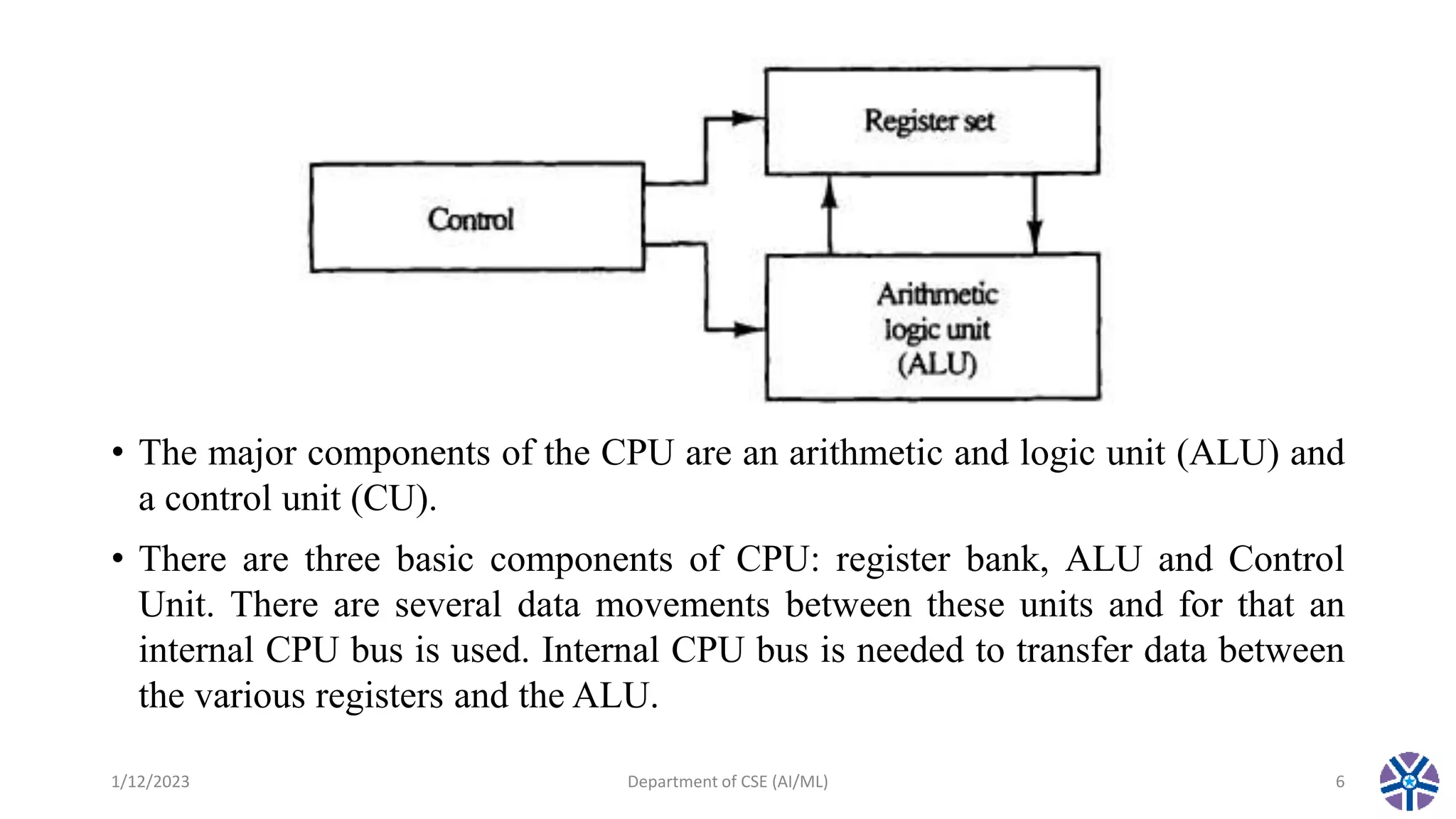

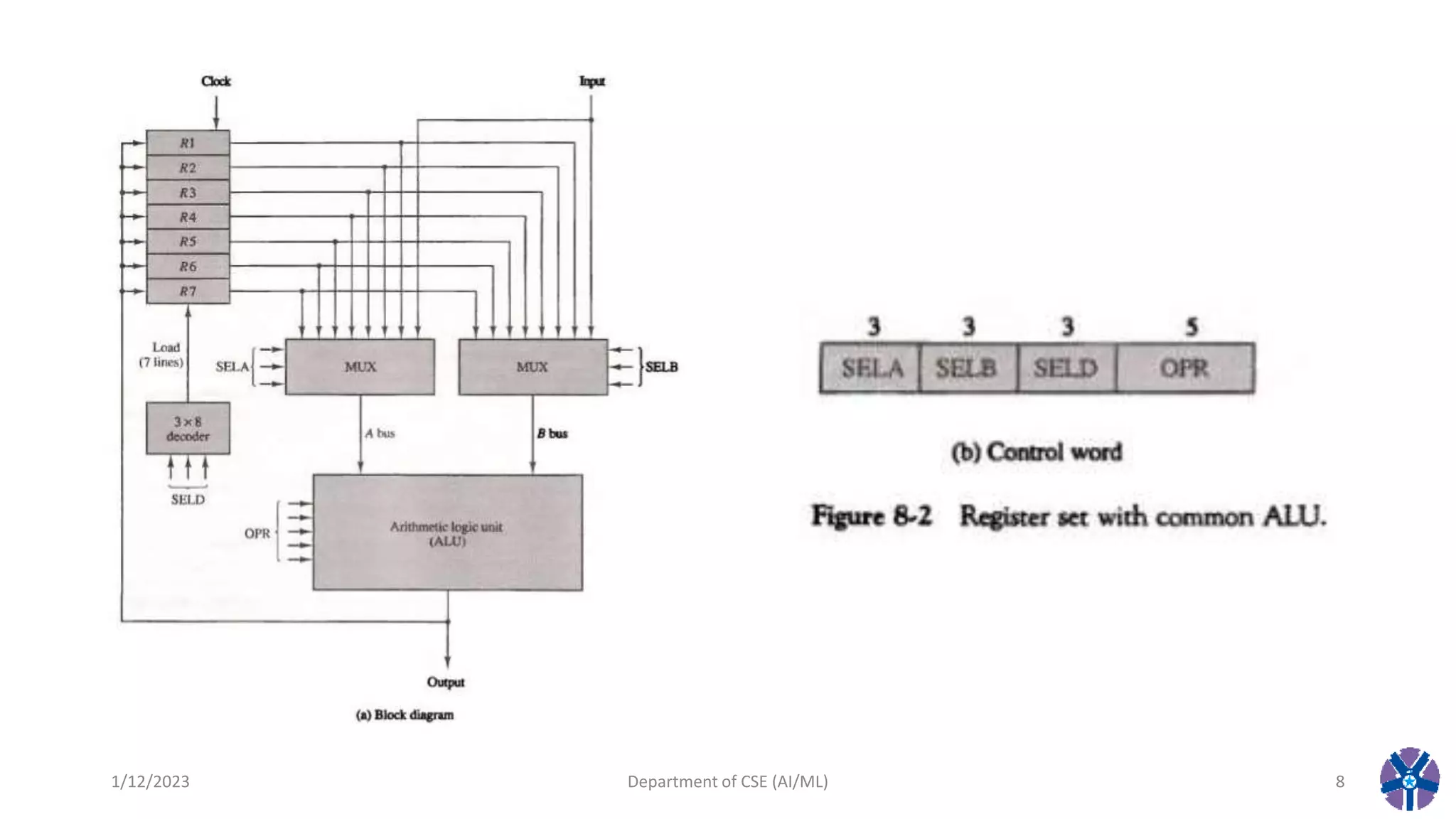

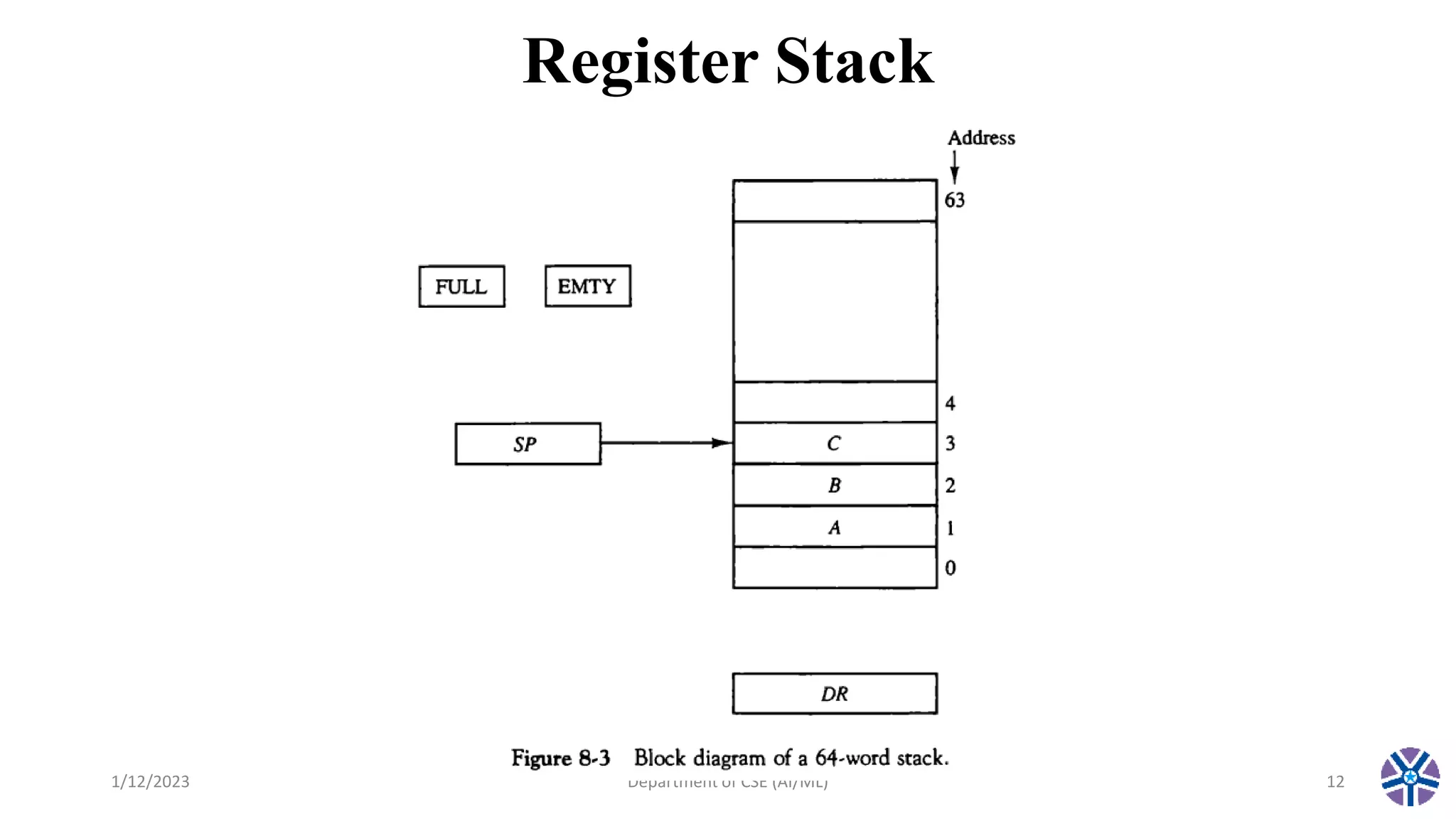

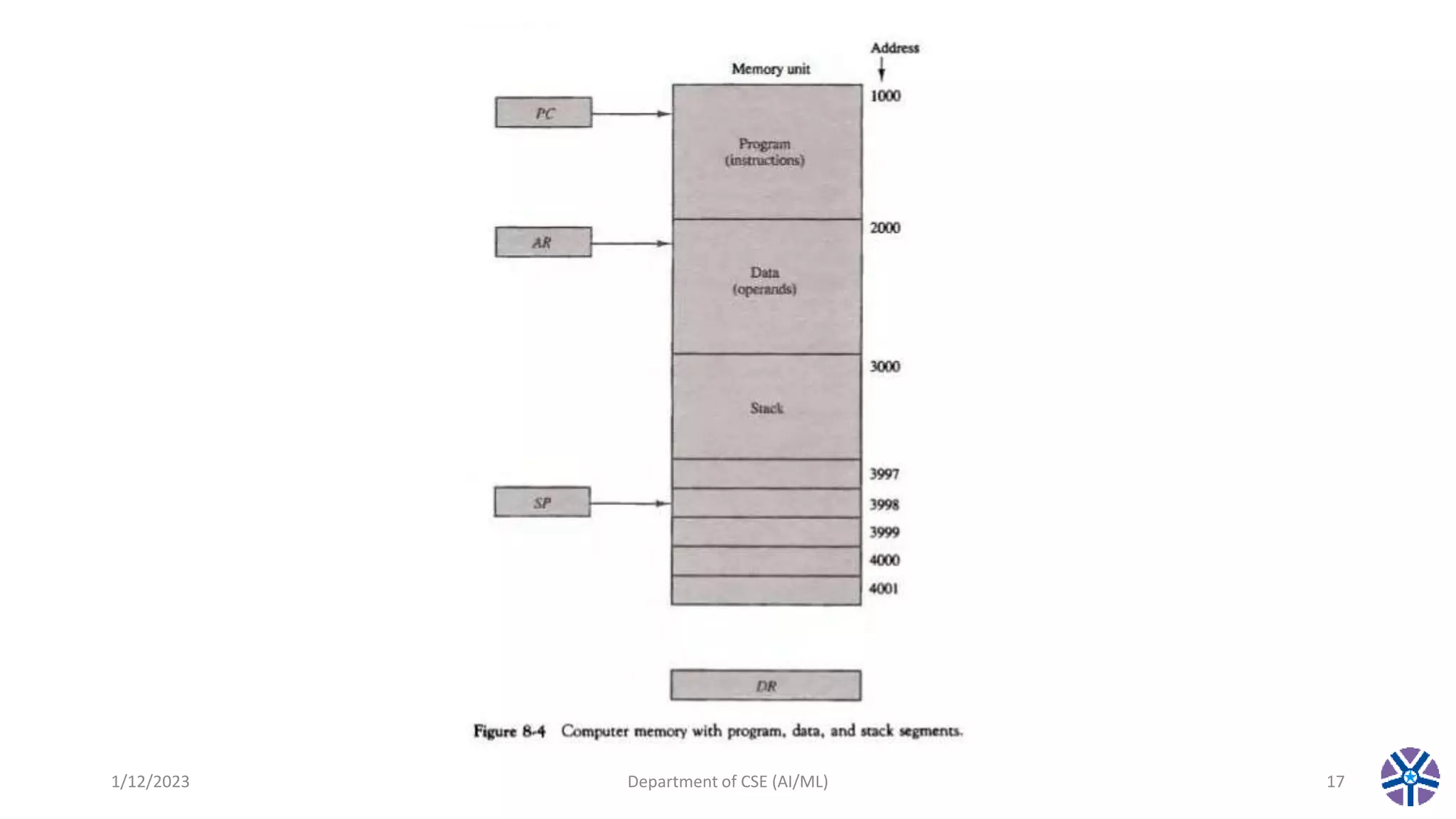

This document summarizes a session on computer organization and architecture. It discusses topics like general register organization, instruction formats, addressing modes, data transfer and manipulation, and program control. It provides details on central processing unit components and operations. It also describes stack organization, including register stacks stored in CPU registers and memory stacks stored in a designated memory region, with push and pop operations controlled by a stack pointer. The next session is planned to cover instruction formats.