binary decrementer.pdf

•

0 likes•184 views

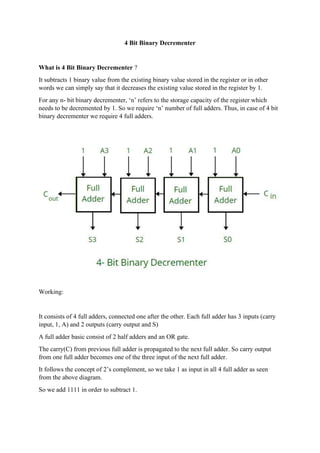

A 4 bit binary decrementer consists of 4 full adders connected in series. It subtracts 1 from the binary value stored in a 4 bit register by adding 1111 in binary. Representing -1 in 2's complement is 1111. So by adding 1111, the decrementer decreases the register value by 1 following the concept of 2's complement arithmetic.

Report

Share

Report

Share

Download to read offline

Recommended

BJT CE

This document provides an overview of bipolar junction transistors (BJTs) including:

- The common emitter, common base, and common collector configurations and their key characteristics like voltage/current gain, input/output impedance, and frequency response.

- How to determine the quiescent operating point and calculate small signal performance for the common emitter configuration.

- Equations for calculating the input and output impedance of the common emitter configuration.

- How coupling and bypass capacitors affect the frequency response and how to determine the lower 3dB frequency cutoff.

State transition diagram 8085

The document discusses state transition diagrams and the various states of the 8085 microprocessor. It provides details on the T1-T6 states which represent the clock cycles, as well as the TRESET, THALT, TWAIT, and THOLD states. The TRESET state occurs when the reset signal is active, THALT occurs after HLT instruction execution, TWAIT inserts extra cycles for slow memory/I/O, and THOLD occurs when the HOLD signal requests DMA access. Transition diagrams are shown for the THALT and THOLD states to illustrate the different state changes.

Combinational Circuits & Sequential Circuits

This document discusses and compares combinational and sequential circuits. It provides examples of common combinational circuits like half adders, full adders, decoders, and multiplexers. It also discusses sequential circuits elements like flip flops and shift registers. The document then focuses on adders in more detail, explaining half adders, full adders, and ripple carry adders through diagrams and examples.

Encoders and decoders

This document discusses various encoders and decoders used in digital circuits. It describes decimal to BCD encoders that convert decimal numbers to binary coded decimal. Priority encoders are discussed that compress multiple inputs into fewer outputs based on priority. Decoders discussed include BCD to decimal decoders that convert BCD to decimal numbers, and seven segment decoders that convert codes to activate the segments of seven segment displays. Applications of encoders and decoders include data communications, compression, security, and making data human readable.

Booth’s algorithm.(a014& a015)

This document provides an overview of Booth's algorithm for multiplying signed and unsigned integers. It begins with an introduction and history, noting that the algorithm was invented by Andrew Donald Booth in 1950. It then explains the key points of Booth's algorithm through a flow chart and examples. For unsigned integers, it uses fewer additions/subtractions than other methods by conditionally adding or subtracting the multiplicand. For signed integers, it first converts them to unsigned using 2's complement before applying the same process.

Subtractor

The document discusses binary subtraction and different types of binary subtractors. It describes half subtractors and full subtractors. A half subtractor is a basic circuit that can subtract two binary bits and outputs the difference and borrow. A full subtractor can subtract three bits by also considering the borrow from the previous stage. Truth tables and K-maps are used to derive the logic equations for difference and borrow outputs. Full subtractors are realized using basic gates by complementing one input to convert a full adder circuit into a full subtractor.

Combinational circuits

This document discusses combinational logic circuits such as adders, subtractors, multipliers, decoders, and multiplexers. It provides circuit diagrams and truth tables for half adders, full adders, half subtractors, full subtractors, decoders, and multiplexers. It also describes how to build binary adders and subtractors using these basic components and how multiplication of binary numbers is performed.

differential amplifier for electronic

Here are the steps to solve this:

1) VZ = VBE3 (zener voltage is equal to BJT base-emitter voltage)

2) Using KVL: -VZ + VBE3 + IE3RE = 0

3) Simplify: IE3RE = 0

4) IE3 is constant

Therefore, with a zener diode replacing R2, the current IE3 (and thus IT) remains constant regardless of load or temperature variations. The zener diode acts to stabilize the BJT base-emitter voltage, keeping the current constant.

Recommended

BJT CE

This document provides an overview of bipolar junction transistors (BJTs) including:

- The common emitter, common base, and common collector configurations and their key characteristics like voltage/current gain, input/output impedance, and frequency response.

- How to determine the quiescent operating point and calculate small signal performance for the common emitter configuration.

- Equations for calculating the input and output impedance of the common emitter configuration.

- How coupling and bypass capacitors affect the frequency response and how to determine the lower 3dB frequency cutoff.

State transition diagram 8085

The document discusses state transition diagrams and the various states of the 8085 microprocessor. It provides details on the T1-T6 states which represent the clock cycles, as well as the TRESET, THALT, TWAIT, and THOLD states. The TRESET state occurs when the reset signal is active, THALT occurs after HLT instruction execution, TWAIT inserts extra cycles for slow memory/I/O, and THOLD occurs when the HOLD signal requests DMA access. Transition diagrams are shown for the THALT and THOLD states to illustrate the different state changes.

Combinational Circuits & Sequential Circuits

This document discusses and compares combinational and sequential circuits. It provides examples of common combinational circuits like half adders, full adders, decoders, and multiplexers. It also discusses sequential circuits elements like flip flops and shift registers. The document then focuses on adders in more detail, explaining half adders, full adders, and ripple carry adders through diagrams and examples.

Encoders and decoders

This document discusses various encoders and decoders used in digital circuits. It describes decimal to BCD encoders that convert decimal numbers to binary coded decimal. Priority encoders are discussed that compress multiple inputs into fewer outputs based on priority. Decoders discussed include BCD to decimal decoders that convert BCD to decimal numbers, and seven segment decoders that convert codes to activate the segments of seven segment displays. Applications of encoders and decoders include data communications, compression, security, and making data human readable.

Booth’s algorithm.(a014& a015)

This document provides an overview of Booth's algorithm for multiplying signed and unsigned integers. It begins with an introduction and history, noting that the algorithm was invented by Andrew Donald Booth in 1950. It then explains the key points of Booth's algorithm through a flow chart and examples. For unsigned integers, it uses fewer additions/subtractions than other methods by conditionally adding or subtracting the multiplicand. For signed integers, it first converts them to unsigned using 2's complement before applying the same process.

Subtractor

The document discusses binary subtraction and different types of binary subtractors. It describes half subtractors and full subtractors. A half subtractor is a basic circuit that can subtract two binary bits and outputs the difference and borrow. A full subtractor can subtract three bits by also considering the borrow from the previous stage. Truth tables and K-maps are used to derive the logic equations for difference and borrow outputs. Full subtractors are realized using basic gates by complementing one input to convert a full adder circuit into a full subtractor.

Combinational circuits

This document discusses combinational logic circuits such as adders, subtractors, multipliers, decoders, and multiplexers. It provides circuit diagrams and truth tables for half adders, full adders, half subtractors, full subtractors, decoders, and multiplexers. It also describes how to build binary adders and subtractors using these basic components and how multiplication of binary numbers is performed.

differential amplifier for electronic

Here are the steps to solve this:

1) VZ = VBE3 (zener voltage is equal to BJT base-emitter voltage)

2) Using KVL: -VZ + VBE3 + IE3RE = 0

3) Simplify: IE3RE = 0

4) IE3 is constant

Therefore, with a zener diode replacing R2, the current IE3 (and thus IT) remains constant regardless of load or temperature variations. The zener diode acts to stabilize the BJT base-emitter voltage, keeping the current constant.

Decoder Full Presentation

In which i describe all the features of decoder. All the functionalities describe with the circuits and truth tables. So download and learn more about decoder. Decoder Full Presentation.

Conversion of transfer function to canonical state variable models

Realization of transfer function into state variable models is needed even if the control system design based on frequency-domain design method.

In these cases the need arises for the purpose of transient response simulation.

But there is not much software for the numerical inversion of Laplace transform.

So one ways is to convert transfer function of the system to state variable description and numerically integrating the resulting differential equations rather than attempting to compute the inverse Laplace transform by numerical method.

adder and subtractor

1) The document discusses binary adders and subtractors, including half adders, full adders, and full subtractors. It provides truth tables and logic diagrams for each circuit.

2) A half adder adds two bits and produces a sum and carry output. A full adder adds three bits by taking two input bits and a carry bit as input.

3) A half subtractor and full subtractor are also discussed, which take inputs of minuend, subtrahend, and optionally a carry bit, and produce a difference and borrow output. Truth tables and logic diagrams are provided for the subtractor circuits.

Adder substracter

This document discusses digital adders and subtracters. It begins by explaining half adders and full adders, which are used to add binary numbers. It then discusses how to design multi-bit adders using full adders as building blocks. Different approaches for subtraction using full adders and full subtracters are also covered. The document provides circuit diagrams and truth tables to illustrate the designs of basic digital addition and subtraction components.

Combinational circuits

A combinational circuit is a logic circuit whose output is solely determined by the present input. It has no internal memory and its output depends only on the current inputs. A half adder is a basic combinational circuit that adds two single bits and produces a sum and carry output. A full adder adds three bits and produces a sum and carry like the half adder. Other combinational circuits discussed include half and full subtractors, decoders, encoders, and priority encoders.

Digital logic families

This document discusses different digital logic families and characteristics. It describes Resistor-Transistor Logic (RTL) which consists of resistors and transistors, with the emitters connected to ground and collectors tied through a resistor. Transistor-Transistor Logic (TTL) is also discussed, which depends solely on transistors. TTL uses multiple emitter transistors for inputs and a totem-pole output for high speed and low impedance. The document provides details on RTL and TTL gate operations.

Code conversions.pptx415.pptx

This document discusses different types of binary codes used to represent digital data, including weighted codes like BCD and non-weighted codes like Gray code. It provides details on code conversions between binary, Gray code, BCD, and excess-3 code. Conversion methods are described algorithmically and using logic gates. Truth tables are given to illustrate the bit patterns for conversions between BCD and excess-3 code.

Introduction to Counters

The document discusses synchronous and asynchronous counters. It defines a counter as a digital circuit that counts input pulses. Asynchronous counters have flip-flops that change state at different times since they do not share a common clock. Synchronous counters have all flip-flops change simultaneously due to a shared global clock, allowing them to operate at higher frequencies. The document provides examples of 2-bit, 3-bit, and 4-bit synchronous binary counters as well as a 4-bit synchronous decade counter along with their operations and timing diagrams.

Programmable logic array

It Defines what is Programmable Logic Array(PLA) also explains it in easy wording with syntax and Example...

It also cover what is Combinational & Sequential Logic Circuit and the Difference b/w these both. :)

Design half ,full Adder and Subtractor

This document describes the design and operation of half adders, full adders, half subtractors, and full subtractors. It defines each component, provides their truth tables, and shows how to design the logic circuits using K-maps. Half adders and subtractors perform addition and subtraction of two single bits, while full adders and subtractors handle three input bits, accounting for values carried in and out. The document also distinguishes between the components and their uses in digital logic systems.

Chapter 3: Simplification of Boolean Function

The document discusses minterms, maxterms, and their representation using shorthand notation in digital logic. It also covers the steps to obtain the shorthand notation for minterms and maxterms. Standard forms such as SOP and POS are introduced along with methods to simplify boolean functions into canonical forms using Karnaugh maps. The implementation of boolean functions using NAND and NOR gates is also described through examples.

7 Segment Decoder

A 7 segment display uses 7 LEDs to display decimal numbers from 0 to 9. It has either a common anode or common cathode configuration. A 7 segment decoder takes a 4-bit binary coded decimal input and outputs a 7-bit code that illuminates the correct LED segments to display that decimal number. For example, the input 0000 would output 1111110 to display the number 0. The decoder operates based on a truth table to map each input to the proper 7-bit segment output.

Relay interfacing with 8051

This document discusses interfacing a relay with an 8051 microcontroller. It defines a relay as a switch that can be controlled by a low-power signal to switch high-power circuits. It provides a diagram showing how an 8051 port pin can provide control signals to drive a transistor and energize a relay coil to open and close the main relay switch. It also gives examples of assembly and C code to output high and low signals from a port pin to toggle a relay on and off.

Neutralization Technique in EDC

Neutralization is a technique used to cancel feedback in bipolar junction transistors (BJTs) and field-effect transistors (FETs) that can cause instability over certain frequency ranges. This is done by introducing an additional feedback signal of equal amplitude but opposite phase to cancel the original feedback. In a neutralized transistor circuit, a negative capacitor is typically used to introduce this additional feedback signal. The Hazeltine neutralization method uses a variable capacitor connected from the bottom of an RF amplifier coil to the transistor base to neutralize the feedback from the collector-base capacitance. A modified version called Neutrodyne neutralization connects the capacitor to the secondary coil of the next stage for improved stability and insensitivity to supply voltage variations.

Combinational circuit

HALF ADDER &FULL ADDER

HALF& FULL SUBTRACTOR

1 BIT,2 BIT&4 BIT MAGNITUDE COMPARATOR

2:1,4:1& 8:1 MULTIPLEXER

1:2 DEMULTIPLEXER

PARALLEL ADDER

PARALLEL SUBTRACTOR

PARALLEL ADDER/SUBTRACTOR

Counters & time delay

The document discusses counters and time delays in microprocessors. It defines counters as circuits used to keep track of events and time delays as important for setting timing between events. It then provides details on designing counters and time delays using registers, loops, and instructions. It discusses different techniques for creating longer time delays using register pairs, nested loops, and inserting dummy instructions. Example programs are given to count hexadecimal numbers and generate pulse waveforms with delays. Common errors in programming counters and delays are also outlined.

Queue AS an ADT (Abstract Data Type)

A queue is a first-in, first-out (FIFO) data structure where elements are inserted at the rear and deleted from the front. There are two common implementations - a linear array implementation where the front and rear indices are incremented as elements are added/removed, and a circular array implementation where the indices wrap around to avoid unused space. Queues have applications in printing, scheduling, and call centers where requests are handled in the order received.

Emitter Coupled Logic (ECL)

This document is a presentation on emitter-coupled logic (ECL) given to a lecturer. It discusses the basics of ECL, including its differential amplifier configuration, lower time delay compared to other logic gates, use of negative voltage supply, and why it provides faster switching. It also covers some disadvantages of ECL like low fan-out and input-output voltage variations not matching. The presentation explains the basic circuit diagram and operation of ECL, showing how voltages are more negative for logic low and less negative for logic high. It further discusses how ECL provides faster speed due to a small voltage swing of 75mV when the emitter current is 95% or 5% of its operating current. The presentation addresses how

Tuned amplifire

Introduction

Band Pass Amplifiers

Series & Parallel Resonant Circuits & their Bandwidth

Analysis of Single Tuned Amplifiers

Analysis of Double Tuned Amplifiers

Primary & Secondary Tuned Amplifiers with BJT & FET

Merits and de-merits of Tuned Amplifiers

Race around and master slave flip flop

The Reason Why we use master slave JK flip flop instead of simple level triggered flip flop is Racing condition which can be successfully avoided using two SR latches fed with inverted clocks.

Adder & subtractor (Half adder, Full adder, Half subtractor, Full subtractor)

This slide tells you about Half adder, Full adder, Half subtractor, Full subtractor with its diagram, truth table.

Lect 1 unit 2.pdf

This document provides an overview of combinational logic circuits including half adders, full adders, half subtractors, full subtractors, multiplexers, demultiplexers, encoders, decoders, binary coded decimal adders, arithmetic logic units, and the differences between serial adders and parallel adders. Combinational logic circuits have outputs that are a function of the present inputs only. Common combinational logic elements and their applications are described.

More Related Content

What's hot

Decoder Full Presentation

In which i describe all the features of decoder. All the functionalities describe with the circuits and truth tables. So download and learn more about decoder. Decoder Full Presentation.

Conversion of transfer function to canonical state variable models

Realization of transfer function into state variable models is needed even if the control system design based on frequency-domain design method.

In these cases the need arises for the purpose of transient response simulation.

But there is not much software for the numerical inversion of Laplace transform.

So one ways is to convert transfer function of the system to state variable description and numerically integrating the resulting differential equations rather than attempting to compute the inverse Laplace transform by numerical method.

adder and subtractor

1) The document discusses binary adders and subtractors, including half adders, full adders, and full subtractors. It provides truth tables and logic diagrams for each circuit.

2) A half adder adds two bits and produces a sum and carry output. A full adder adds three bits by taking two input bits and a carry bit as input.

3) A half subtractor and full subtractor are also discussed, which take inputs of minuend, subtrahend, and optionally a carry bit, and produce a difference and borrow output. Truth tables and logic diagrams are provided for the subtractor circuits.

Adder substracter

This document discusses digital adders and subtracters. It begins by explaining half adders and full adders, which are used to add binary numbers. It then discusses how to design multi-bit adders using full adders as building blocks. Different approaches for subtraction using full adders and full subtracters are also covered. The document provides circuit diagrams and truth tables to illustrate the designs of basic digital addition and subtraction components.

Combinational circuits

A combinational circuit is a logic circuit whose output is solely determined by the present input. It has no internal memory and its output depends only on the current inputs. A half adder is a basic combinational circuit that adds two single bits and produces a sum and carry output. A full adder adds three bits and produces a sum and carry like the half adder. Other combinational circuits discussed include half and full subtractors, decoders, encoders, and priority encoders.

Digital logic families

This document discusses different digital logic families and characteristics. It describes Resistor-Transistor Logic (RTL) which consists of resistors and transistors, with the emitters connected to ground and collectors tied through a resistor. Transistor-Transistor Logic (TTL) is also discussed, which depends solely on transistors. TTL uses multiple emitter transistors for inputs and a totem-pole output for high speed and low impedance. The document provides details on RTL and TTL gate operations.

Code conversions.pptx415.pptx

This document discusses different types of binary codes used to represent digital data, including weighted codes like BCD and non-weighted codes like Gray code. It provides details on code conversions between binary, Gray code, BCD, and excess-3 code. Conversion methods are described algorithmically and using logic gates. Truth tables are given to illustrate the bit patterns for conversions between BCD and excess-3 code.

Introduction to Counters

The document discusses synchronous and asynchronous counters. It defines a counter as a digital circuit that counts input pulses. Asynchronous counters have flip-flops that change state at different times since they do not share a common clock. Synchronous counters have all flip-flops change simultaneously due to a shared global clock, allowing them to operate at higher frequencies. The document provides examples of 2-bit, 3-bit, and 4-bit synchronous binary counters as well as a 4-bit synchronous decade counter along with their operations and timing diagrams.

Programmable logic array

It Defines what is Programmable Logic Array(PLA) also explains it in easy wording with syntax and Example...

It also cover what is Combinational & Sequential Logic Circuit and the Difference b/w these both. :)

Design half ,full Adder and Subtractor

This document describes the design and operation of half adders, full adders, half subtractors, and full subtractors. It defines each component, provides their truth tables, and shows how to design the logic circuits using K-maps. Half adders and subtractors perform addition and subtraction of two single bits, while full adders and subtractors handle three input bits, accounting for values carried in and out. The document also distinguishes between the components and their uses in digital logic systems.

Chapter 3: Simplification of Boolean Function

The document discusses minterms, maxterms, and their representation using shorthand notation in digital logic. It also covers the steps to obtain the shorthand notation for minterms and maxterms. Standard forms such as SOP and POS are introduced along with methods to simplify boolean functions into canonical forms using Karnaugh maps. The implementation of boolean functions using NAND and NOR gates is also described through examples.

7 Segment Decoder

A 7 segment display uses 7 LEDs to display decimal numbers from 0 to 9. It has either a common anode or common cathode configuration. A 7 segment decoder takes a 4-bit binary coded decimal input and outputs a 7-bit code that illuminates the correct LED segments to display that decimal number. For example, the input 0000 would output 1111110 to display the number 0. The decoder operates based on a truth table to map each input to the proper 7-bit segment output.

Relay interfacing with 8051

This document discusses interfacing a relay with an 8051 microcontroller. It defines a relay as a switch that can be controlled by a low-power signal to switch high-power circuits. It provides a diagram showing how an 8051 port pin can provide control signals to drive a transistor and energize a relay coil to open and close the main relay switch. It also gives examples of assembly and C code to output high and low signals from a port pin to toggle a relay on and off.

Neutralization Technique in EDC

Neutralization is a technique used to cancel feedback in bipolar junction transistors (BJTs) and field-effect transistors (FETs) that can cause instability over certain frequency ranges. This is done by introducing an additional feedback signal of equal amplitude but opposite phase to cancel the original feedback. In a neutralized transistor circuit, a negative capacitor is typically used to introduce this additional feedback signal. The Hazeltine neutralization method uses a variable capacitor connected from the bottom of an RF amplifier coil to the transistor base to neutralize the feedback from the collector-base capacitance. A modified version called Neutrodyne neutralization connects the capacitor to the secondary coil of the next stage for improved stability and insensitivity to supply voltage variations.

Combinational circuit

HALF ADDER &FULL ADDER

HALF& FULL SUBTRACTOR

1 BIT,2 BIT&4 BIT MAGNITUDE COMPARATOR

2:1,4:1& 8:1 MULTIPLEXER

1:2 DEMULTIPLEXER

PARALLEL ADDER

PARALLEL SUBTRACTOR

PARALLEL ADDER/SUBTRACTOR

Counters & time delay

The document discusses counters and time delays in microprocessors. It defines counters as circuits used to keep track of events and time delays as important for setting timing between events. It then provides details on designing counters and time delays using registers, loops, and instructions. It discusses different techniques for creating longer time delays using register pairs, nested loops, and inserting dummy instructions. Example programs are given to count hexadecimal numbers and generate pulse waveforms with delays. Common errors in programming counters and delays are also outlined.

Queue AS an ADT (Abstract Data Type)

A queue is a first-in, first-out (FIFO) data structure where elements are inserted at the rear and deleted from the front. There are two common implementations - a linear array implementation where the front and rear indices are incremented as elements are added/removed, and a circular array implementation where the indices wrap around to avoid unused space. Queues have applications in printing, scheduling, and call centers where requests are handled in the order received.

Emitter Coupled Logic (ECL)

This document is a presentation on emitter-coupled logic (ECL) given to a lecturer. It discusses the basics of ECL, including its differential amplifier configuration, lower time delay compared to other logic gates, use of negative voltage supply, and why it provides faster switching. It also covers some disadvantages of ECL like low fan-out and input-output voltage variations not matching. The presentation explains the basic circuit diagram and operation of ECL, showing how voltages are more negative for logic low and less negative for logic high. It further discusses how ECL provides faster speed due to a small voltage swing of 75mV when the emitter current is 95% or 5% of its operating current. The presentation addresses how

Tuned amplifire

Introduction

Band Pass Amplifiers

Series & Parallel Resonant Circuits & their Bandwidth

Analysis of Single Tuned Amplifiers

Analysis of Double Tuned Amplifiers

Primary & Secondary Tuned Amplifiers with BJT & FET

Merits and de-merits of Tuned Amplifiers

Race around and master slave flip flop

The Reason Why we use master slave JK flip flop instead of simple level triggered flip flop is Racing condition which can be successfully avoided using two SR latches fed with inverted clocks.

What's hot (20)

Conversion of transfer function to canonical state variable models

Conversion of transfer function to canonical state variable models

Similar to binary decrementer.pdf

Adder & subtractor (Half adder, Full adder, Half subtractor, Full subtractor)

This slide tells you about Half adder, Full adder, Half subtractor, Full subtractor with its diagram, truth table.

Lect 1 unit 2.pdf

This document provides an overview of combinational logic circuits including half adders, full adders, half subtractors, full subtractors, multiplexers, demultiplexers, encoders, decoders, binary coded decimal adders, arithmetic logic units, and the differences between serial adders and parallel adders. Combinational logic circuits have outputs that are a function of the present inputs only. Common combinational logic elements and their applications are described.

Implementation and Simulation of Ieee 754 Single-Precision Floating Point Mul...

International Journal of Engineering and Science Invention (IJESI) is an international journal intended for professionals and researchers in all fields of computer science and electronics. IJESI publishes research articles and reviews within the whole field Engineering Science and Technology, new teaching methods, assessment, validation and the impact of new technologies and it will continue to provide information on the latest trends and developments in this ever-expanding subject. The publications of papers are selected through double peer reviewed to ensure originality, relevance, and readability. The articles published in our journal can be accessed online.

18CSC203J_COA_Unit 2 final.pptx

SIGNED 2’S COMPLEMENT SYSTEM: The standard system used to represent signed binary integers. A negative number is obtained by taking the 2's complement of its positive form. This allows for an easy way to perform addition and subtraction on signed binaries.

CARRY LOOKAHEAD ADDER: A fast adder circuit that calculates carry bits in advance to reduce wait time, improving speed over a ripple carry adder. It determines carry signals through a carry generate and propagate network to independently calculate carry and sum bits.

SHIFT-AND-ADD MULTIPLICATION: Implements binary multiplication by shifting and adding the multiplicand to itself the number of times indicated by

DLD Lecture No 20 Look Ahead Carry Generator, Binary Subtractors and BCD Add...

- A binary adder produces the sum of two binary numbers by connecting multiple full adders in cascade, with the output carry from each full adder feeding into the input carry of the next.

- In an n-bit adder, the carry propagation delay is 2n gate levels as the carry must propagate from the least to most significant bit. A carry lookahead generator reduces this delay by computing carry outputs in parallel rather than series.

- A binary subtractor implements subtraction by adding the number to the 2's complement of the subtrahend. An overflow in addition of signed numbers occurs if the carry into and out of the sign bit position differ.

Parallel Adder and Subtractor

1) The document discusses parallel adders and subtractors for n-bit binary numbers. It specifically examines a 4-bit parallel adder that uses full adders connected in cascade, with the carry output of one full adder connected to the next's carry input.

2) A 4-bit parallel subtractor is also examined, which takes the 2's complement of the number to be subtracted and adds it to the other number using a 4-bit parallel adder.

3) Carry propagation time is discussed, which is the time it takes the carry to ripple through all the full adders in the parallel adder from the least to most significant bit.

Comparison of Adders for optimized Exponent Addition circuit in IEEE754 Float...

This document compares different types of adders for calculating the addition of exponent bits when multiplying single and double precision floating point numbers according to the IEEE 754 standard. It describes parallel, carry skip, and carry select adders and analyzes their maximum combinational path delays. The document proposes using carry select and carry skip adders for exponent addition in floating point multiplication circuits, as they provide improved path delays over parallel adders. It also outlines the process for calculating the sign bit and adjusting the exponent value after multiplying the significands.

1d-HALF ADDER & FULL ADDER-PPT.pdf

The document discusses combinational logic circuits and different types of adders. It begins by defining combinational circuits and describing their characteristics. It then explains half adders and full adders. A half adder can add two bits but cannot account for carry bits from previous additions. A full adder can add two bits and an additional carry bit. The document discusses implementing full adders using logic gates. It also describes how multiple full adders can be used in parallel in a ripple carry adder or carry lookahead adder to add multiple bit numbers.

Binary Adders.pdf

The document describes various binary adders and subtractors used in digital circuits, including half adders, full adders, half subtractors, full subtractors, parallel adders, carry lookahead adders, and BCD adders. It explains their logic functions, truth tables, logic circuits, and implementations. It also provides examples of problems involving calculating propagation delays of ripple carry adders with different bit sizes and gate delays.

Arithmetic Micro Operations.pptx

The document discusses various arithmetic micro-operations including addition, subtraction, incrementing, and decrementing. It describes how addition and subtraction can be performed using binary adders and subtractors. A binary adder uses full adders to sum two binary numbers. A binary adder-subtractor uses exclusive-OR gates to select between addition and subtraction modes. Incrementing can be done using cascaded half-adders, with the least significant bit connected to a logic 1.

Digital Logic Design

This document provides information about Dr. Krishnanaik Vankdoth and his background and qualifications. It then discusses digital logic design topics like digital circuits, combinational logic, sequential circuits, logic gates, truth tables, adders, decoders, encoders, multiplexers and demultiplexers. Example circuits are provided and the functions of components like full adders, parallel adders, magnitude comparators are explained through diagrams and logic equations.

Logic gates

Combinational logic circuits produce outputs solely based on current inputs. They are made up of basic logic gates like NAND, NOR, and NOT connected together. A half adder adds two binary digits and produces a sum and carry output. A full adder adds three binary digits and produces a two-bit sum and carry output. A half subtractor subtracts one bit from another and produces a difference and borrow output, while a full subtractor subtracts three bits. Parallel adders use cascaded full adders to add multiple bits simultaneously, while serial adders add bits sequentially with the carry from the previous addition. BCD to 7-segment decoders take a 4-bit BCD number and output the correct segments to display

CSO PPT.pptx

Integer addition and subtraction can be performed using ripple carry adders and carry lookahead adders. Ripple carry adders consist of cascaded full adders where the carry output of each stage is input to the next. This results in a delay until the final output is reached. Carry lookahead adders reduce this propagation delay by computing carry bits in parallel rather than series. Shift-and-add multiplication works by shifting and adding the multiplicand to itself based on the bits of the multiplier, similar to the hand multiplication algorithm.

Cse lecture-4.2-c bit wise operators and expression

Prepared by-

Md. Abu Sayeed

Department of Computer Science & Engineering

Rajshahi Uiversity of Engineering & Technology

DLD Lecture No 19 Binary adders.pptx

This document discusses binary adders and subtractors. It begins by explaining half adders and full adders. A half adder adds two binary bits and produces a sum and carry output. A full adder adds three bits, including a carry bit from the previous stage. The document then explains how multiple full adders can be connected to form a binary adder to add multi-bit binary numbers. It notes that carry propagation, where the carry must ripple from least to most significant bit, leads to slow performance in binary adders. The document concludes by discussing techniques to reduce carry propagation delay.

Parallel Adder_Mul_Mag.pptx

This document discusses parallel adders and magnitude comparators. It describes how a parallel adder can be constructed using multiple full adder circuits connected in parallel to add binary numbers with more than one bit. It also provides logic diagrams and Verilog code examples for 4-bit parallel adders. The document further discusses carry look-ahead adders which can reduce the carry propagation delay time compared to ripple carry adders. Finally, it describes how a magnitude comparator works by comparing two binary numbers and determining if one is equal, less than, or greater than the other.

Hemanth143

The document discusses various logical and arithmetic operations in 8051 assembly language. It describes different types of instructions including data transfer, program branching, logical and arithmetic. Logical instructions include byte-level and bit-level logical operations like AND, OR, XOR. Arithmetic instructions cover operations like addition, subtraction, multiplication and division. Examples are provided to illustrate how these instructions work and how they affect the flag register.

CDS Fundamentals of digital communication system UNIT 1 AND 2.pdf

The document discusses various number systems including decimal, binary, hexadecimal and their conversions. It explains binary addition and subtraction using 2's complement. Binary coded decimal and gray codes are also covered. The last part discusses ASCII codes for alphanumeric representation. Key points discussed are:

- Decimal, binary and hexadecimal number systems and inter-conversions between them.

- Binary addition and subtraction using 2's complement.

- Binary coded decimal and gray codes for number representation.

- ASCII codes for alphanumeric representation in computers.

combinational_circuits

Combinational circuits are digital logic circuits whose outputs depend only on the current inputs. They have no internal stored state and include gates, encoders, decoders, multiplexers, and demultiplexers. The document describes several types of basic combinational circuits including half adders, full adders, parallel adders, subtractors, multiplexers, demultiplexers, decoders, and encoders. Their functions, block diagrams, truth tables, and circuit diagrams are provided as examples.

combinational_circuits

Combinational circuits are digital logic circuits whose outputs depend only on the current inputs. They have no internal stored state and include gates, encoders, decoders, multiplexers, and demultiplexers. The document describes several types of basic combinational circuits including half adders, full adders, n-bit parallel adders and subtractors, multiplexers, demultiplexers, decoders, encoders, and priority encoders. Their functions, block diagrams, and truth tables are explained.

Similar to binary decrementer.pdf (20)

Adder & subtractor (Half adder, Full adder, Half subtractor, Full subtractor)

Adder & subtractor (Half adder, Full adder, Half subtractor, Full subtractor)

Implementation and Simulation of Ieee 754 Single-Precision Floating Point Mul...

Implementation and Simulation of Ieee 754 Single-Precision Floating Point Mul...

DLD Lecture No 20 Look Ahead Carry Generator, Binary Subtractors and BCD Add...

DLD Lecture No 20 Look Ahead Carry Generator, Binary Subtractors and BCD Add...

Comparison of Adders for optimized Exponent Addition circuit in IEEE754 Float...

Comparison of Adders for optimized Exponent Addition circuit in IEEE754 Float...

Cse lecture-4.2-c bit wise operators and expression

Cse lecture-4.2-c bit wise operators and expression

CDS Fundamentals of digital communication system UNIT 1 AND 2.pdf

CDS Fundamentals of digital communication system UNIT 1 AND 2.pdf

Recently uploaded

ISPM 15 Heat Treated Wood Stamps and why your shipping must have one

For International shipping and maritime laws all wood must contain the ISPM 15 Stamp. Here is how and why.

New techniques for characterising damage in rock slopes.pdf

rock mass characterization and New techniques for characterising damage in rock slopes

22CYT12-Unit-V-E Waste and its Management.ppt

Introduction- e - waste – definition - sources of e-waste– hazardous substances in e-waste - effects of e-waste on environment and human health- need for e-waste management– e-waste handling rules - waste minimization techniques for managing e-waste – recycling of e-waste - disposal treatment methods of e- waste – mechanism of extraction of precious metal from leaching solution-global Scenario of E-waste – E-waste in India- case studies.

International Conference on NLP, Artificial Intelligence, Machine Learning an...

International Conference on NLP, Artificial Intelligence, Machine Learning and Applications (NLAIM 2024) offers a premier global platform for exchanging insights and findings in the theory, methodology, and applications of NLP, Artificial Intelligence, Machine Learning, and their applications. The conference seeks substantial contributions across all key domains of NLP, Artificial Intelligence, Machine Learning, and their practical applications, aiming to foster both theoretical advancements and real-world implementations. With a focus on facilitating collaboration between researchers and practitioners from academia and industry, the conference serves as a nexus for sharing the latest developments in the field.

Optimizing Gradle Builds - Gradle DPE Tour Berlin 2024

Sinan from the Delivery Hero mobile infrastructure engineering team shares a deep dive into performance acceleration with Gradle build cache optimizations. Sinan shares their journey into solving complex build-cache problems that affect Gradle builds. By understanding the challenges and solutions found in our journey, we aim to demonstrate the possibilities for faster builds. The case study reveals how overlapping outputs and cache misconfigurations led to significant increases in build times, especially as the project scaled up with numerous modules using Paparazzi tests. The journey from diagnosing to defeating cache issues offers invaluable lessons on maintaining cache integrity without sacrificing functionality.

5214-1693458878915-Unit 6 2023 to 2024 academic year assignment (AutoRecovere...

Bigdata of technology

学校原版美国波士顿大学毕业证学历学位证书原版一模一样

原版一模一样【微信:741003700 】【美国波士顿大学毕业证学历学位证书】【微信:741003700 】学位证,留信认证(真实可查,永久存档)offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原海外各大学 Bachelor Diploma degree, Master Degree Diploma

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微741003700

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

A review on techniques and modelling methodologies used for checking electrom...

The proper function of the integrated circuit (IC) in an inhibiting electromagnetic environment has always been a serious concern throughout the decades of revolution in the world of electronics, from disjunct devices to today’s integrated circuit technology, where billions of transistors are combined on a single chip. The automotive industry and smart vehicles in particular, are confronting design issues such as being prone to electromagnetic interference (EMI). Electronic control devices calculate incorrect outputs because of EMI and sensors give misleading values which can prove fatal in case of automotives. In this paper, the authors have non exhaustively tried to review research work concerned with the investigation of EMI in ICs and prediction of this EMI using various modelling methodologies and measurement setups.

Comparative analysis between traditional aquaponics and reconstructed aquapon...

The aquaponic system of planting is a method that does not require soil usage. It is a method that only needs water, fish, lava rocks (a substitute for soil), and plants. Aquaponic systems are sustainable and environmentally friendly. Its use not only helps to plant in small spaces but also helps reduce artificial chemical use and minimizes excess water use, as aquaponics consumes 90% less water than soil-based gardening. The study applied a descriptive and experimental design to assess and compare conventional and reconstructed aquaponic methods for reproducing tomatoes. The researchers created an observation checklist to determine the significant factors of the study. The study aims to determine the significant difference between traditional aquaponics and reconstructed aquaponics systems propagating tomatoes in terms of height, weight, girth, and number of fruits. The reconstructed aquaponics system’s higher growth yield results in a much more nourished crop than the traditional aquaponics system. It is superior in its number of fruits, height, weight, and girth measurement. Moreover, the reconstructed aquaponics system is proven to eliminate all the hindrances present in the traditional aquaponics system, which are overcrowding of fish, algae growth, pest problems, contaminated water, and dead fish.

ACEP Magazine edition 4th launched on 05.06.2024

This document provides information about the third edition of the magazine "Sthapatya" published by the Association of Civil Engineers (Practicing) Aurangabad. It includes messages from current and past presidents of ACEP, memories and photos from past ACEP events, information on life time achievement awards given by ACEP, and a technical article on concrete maintenance, repairs and strengthening. The document highlights activities of ACEP and provides a technical educational article for members.

2008 BUILDING CONSTRUCTION Illustrated - Ching Chapter 02 The Building.pdf

2008 BUILDING CONSTRUCTION Illustrated - Ching Chapter 02 The Building

Iron and Steel Technology Roadmap - Towards more sustainable steelmaking.pdf

Iron and Steel Technology towards Sustainable Steelmaking

官方认证美国密歇根州立大学毕业证学位证书原版一模一样

原版一模一样【微信:741003700 】【美国密歇根州立大学毕业证学位证书】【微信:741003700 】学位证,留信认证(真实可查,永久存档)offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原海外各大学 Bachelor Diploma degree, Master Degree Diploma

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微741003700

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

Presentation of IEEE Slovenia CIS (Computational Intelligence Society) Chapte...

Presentation of IEEE Slovenia CIS (Computational Intelligence Society) Chapte...University of Maribor

Slides from talk presenting:

Aleš Zamuda: Presentation of IEEE Slovenia CIS (Computational Intelligence Society) Chapter and Networking.

Presentation at IcETRAN 2024 session:

"Inter-Society Networking Panel GRSS/MTT-S/CIS

Panel Session: Promoting Connection and Cooperation"

IEEE Slovenia GRSS

IEEE Serbia and Montenegro MTT-S

IEEE Slovenia CIS

11TH INTERNATIONAL CONFERENCE ON ELECTRICAL, ELECTRONIC AND COMPUTING ENGINEERING

3-6 June 2024, Niš, SerbiaComputational Engineering IITH Presentation

This Presentation will give you a brief idea about what Computational Engineering at IIT Hyderabad has to offer.

IEEE Aerospace and Electronic Systems Society as a Graduate Student Member

IEEE Aerospace and Electronic Systems Society as a Graduate Student Member

Recently uploaded (20)

ISPM 15 Heat Treated Wood Stamps and why your shipping must have one

ISPM 15 Heat Treated Wood Stamps and why your shipping must have one

New techniques for characterising damage in rock slopes.pdf

New techniques for characterising damage in rock slopes.pdf

International Conference on NLP, Artificial Intelligence, Machine Learning an...

International Conference on NLP, Artificial Intelligence, Machine Learning an...

Optimizing Gradle Builds - Gradle DPE Tour Berlin 2024

Optimizing Gradle Builds - Gradle DPE Tour Berlin 2024

5214-1693458878915-Unit 6 2023 to 2024 academic year assignment (AutoRecovere...

5214-1693458878915-Unit 6 2023 to 2024 academic year assignment (AutoRecovere...

Engineering Drawings Lecture Detail Drawings 2014.pdf

Engineering Drawings Lecture Detail Drawings 2014.pdf

A review on techniques and modelling methodologies used for checking electrom...

A review on techniques and modelling methodologies used for checking electrom...

Comparative analysis between traditional aquaponics and reconstructed aquapon...

Comparative analysis between traditional aquaponics and reconstructed aquapon...

2008 BUILDING CONSTRUCTION Illustrated - Ching Chapter 02 The Building.pdf

2008 BUILDING CONSTRUCTION Illustrated - Ching Chapter 02 The Building.pdf

Iron and Steel Technology Roadmap - Towards more sustainable steelmaking.pdf

Iron and Steel Technology Roadmap - Towards more sustainable steelmaking.pdf

Presentation of IEEE Slovenia CIS (Computational Intelligence Society) Chapte...

Presentation of IEEE Slovenia CIS (Computational Intelligence Society) Chapte...

IEEE Aerospace and Electronic Systems Society as a Graduate Student Member

IEEE Aerospace and Electronic Systems Society as a Graduate Student Member

binary decrementer.pdf

- 1. 4 Bit Binary Decrementer What is 4 Bit Binary Decrementer ? It subtracts 1 binary value from the existing binary value stored in the register or in other words we can simply say that it decreases the existing value stored in the register by 1. For any n- bit binary decrementer, ‘n’ refers to the storage capacity of the register which needs to be decremented by 1. So we require ‘n’ number of full adders. Thus, in case of 4 bit binary decrementer we require 4 full adders. Working: It consists of 4 full adders, connected one after the other. Each full adder has 3 inputs (carry input, 1, A) and 2 outputs (carry output and S) A full adder basic consist of 2 half adders and an OR gate. The carry(C) from previous full adder is propagated to the next full adder. So carry output from one full adder becomes one of the three input of the next full adder. It follows the concept of 2’s complement, so we take 1 as input in all 4 full adder as seen from the above diagram. So we add 1111 in order to subtract 1.

- 2. Reason for adding 1111: This is because our main motive is to subtract 1 which in 4 bit representation is 0001 Representing it in 1’s complement will give: 1110 Representing it in 2’s complement (adding 1 to 1’s complement) will give: 1111 This is the reason why input 1111 is given to get a decremented output in 4 bit binary decrementer.