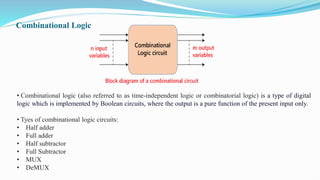

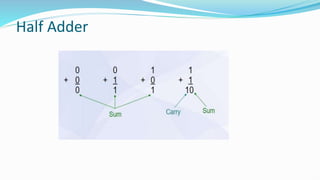

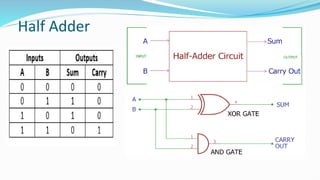

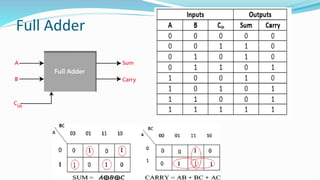

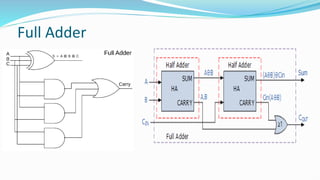

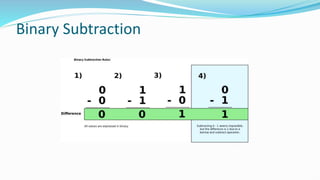

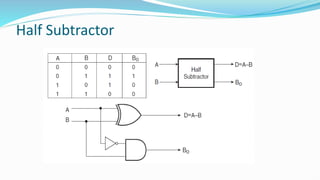

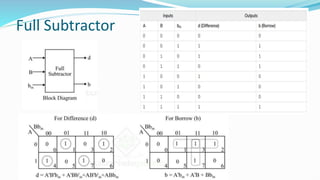

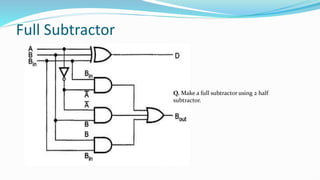

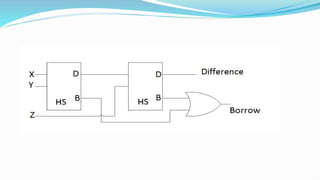

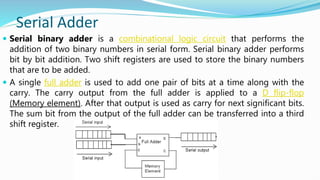

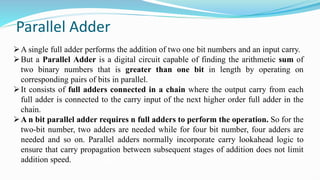

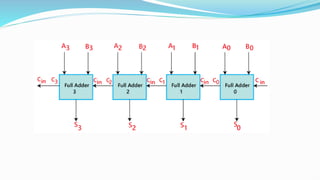

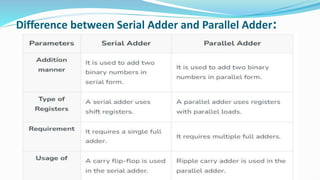

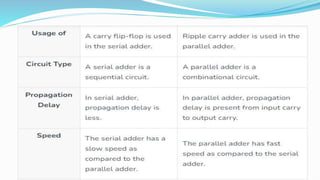

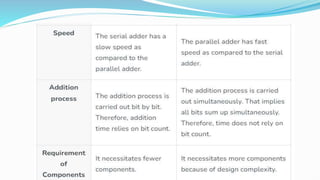

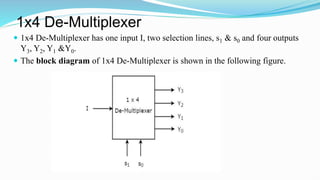

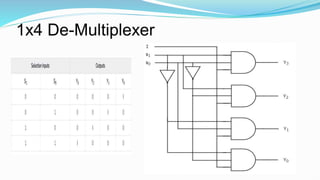

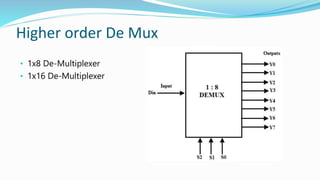

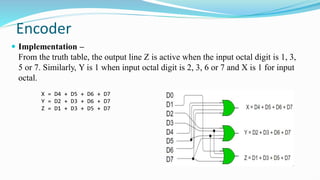

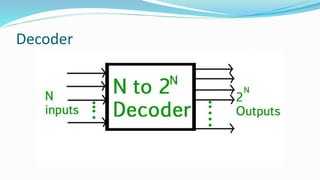

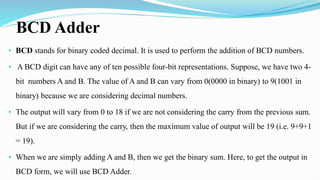

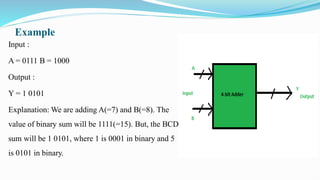

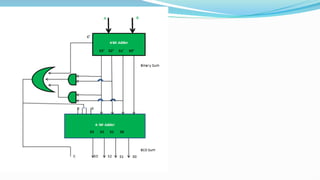

This document provides an overview of combinational logic circuits including half adders, full adders, half subtractors, full subtractors, multiplexers, demultiplexers, encoders, decoders, binary coded decimal adders, arithmetic logic units, and the differences between serial adders and parallel adders. Combinational logic circuits have outputs that are a function of the present inputs only. Common combinational logic elements and their applications are described.