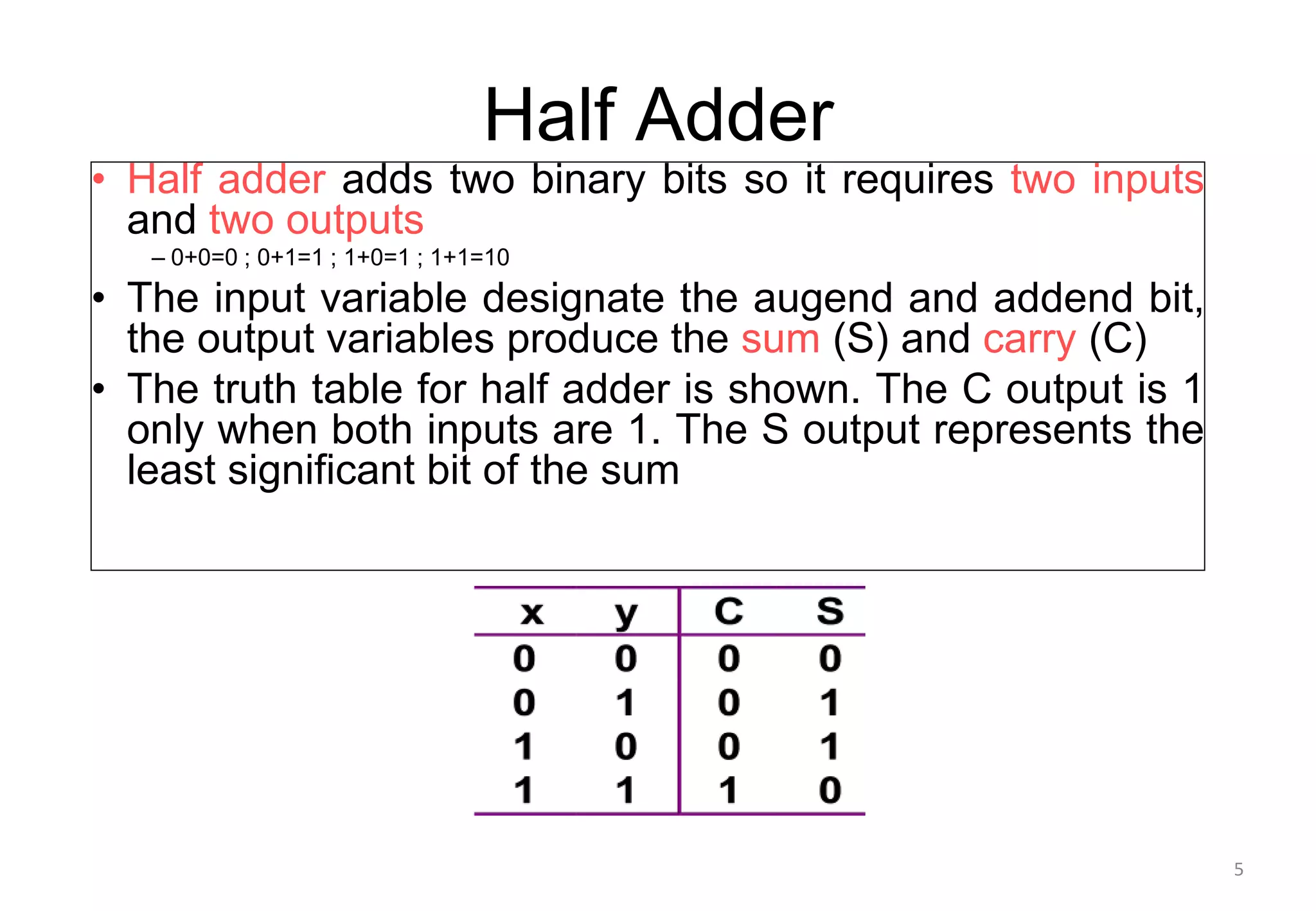

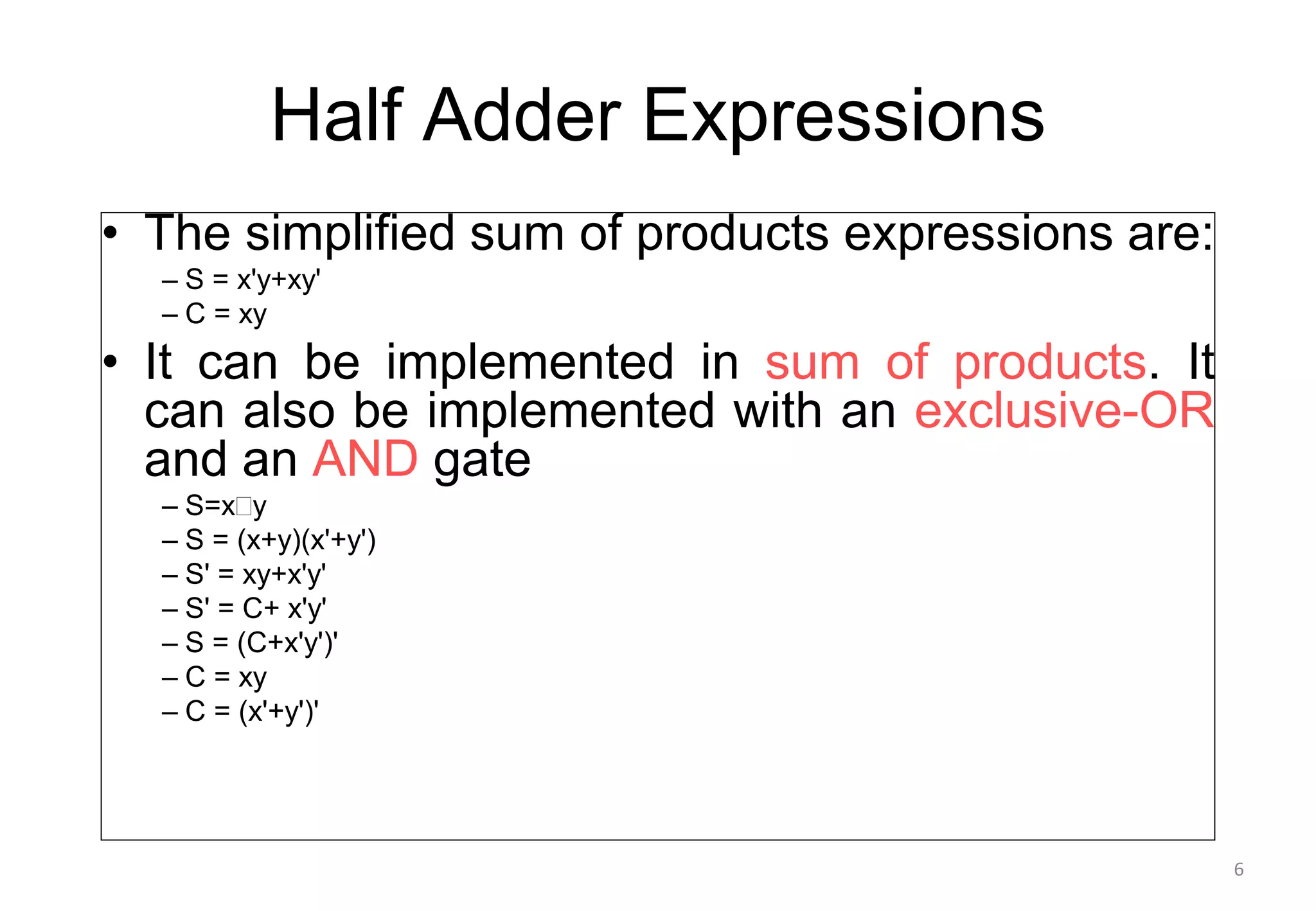

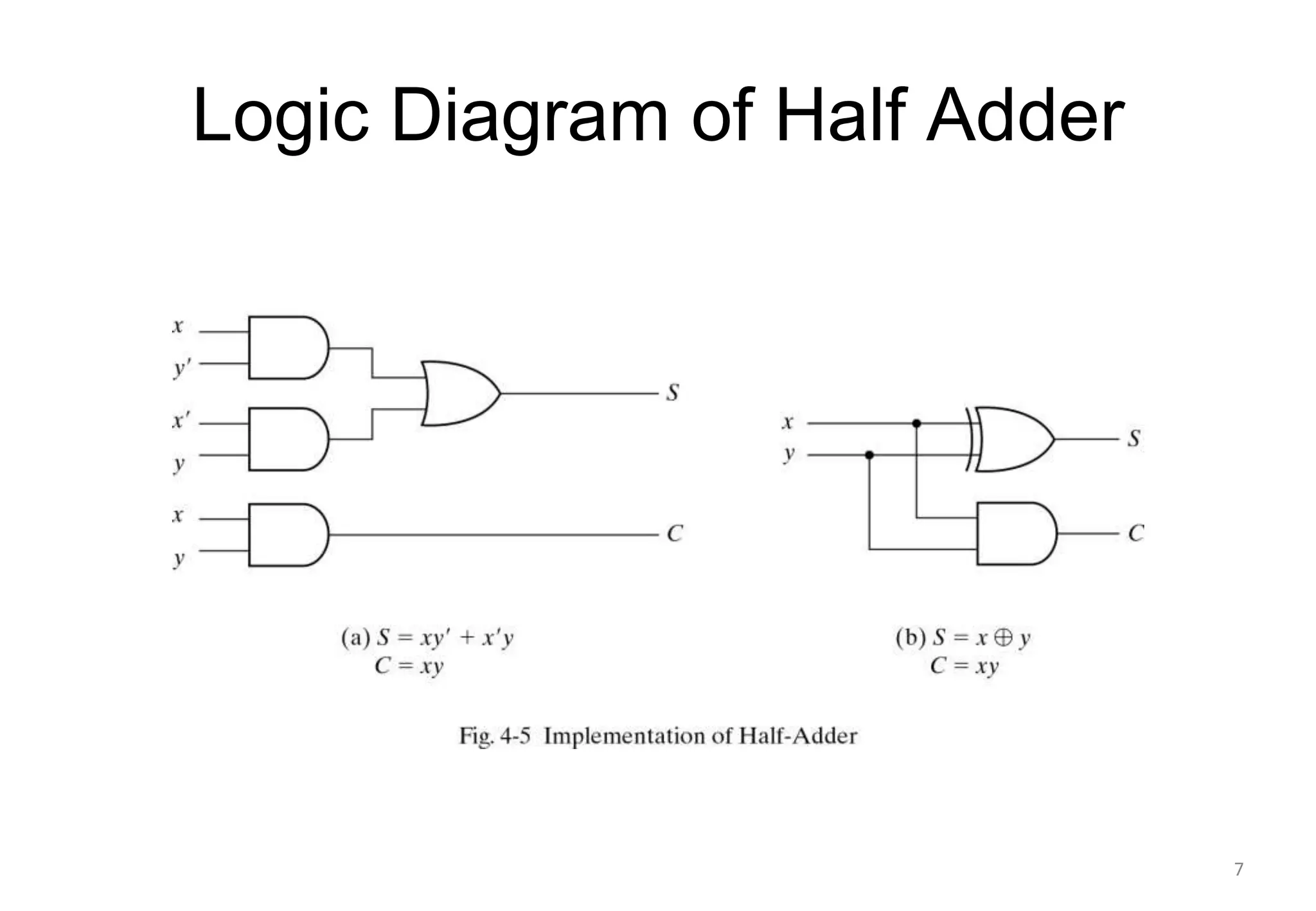

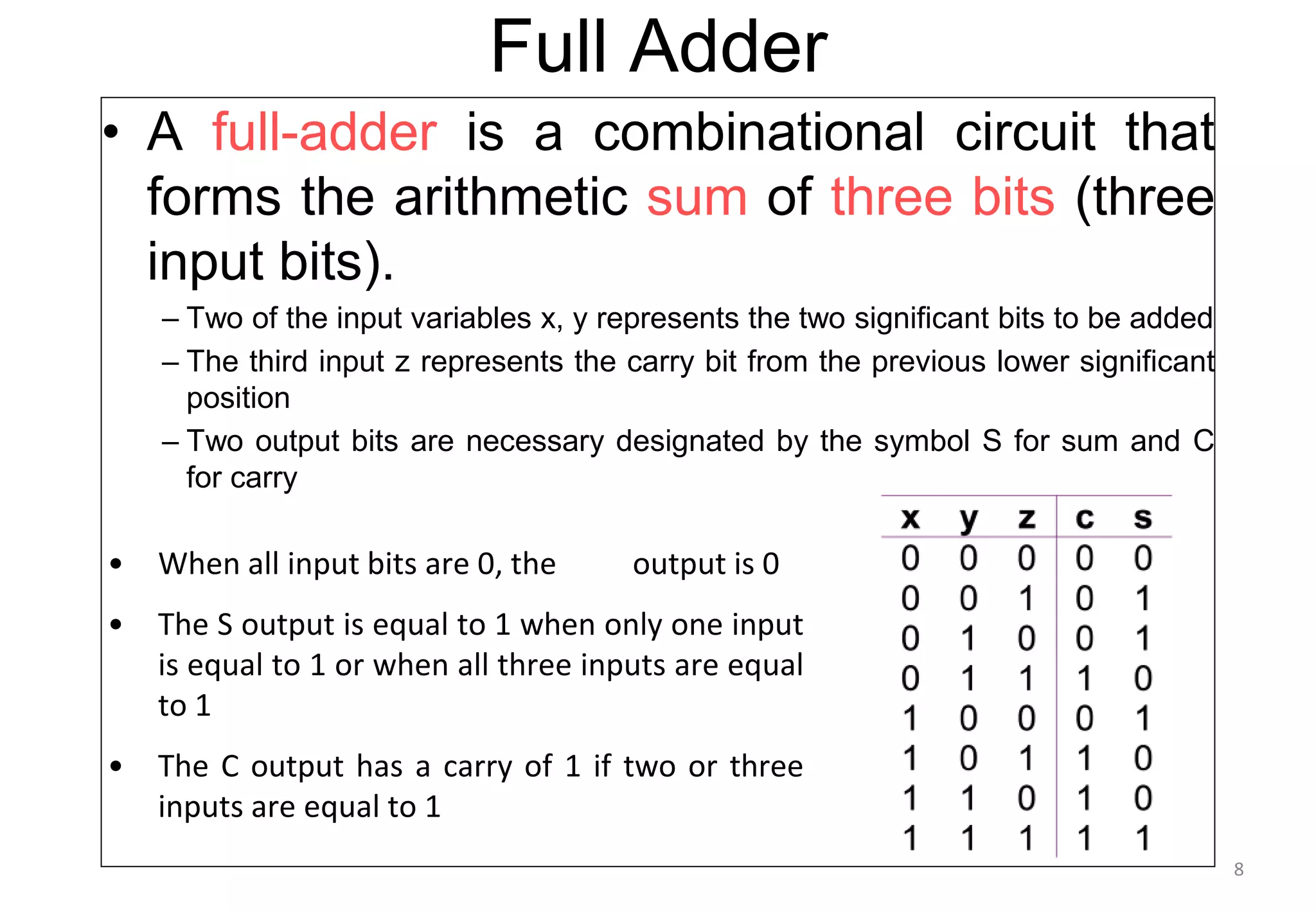

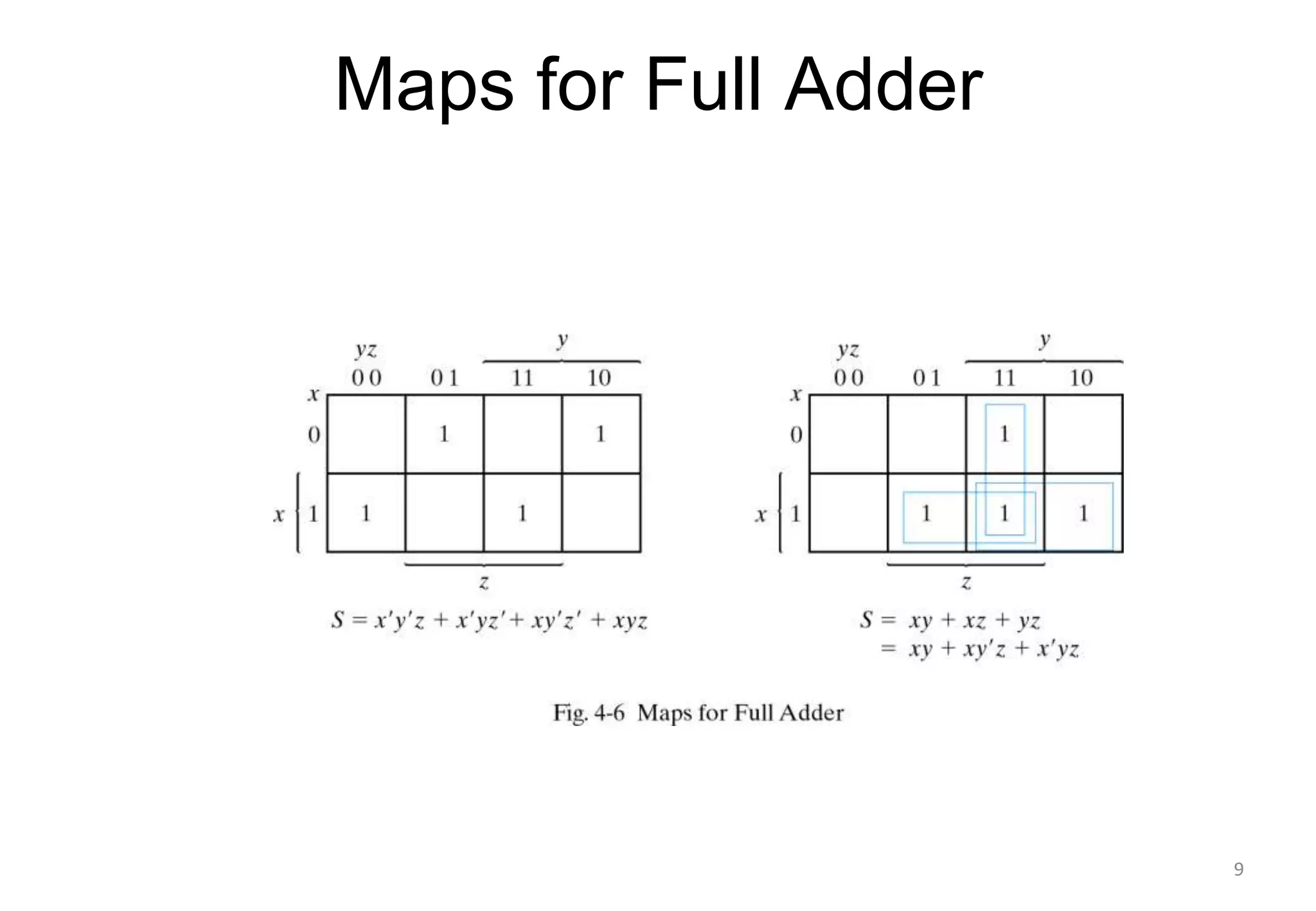

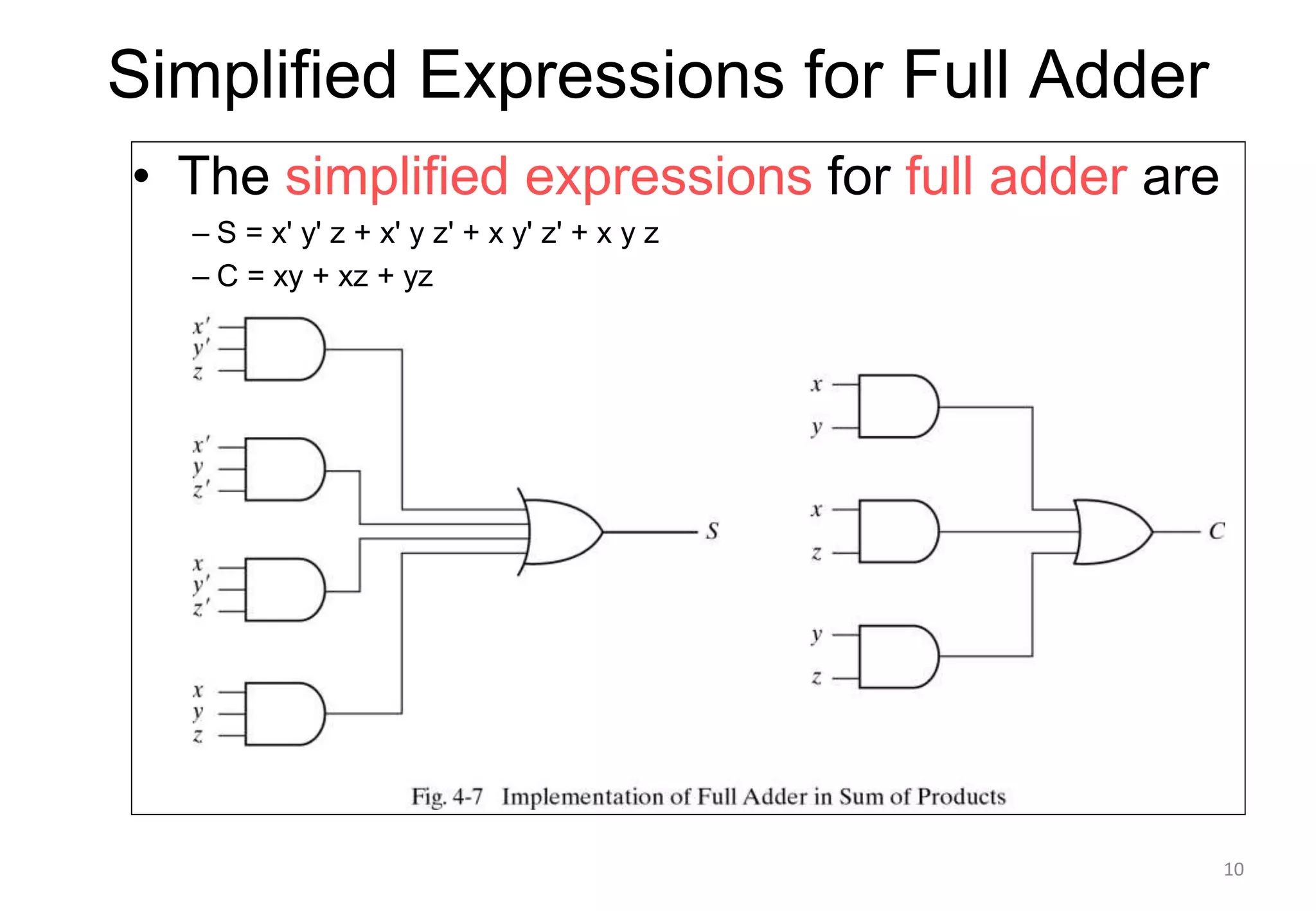

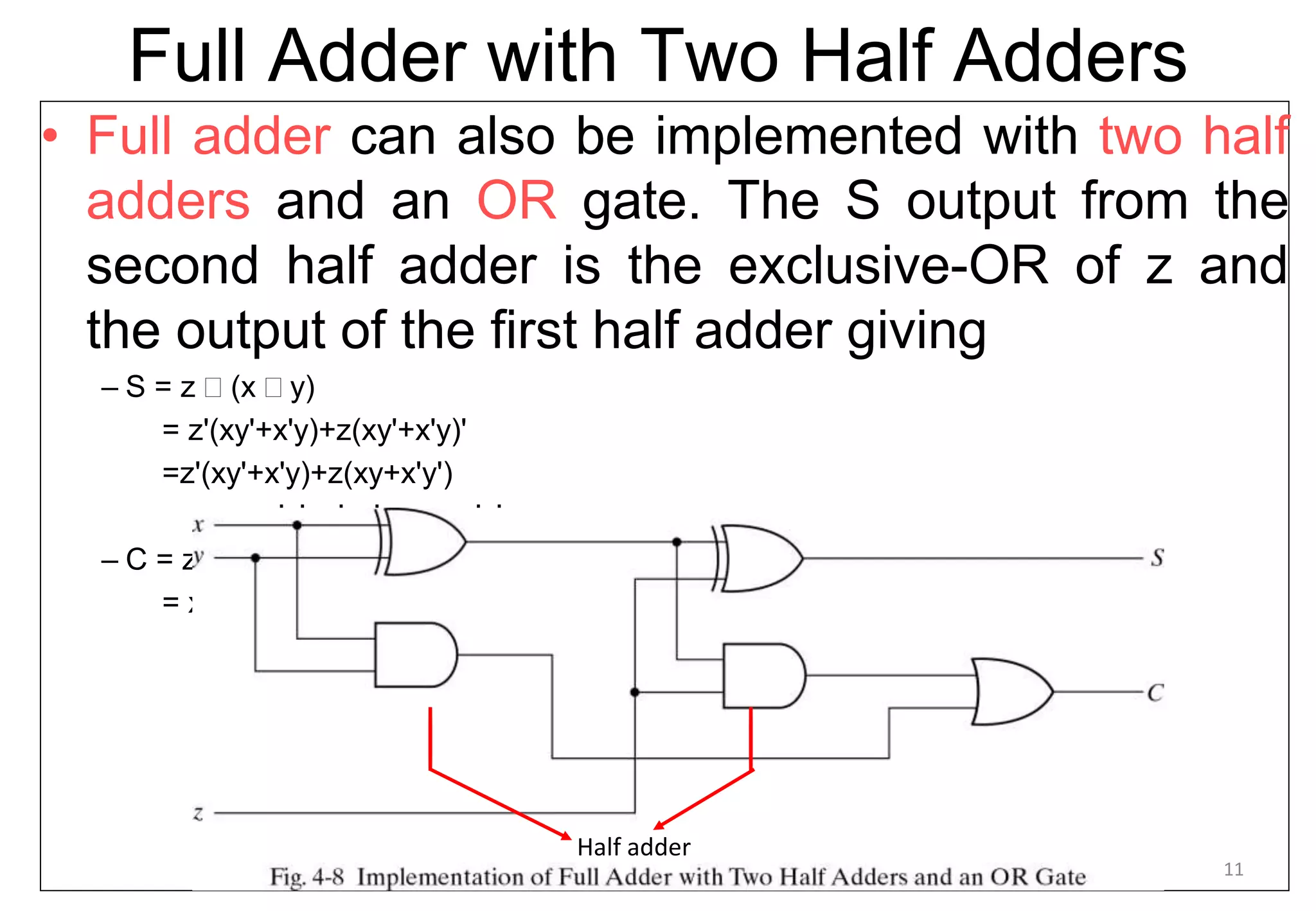

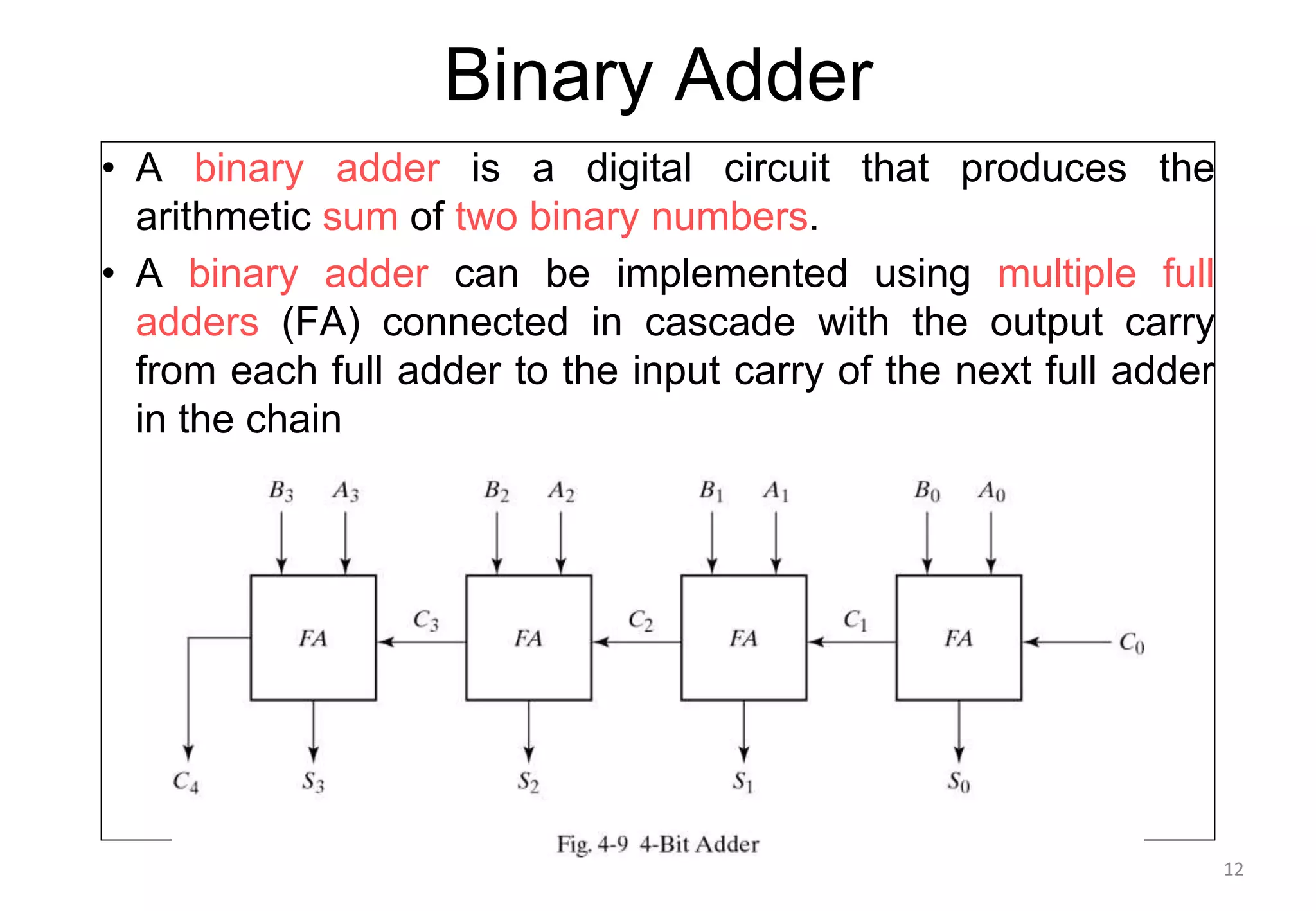

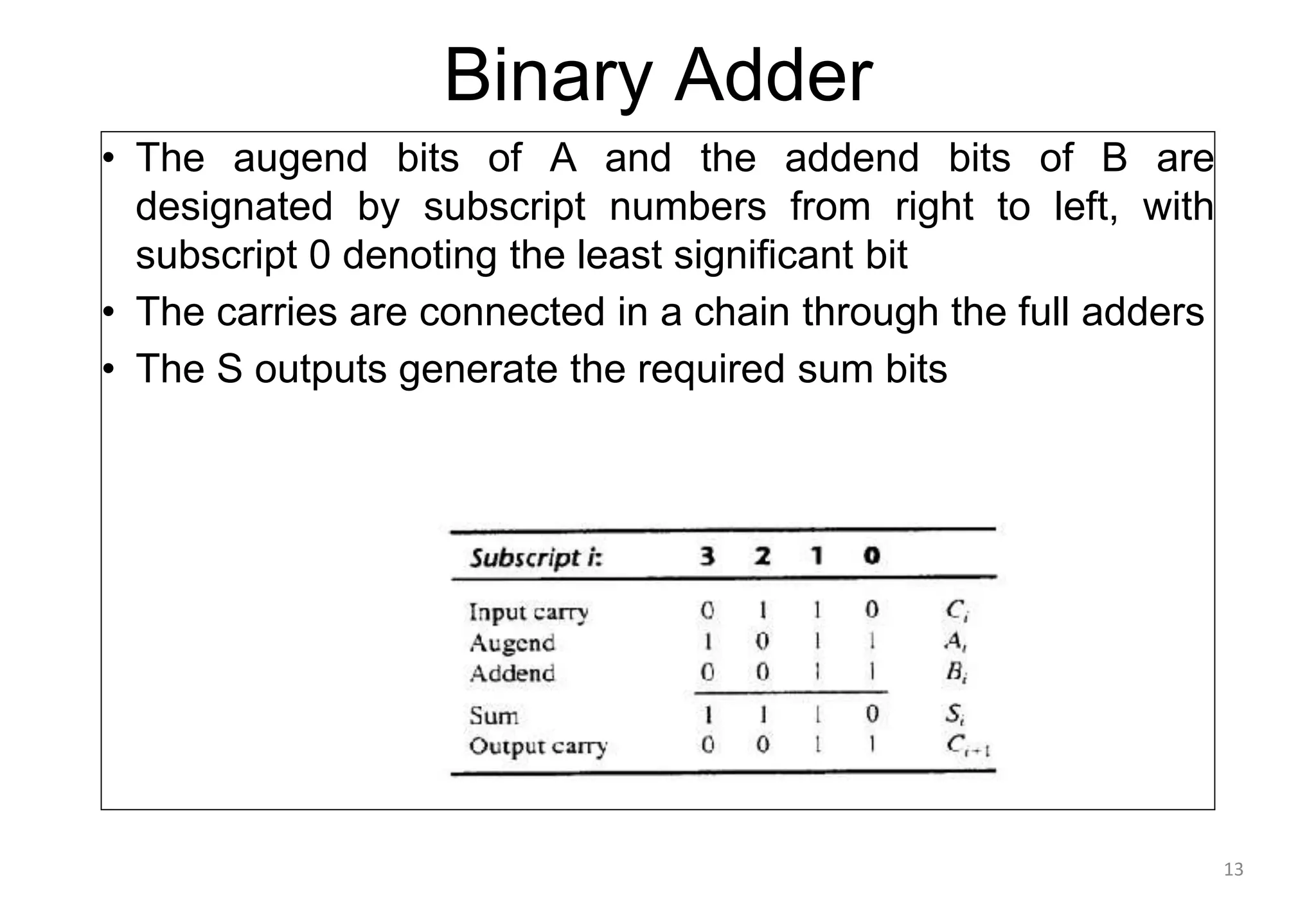

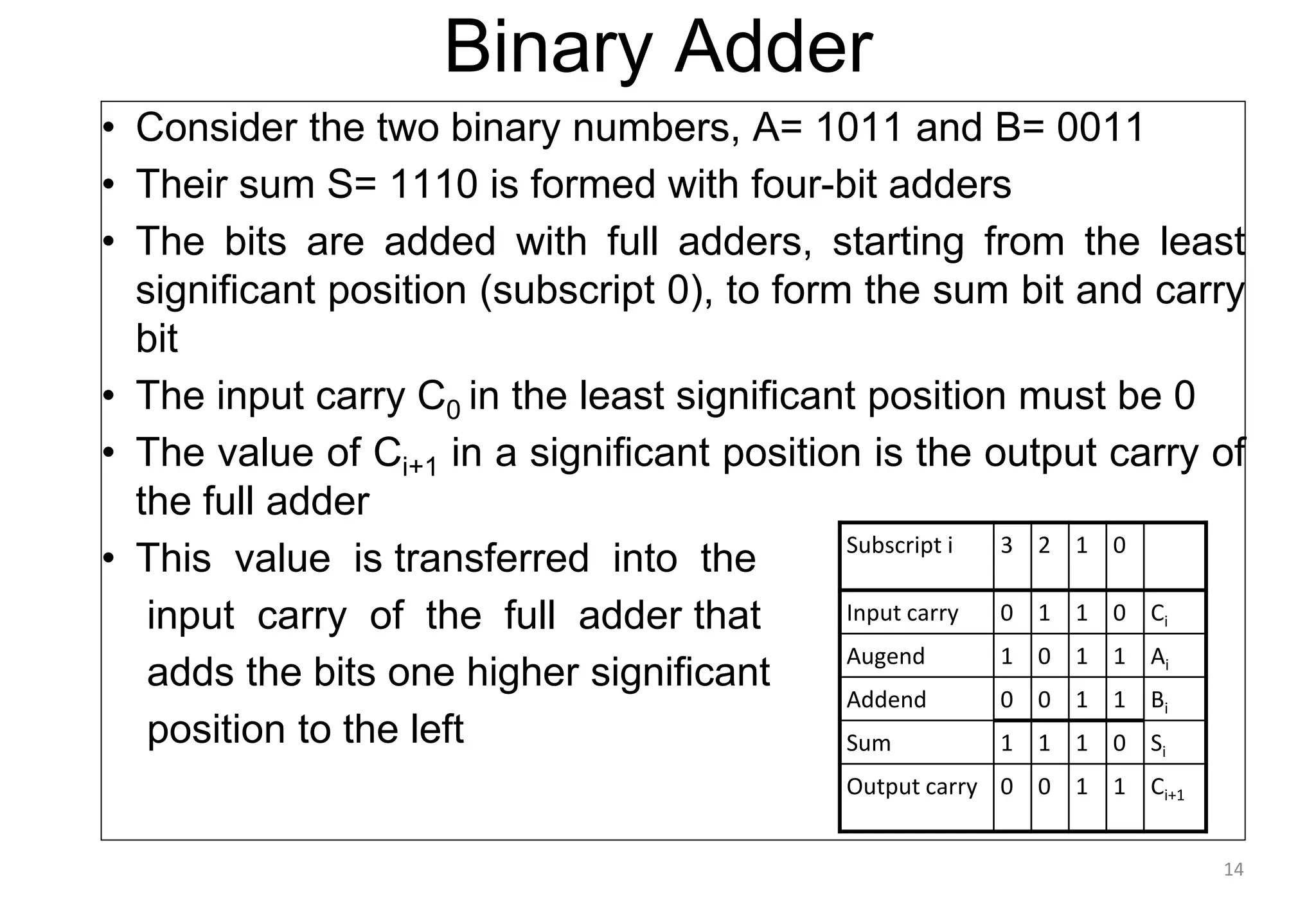

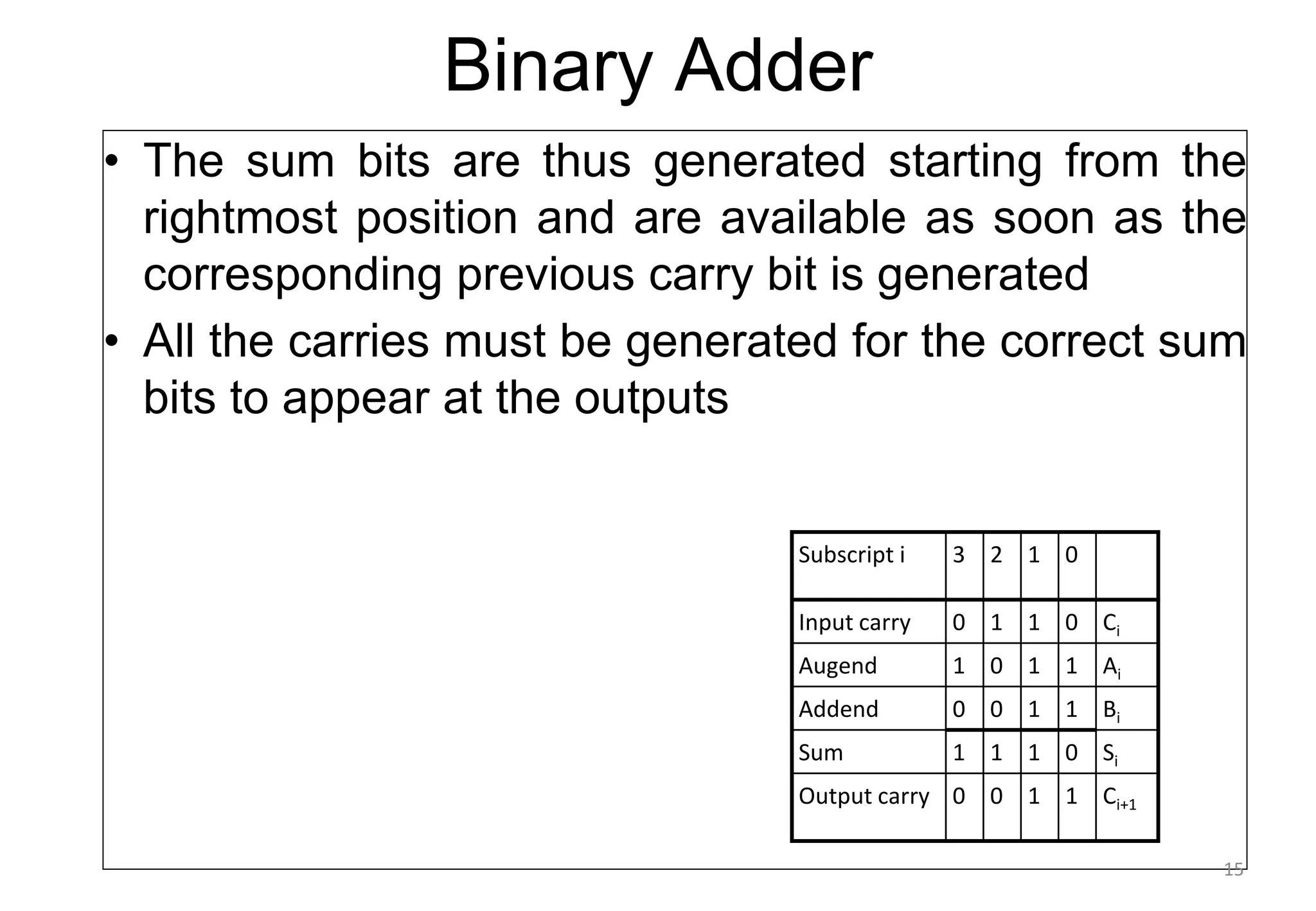

This document discusses binary adders and subtractors. It begins by explaining half adders and full adders. A half adder adds two binary bits and produces a sum and carry output. A full adder adds three bits, including a carry bit from the previous stage. The document then explains how multiple full adders can be connected to form a binary adder to add multi-bit binary numbers. It notes that carry propagation, where the carry must ripple from least to most significant bit, leads to slow performance in binary adders. The document concludes by discussing techniques to reduce carry propagation delay.