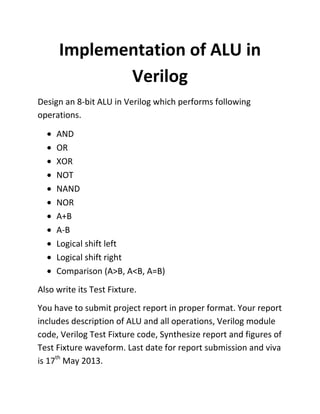

The document describes designing an 8-bit ALU in Verilog that performs logic and arithmetic operations. It includes the Verilog module code for the ALU and a test fixture. Students must submit a project report by May 17th that describes the ALU operations, includes the Verilog code and test results, and discusses the synthesis report.

![// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module Eight_bit_alu(A,B,operation,out,flag_greater,flag_less,flag_equal);

output [7:0]out;

input[7:0]A,B;

input[3:0]operation;

output flag_greater,flag_less,flag_equal;

reg flag_greater,flag_less,flag_equal;

reg [7:0] out;

always @(operation or A or B)

begin

if(operation==4'b0000)

out=A+B;

else if(operation==4'b0001)

out=A-B;

else if(operation==4'b0010)

out=A&B;

else if(operation==4'b0011)

out=A|B;

else if(operation==4'b0100)

out=A^B;

else if(operation==4'b0101)

out=~A;](https://image.slidesharecdn.com/aludescription1-130616094909-phpapp01/85/Alu-description-1-3-320.jpg)

![reg [7:0] A;

reg [7:0] B;

reg [3:0] operation;

// Outputs

wire [7:0] out;

wire flag_greater;

wire flag_less;

wire flag_equal;

// Instantiate the Unit Under Test (UUT)

Eight_bit_alu uut (

.A(A),

.B(B),

.operation(operation),

.out(out),

.flag_greater(flag_greater),

.flag_less(flag_less),

.flag_equal(flag_equal)

);

initial begin

// Initialize Inputs

A = 1;

B = 0;

operation = 0;

// Wait 100 ns for global reset to finish

#100;](https://image.slidesharecdn.com/aludescription1-130616094909-phpapp01/85/Alu-description-1-6-320.jpg)