The document is a comprehensive overview of digital system design using Verilog, covering topics such as delays, compilation, simulation, synthesis, constants, arrays, and testing methodologies. It explains key concepts in Verilog like inertial and transport delays, event-driven simulation, the event queue, and the use of test benches for validating designs. Additionally, it includes examples and best practices for syntax, assignment, and the creation of functions and tasks in Verilog.

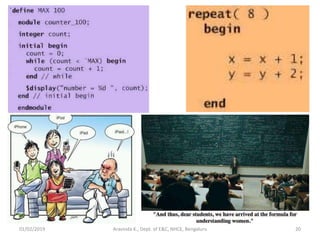

![01/02/2019 15Aravinda K., Dept. of E&C, NHCE, Bengaluru

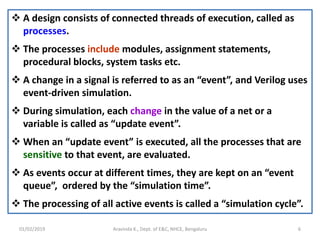

Declaration of constants in Verilog

There are three methods to define constant values: i) using the

compiler directive `define, ii) using the keyword parameter, iii) using

the keyword localparam.

Note: Constants defined using parameter can be changed during

module instantiation. For the constants which should not be changed,

localparam is used to define them.

i) `define constant_name constant_value

e.g., `define wordsize 16

reg [1: `wordsize] data;

Here, data is declared to be a reg of width wordsize.

ii) parameter constant_name = constant_value;

e.g., parameter msb = 15;

parameter [31:0] decim = 1’b1;

iii) localparam constant_name = constant_value;

e.g., localparameter pi = 3.1416;](https://image.slidesharecdn.com/sdhdlece43-m2-200302071339/85/System-design-using-HDL-Module-2-15-320.jpg)

![01/02/2019 16Aravinda K., Dept. of E&C, NHCE, Bengaluru

Usage of arrays in Verilog

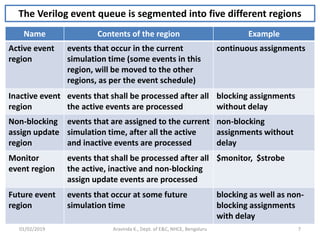

Digital VLSI circuits consist of repeated use of similar structures,

and hence arrays can be utilized to model such structures, along with

the required array bounds.

Declaration

reg [0:7] regA; // an 8-bit register.

reg regB [0:7]; // an array of eight 1-bit registers.

wire wire_arrayA [5:0]; // an array of six wires.

integer intA [1:64]; // an array of sixty four integers.

reg [7:0] regC [15:0]; // an array of sixteen 8-bit registers.

Initialization

regA = 8’b10010110; // 8-bit register’s contents.

regC[15] = 8’b10100101; // 16th register’s 8-bit contents.

.

.

.

regC[0] = 8’b10010110; // 1st register’s 8-bit contents.](https://image.slidesharecdn.com/sdhdlece43-m2-200302071339/85/System-design-using-HDL-Module-2-16-320.jpg)

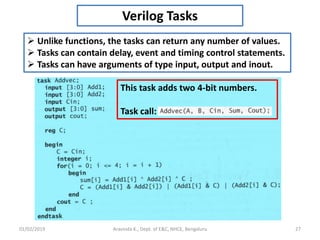

![01/02/2019 17Aravinda K., Dept. of E&C, NHCE, Bengaluru

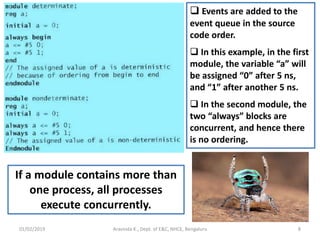

Matrices

Matrices can be declared as multidimensional arrays. A matrix of

size (4X3) with 8-bit elements is declared and initialized as follows –

reg [7:0] matrixA [0:3][0:2] = {{4, 2, 9},

{1, 3, 4},

{8, 6, 7},

{5, 9, 2}};

The array element referenced as matrixA[2][1] implies the element

that is in 3rd row and 2nd column, and it contains the value 6.

The arrays, along with the parameters, can be used to construct

look-up tables (LUT), which can be used to create combinational

circuits using ROM or LUT.](https://image.slidesharecdn.com/sdhdlece43-m2-200302071339/85/System-design-using-HDL-Module-2-17-320.jpg)

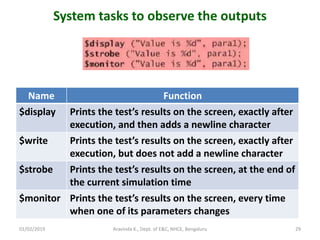

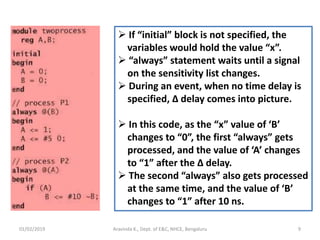

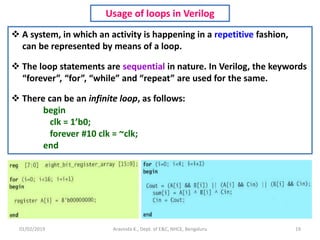

![01/02/2019 18Aravinda K., Dept. of E&C, NHCE, Bengaluru

Input

(LUT Address)

Output

(LUT Data)

0000 00001

0001 00010

0010 00100

0011 00111

0100 01000

0101 01011

0110 01101

0111 01110

1000 10000

1001 10011

1010 10101

1011 10110

1100 11001

1101 11010

1110 11100

1111 11111

Example: odd parity representation for 4-bit numbers

Verilog code for the example

module parity_gen(X,Y);

input [3:0] X;

output [4:0] Y;

wire paritybit;

parameter [0:15] onebit = {1’b1, 1’b0, 1’b0, 1’b1,

1’b0, 1’b1, 1’b1, 1’b0, 1’b0, 1’b1, 1’b1, 1’b0, 1’b1,

1’b0, 1’b0, 1’b1};

assign paritybit = onebit[X];

assign Y = {X, paritybit};

Endmodule

As the first 4 bits of the output are

identical to the input, it is not necessary to

store all the 5-bit 16 numbers in the LUT.

Therefore, only the 16 parity bits can be

stored, and the particular parity bit can be

concatenated with the respective input bit.](https://image.slidesharecdn.com/sdhdlece43-m2-200302071339/85/System-design-using-HDL-Module-2-18-320.jpg)

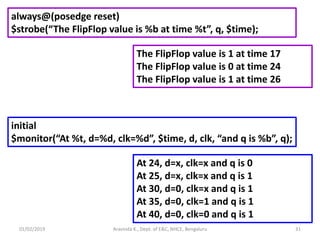

![01/02/2019 Aravinda K., Dept. of E&C, NHCE, Bengaluru 24

Verilog Functions

A function returns only a single value, and a function cannot contain delays.

Functions and tasks can be defined in the module that they will be used in.

A function call in the program file can happen just like an expression.

A function can call other functions, but the function cannot call tasks.

If a function or a task is defined as a separate file, then the compiler

directive `include has to be used in the program file.

Example-1: Write a function for generating an even parity bit for a 4-bit number.

function [4:0] even_parity;

input [3:0] A;

reg temp;

begin

temp = A[0]^A[1]^A[2]^A[3];

even_parity = {A, temp};

end

endfunction

module even_test(Z);

output reg [4:0] Z;

reg [3:0] INP;

initial

begin

INP = 4’b0101;

Z = even_parity(INP);

end

endmodule](https://image.slidesharecdn.com/sdhdlece43-m2-200302071339/85/System-design-using-HDL-Module-2-24-320.jpg)

![01/02/2019 Aravinda K., Dept. of E&C, NHCE, Bengaluru 25

Example-2:

Write a function

to add two

4-bit numbers

function [4:0] add4;

input [3:0] A,B;

input cin;

reg [4:0] sum;

reg cout;

begin

integer i;

for (i=0; i<=3; i=i+1)

begin

cout = (A[i] & B[i]) | (B[i] & cin) | (A[i] & cin);

sum[i] = A[i] ^ B[i] ^ cin;

cin = cout;

end

sum[4] = cout;

add4 = sum;

end

endfunction

Function call: i) Z <= add4(X, Y, 0); // for adding Y to Z

ii) Z <= add4(X, ~Y, 1); // for subtracting Y from Z, ignoring Z[4]](https://image.slidesharecdn.com/sdhdlece43-m2-200302071339/85/System-design-using-HDL-Module-2-25-320.jpg)

![01/02/2019 Aravinda K., Dept. of E&C, NHCE, Bengaluru 26

Example-3:

Write a program which

computes the square of a 4-bit

number, by using a function

module squares_test (clk);

input clk;

reg [3:0] temp;

reg [7:0] answer;

function [7:0] squares;

input [3:0] number;

begin

squares = number * number;

end

endfunction

initial

begin

temp = 4’b0011;

end

always @(posedge clk)

begin

answer = squares (temp)

end

endmodule

A function must have at least

one input argument.

The function cannot have output

or inout arguments.

Recursive functions must be

declared as automatic.](https://image.slidesharecdn.com/sdhdlece43-m2-200302071339/85/System-design-using-HDL-Module-2-26-320.jpg)