Embed presentation

Downloaded 25 times

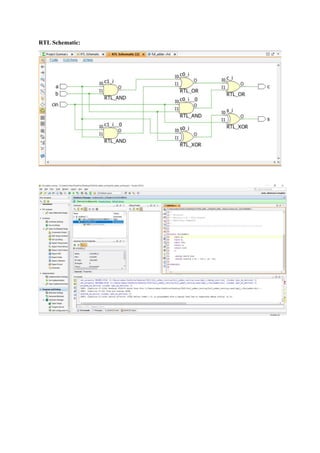

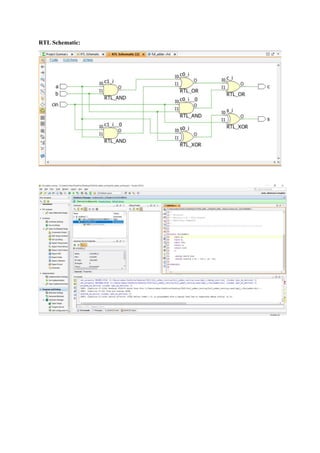

This document describes two different models for a full adder circuit - a dataflow model and a gate level model. The dataflow model uses assign statements to directly define the sum (s) and carry out (cout) outputs in terms of the inputs (a, b, cin). The gate level model builds the full adder using lower level logic gates like xor, and, or connected via internal wires to compute the sum and carry outputs.