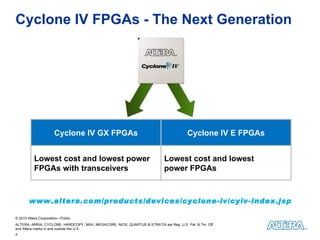

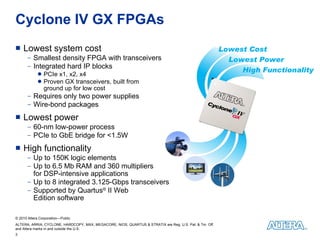

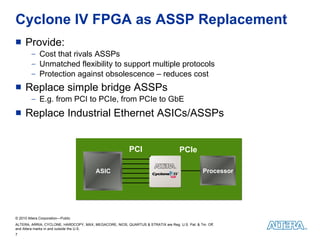

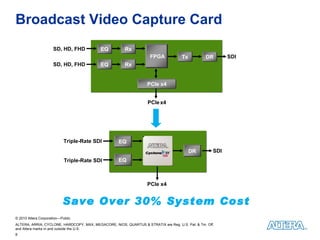

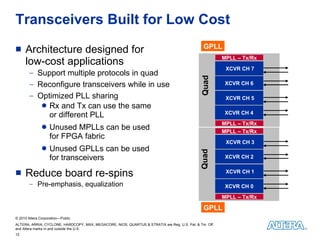

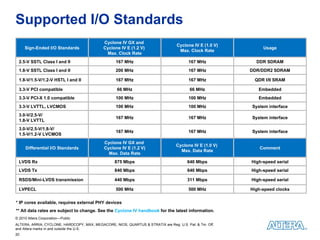

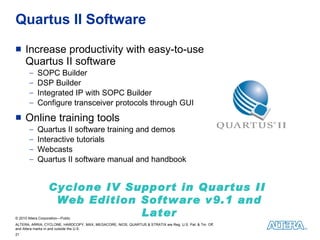

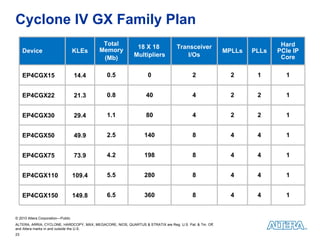

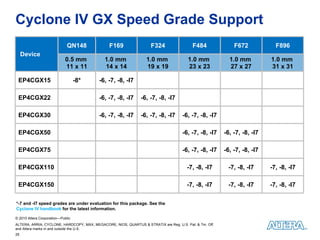

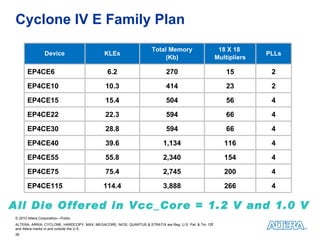

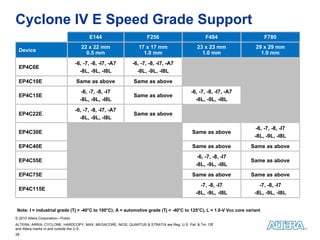

The document provides detailed information on the Cyclone IV FPGA family by Altera, highlighting their features such as low cost, low power consumption, and integrated transceivers designed for various applications. It outlines the specifications of different models within the Cyclone IV GX and E series, including logic element counts, memory capacity, and support for various protocols like PCIe and Gigabit Ethernet. Additionally, it emphasizes the benefits of these FPGAs in reducing overall system costs and enhancing design flexibility.