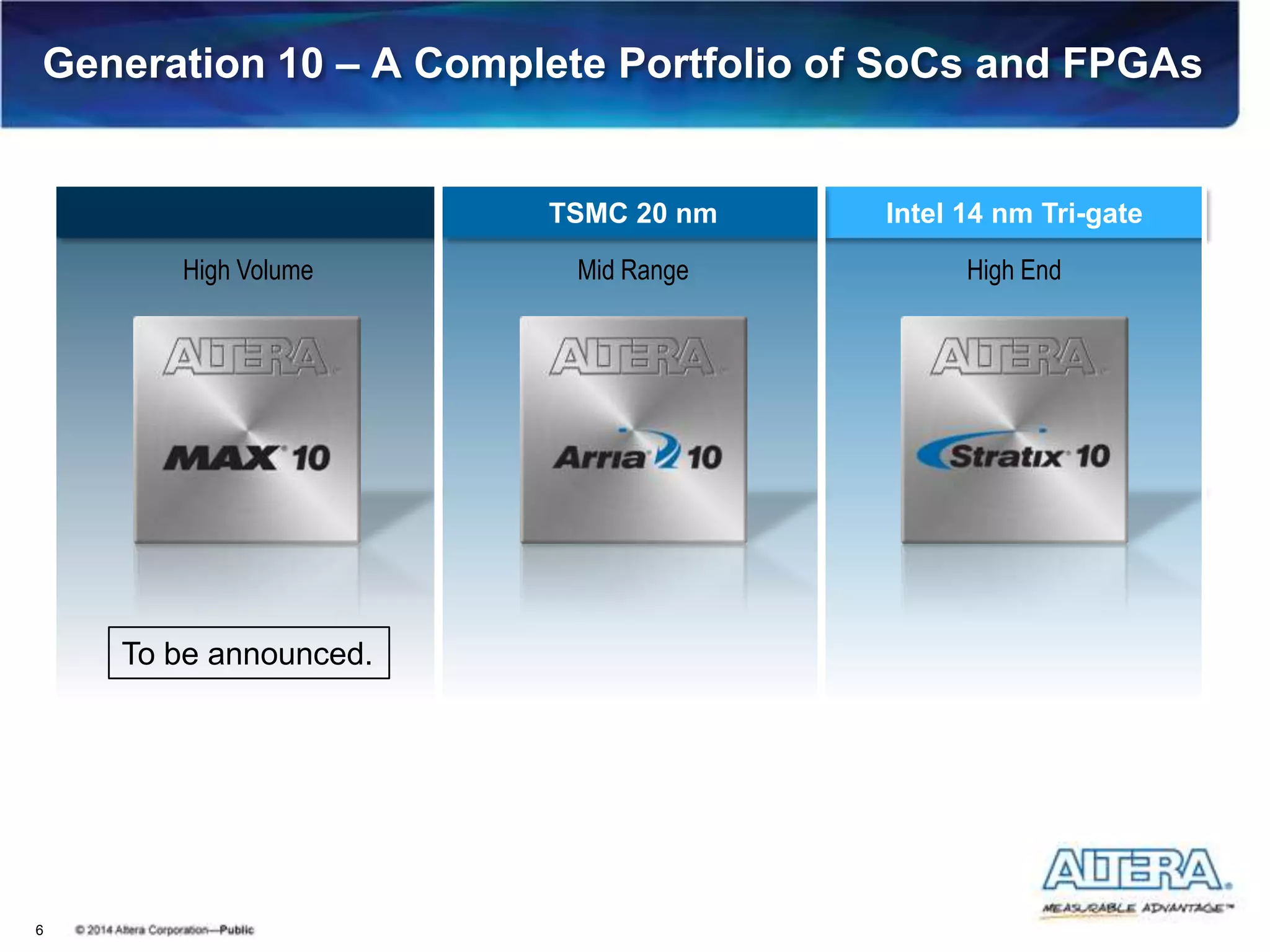

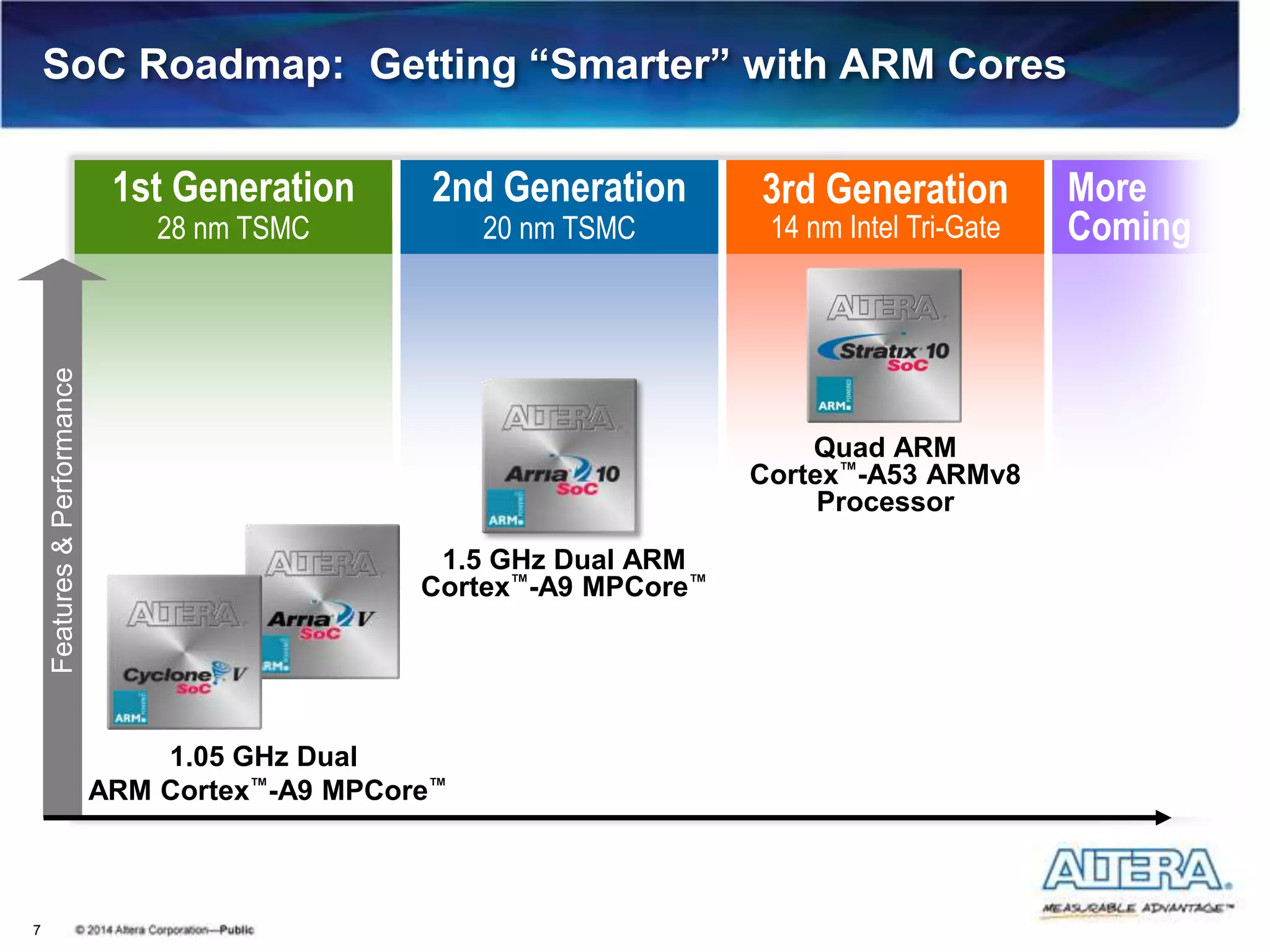

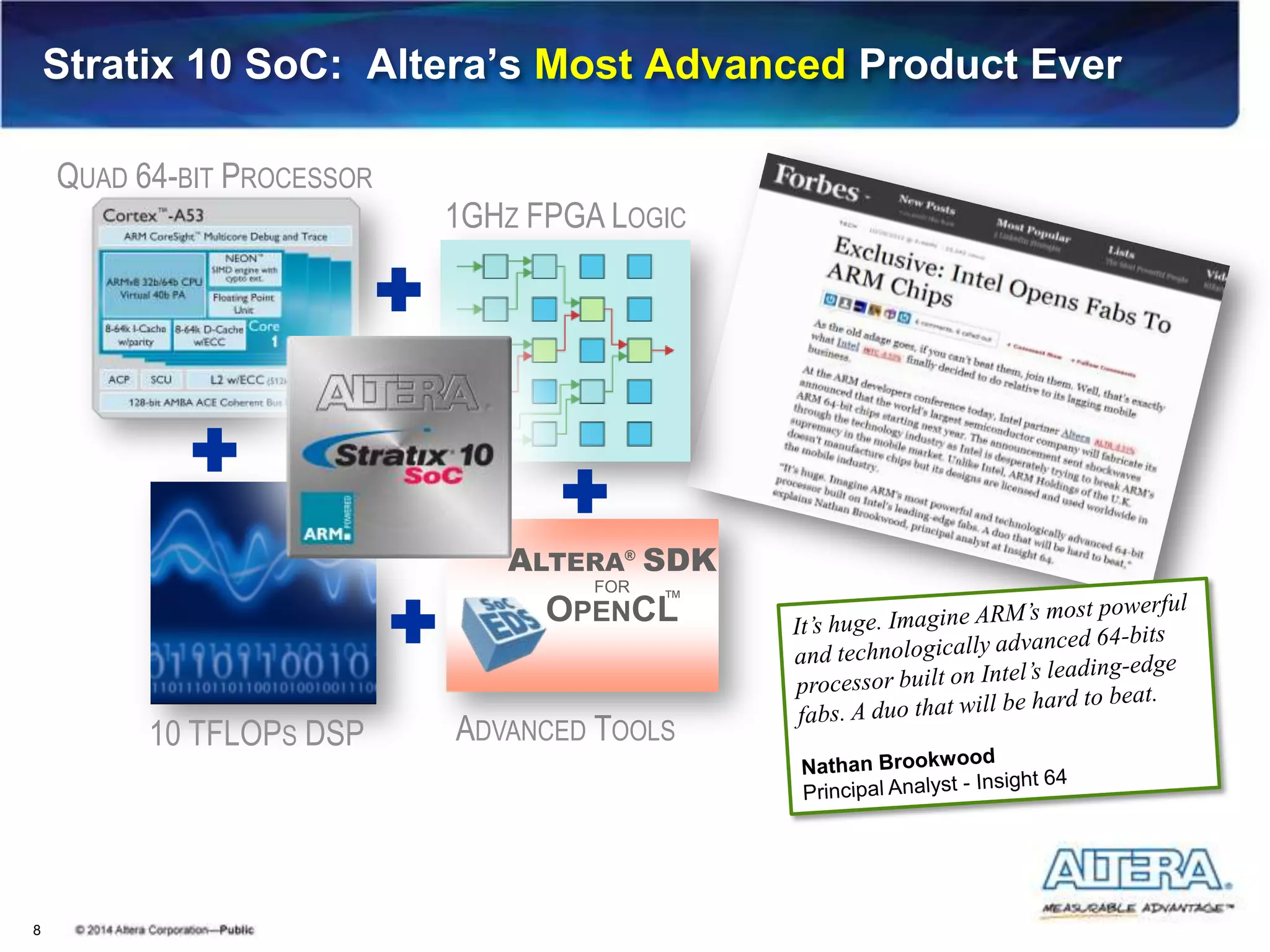

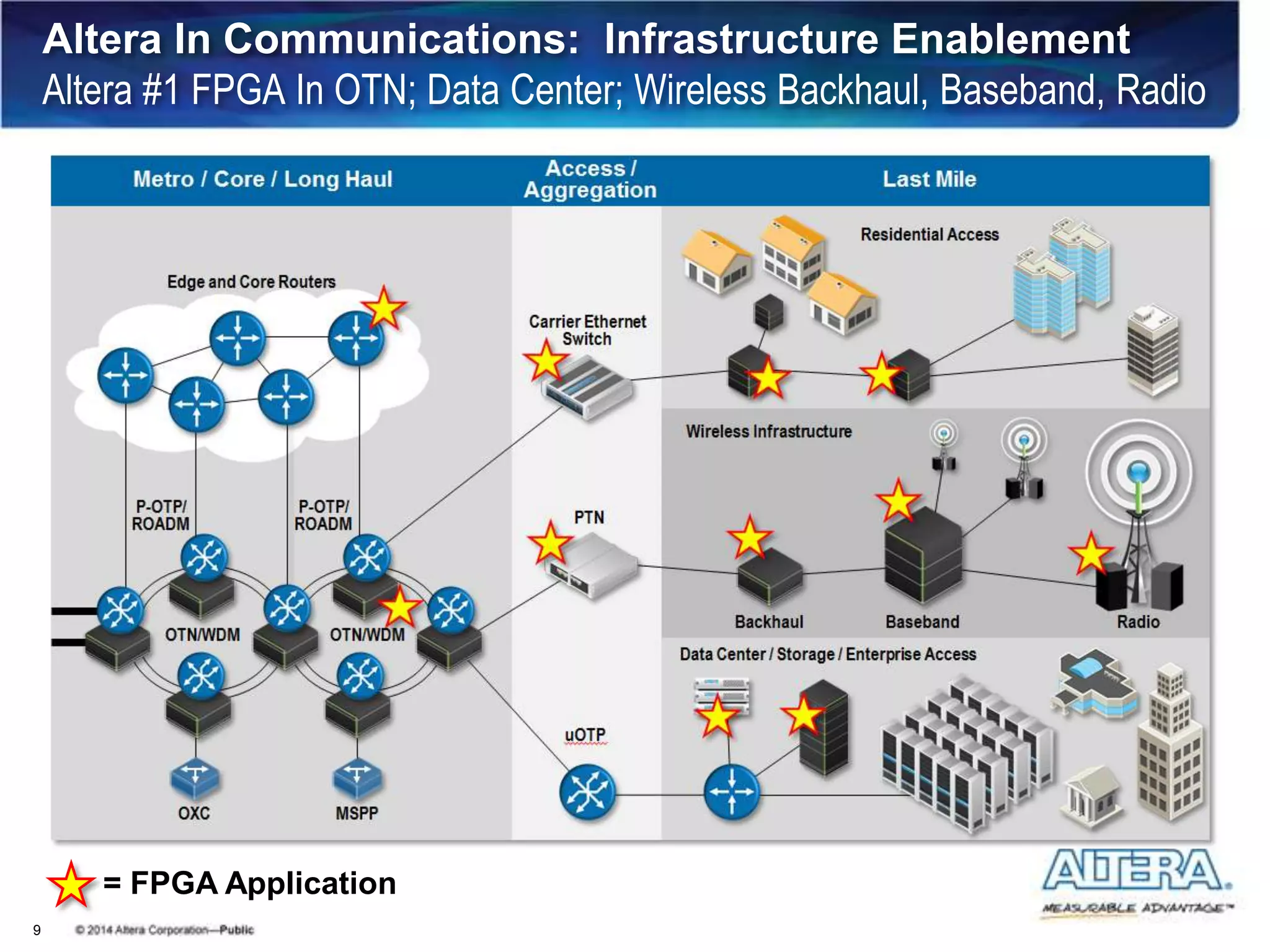

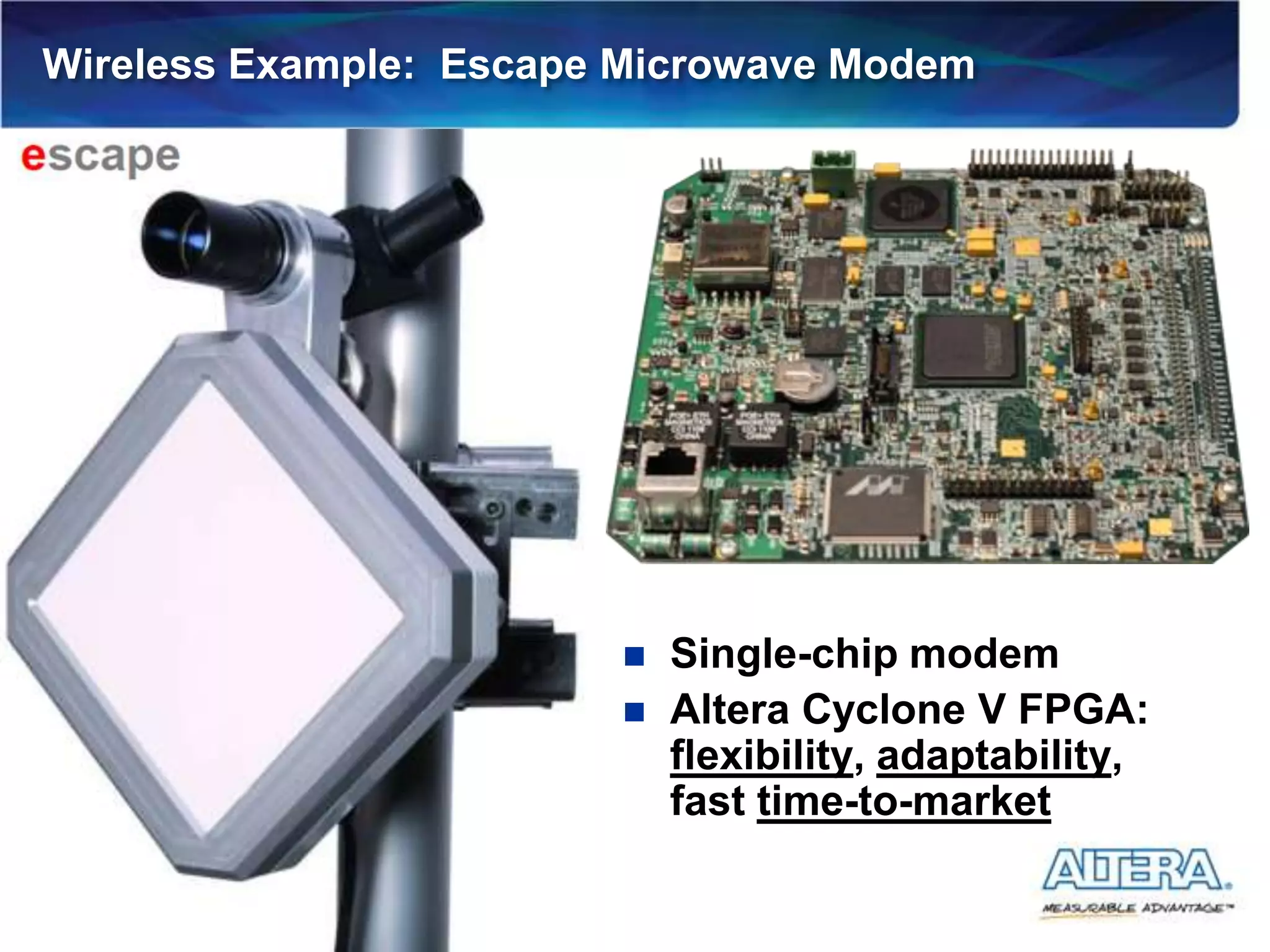

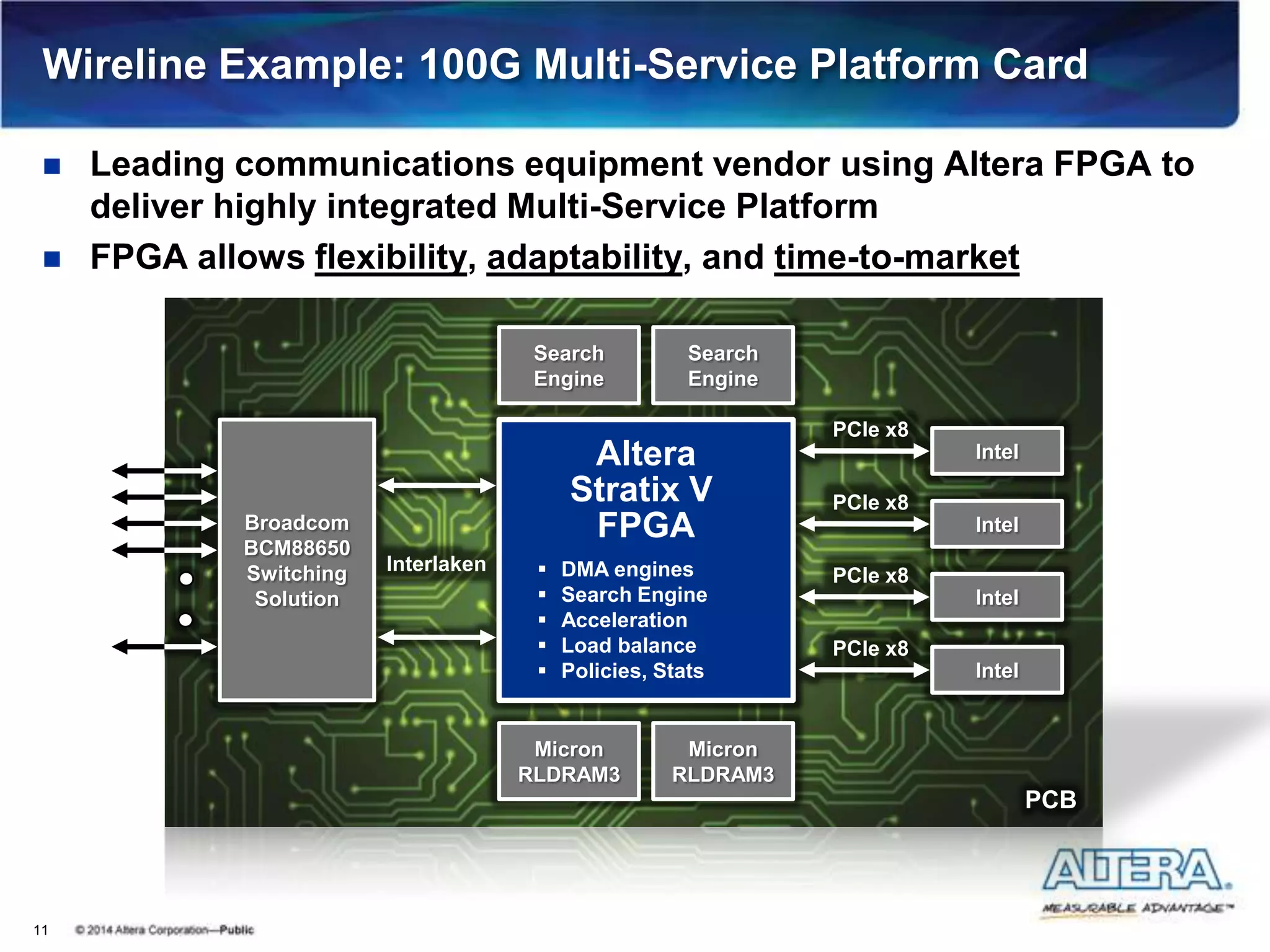

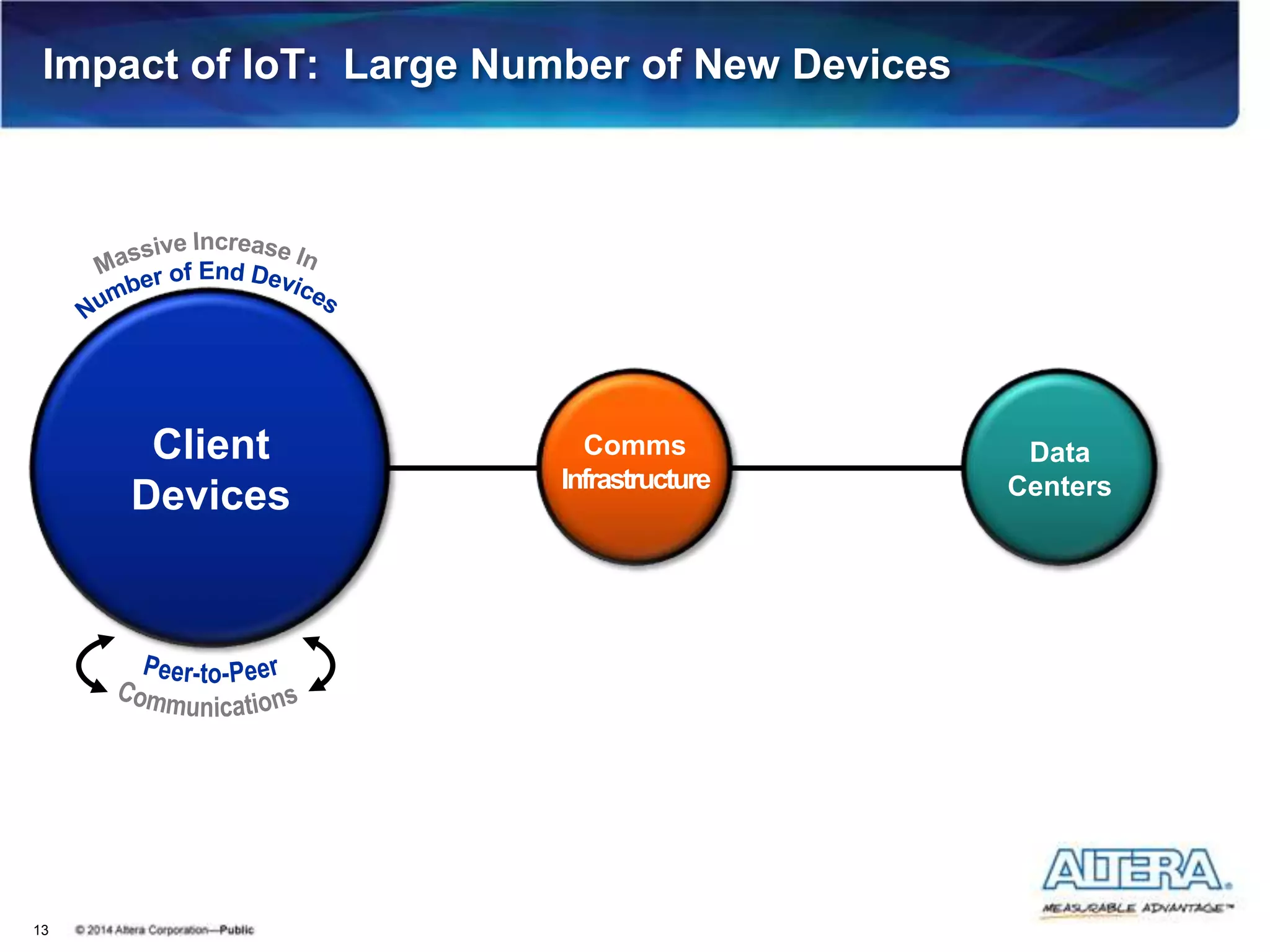

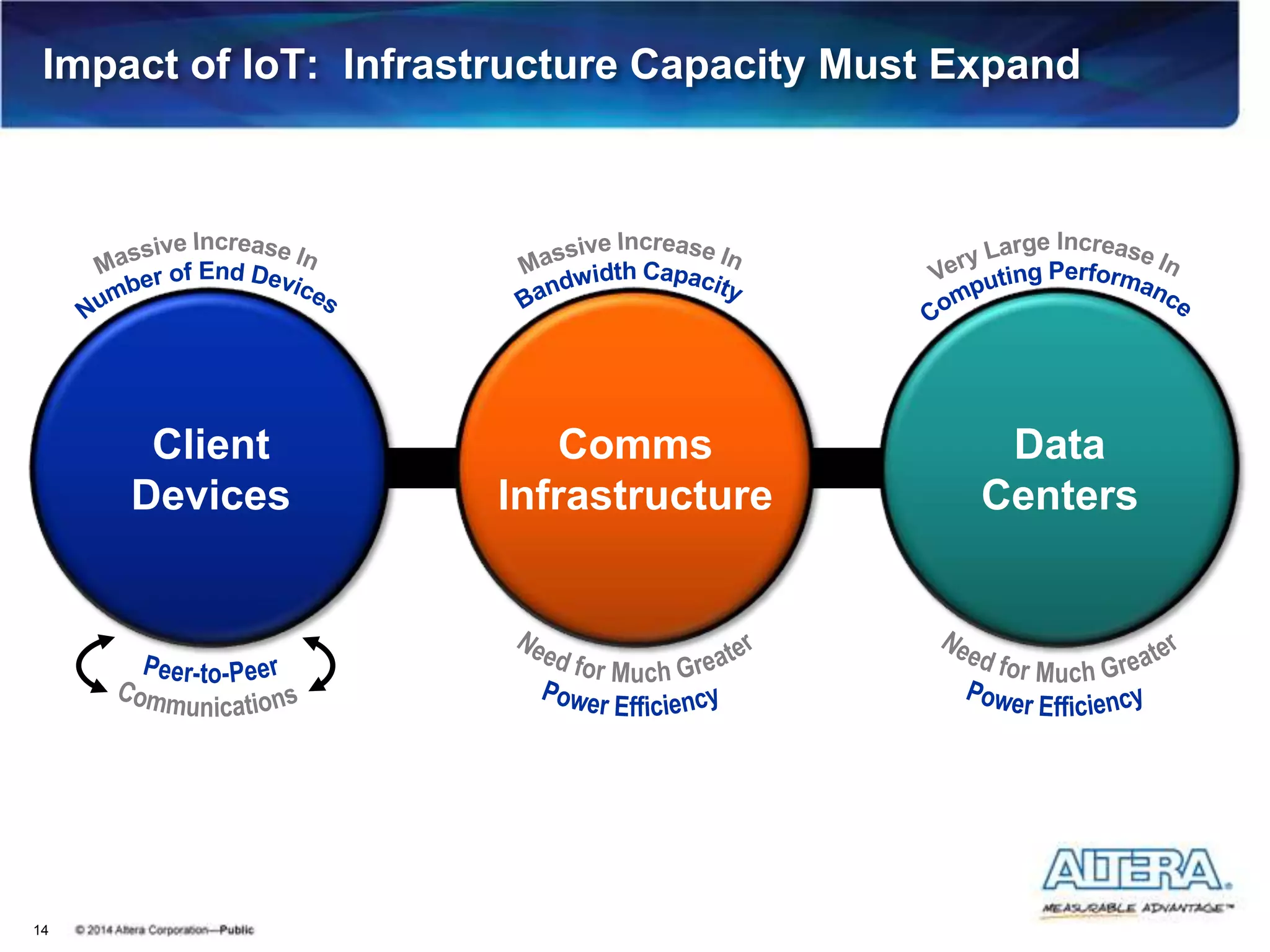

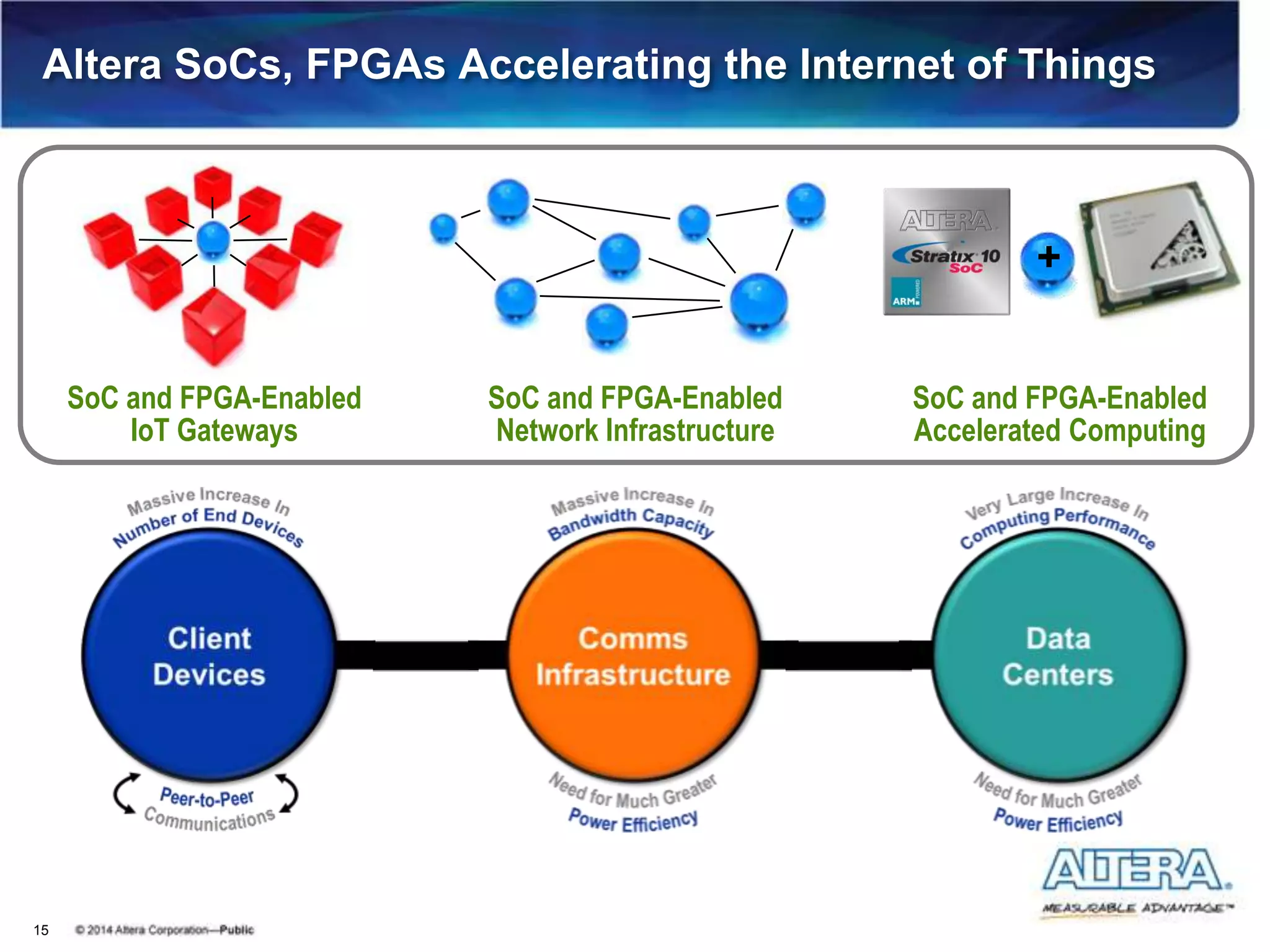

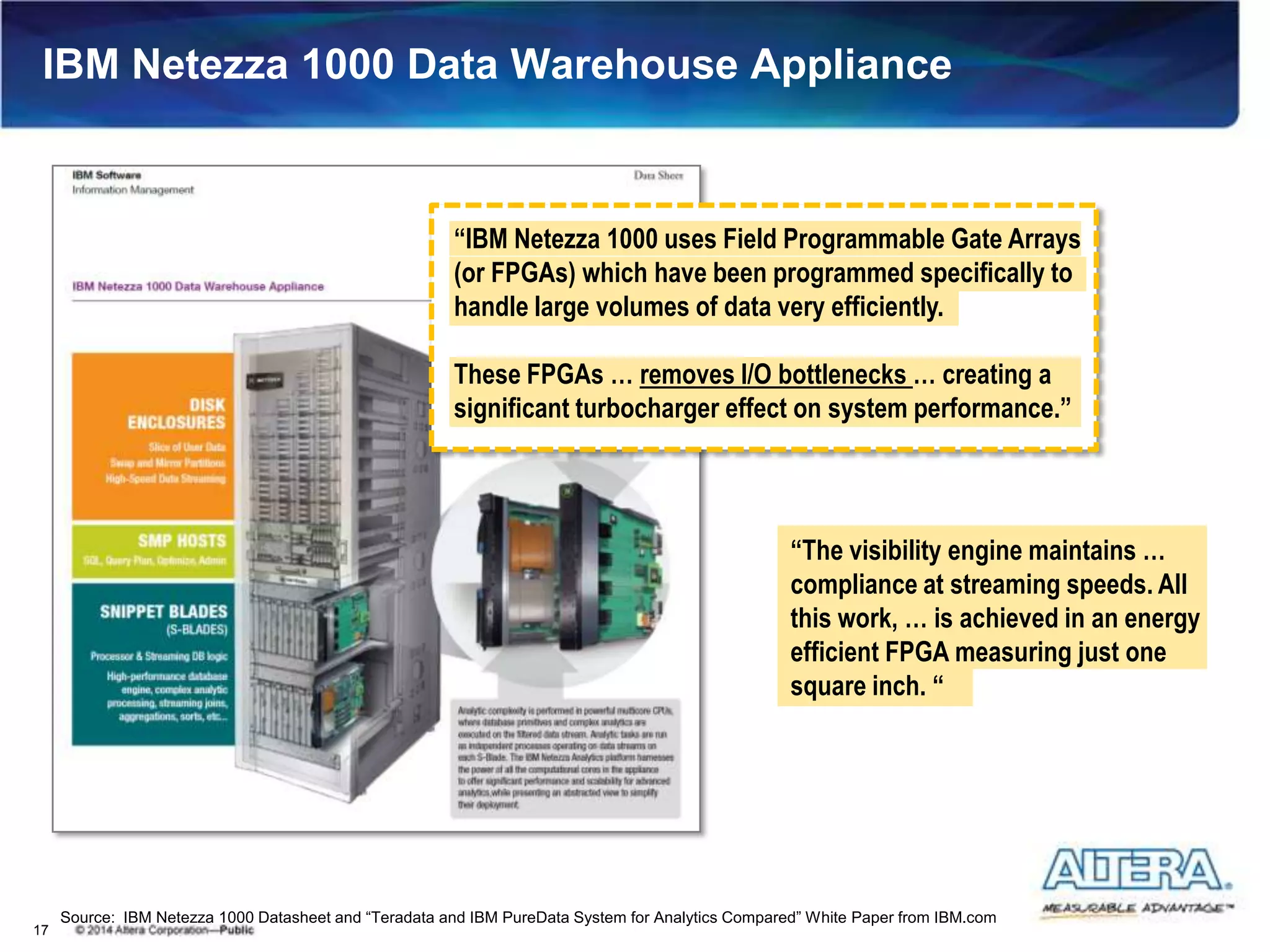

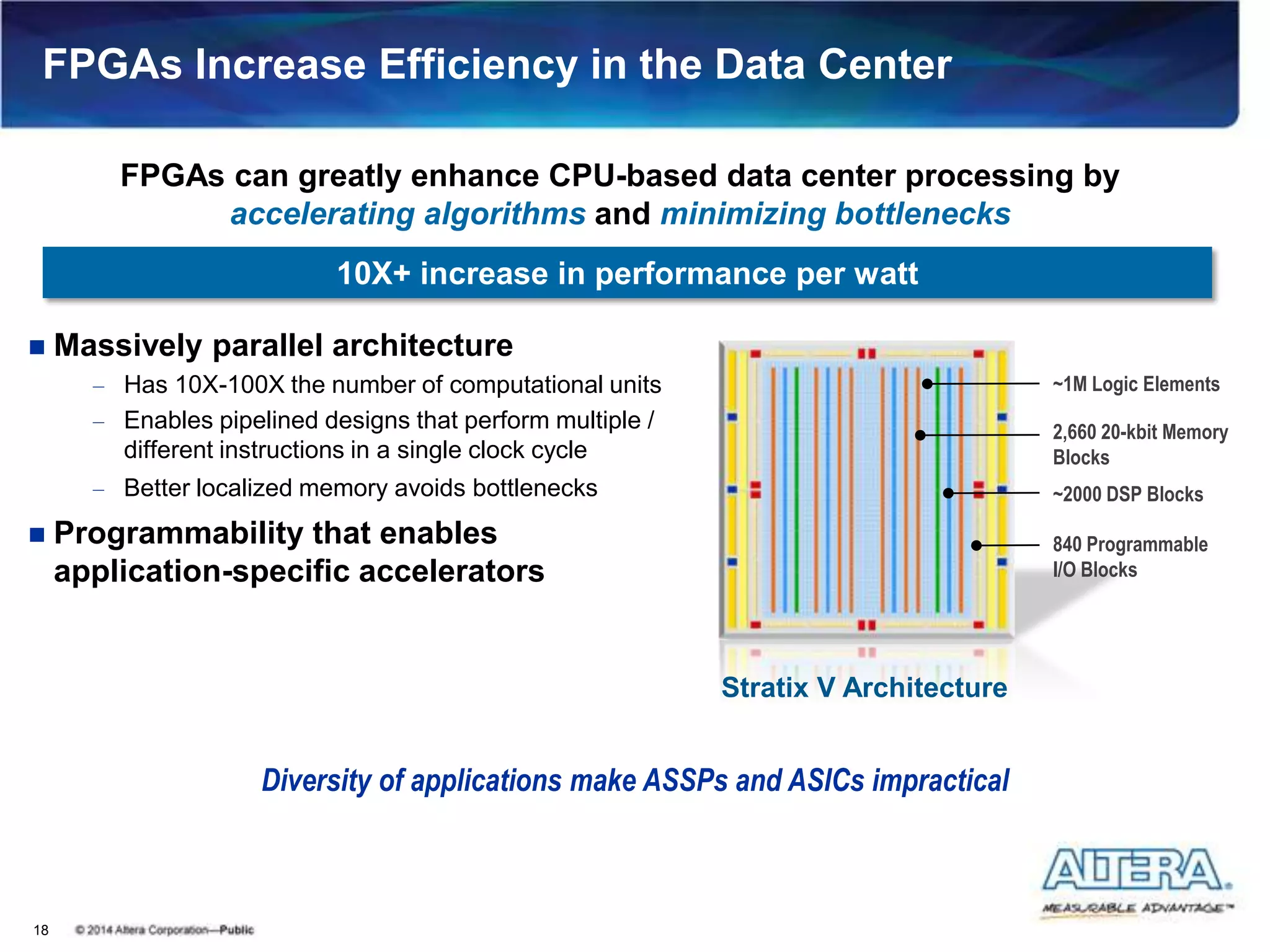

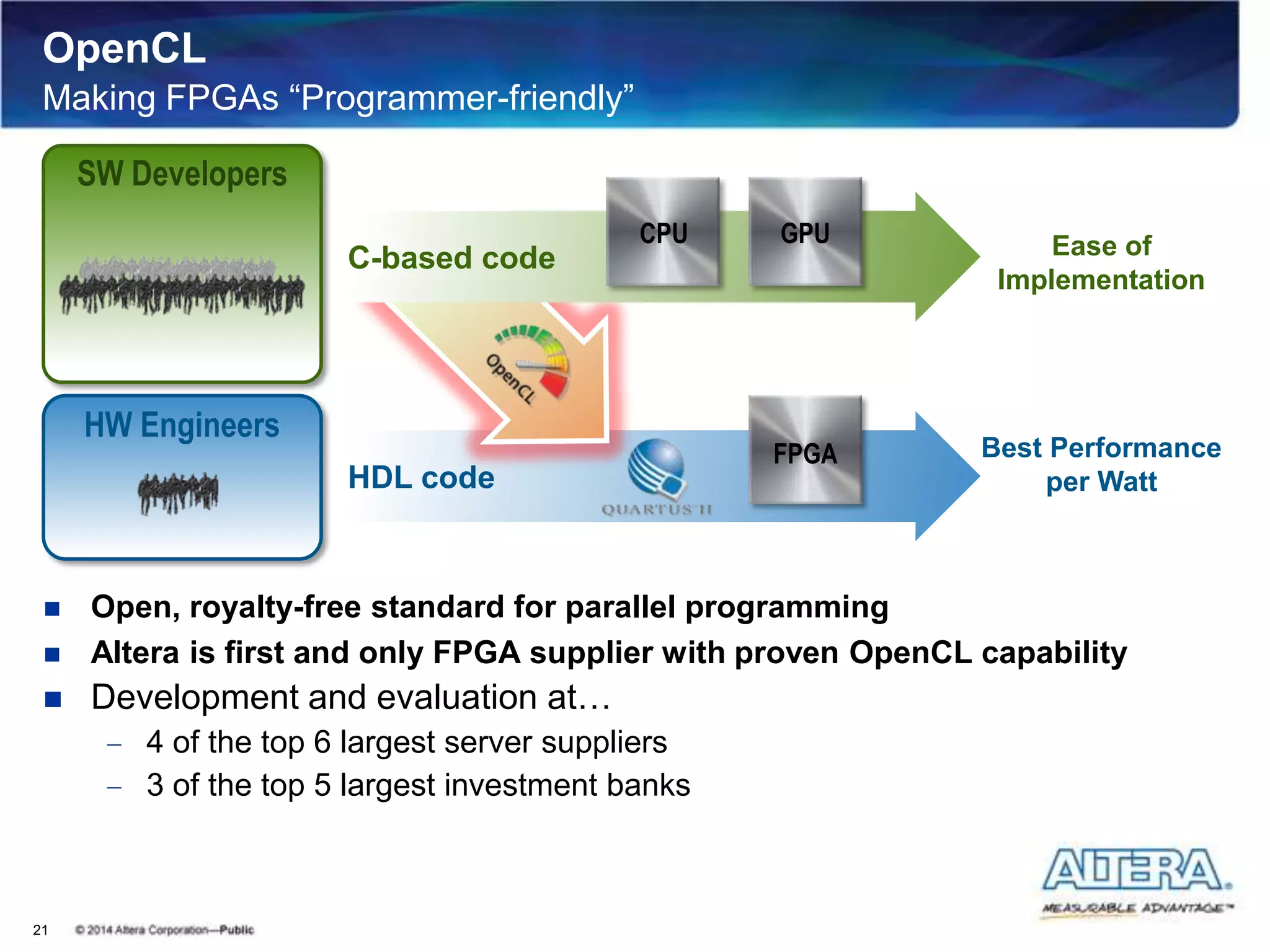

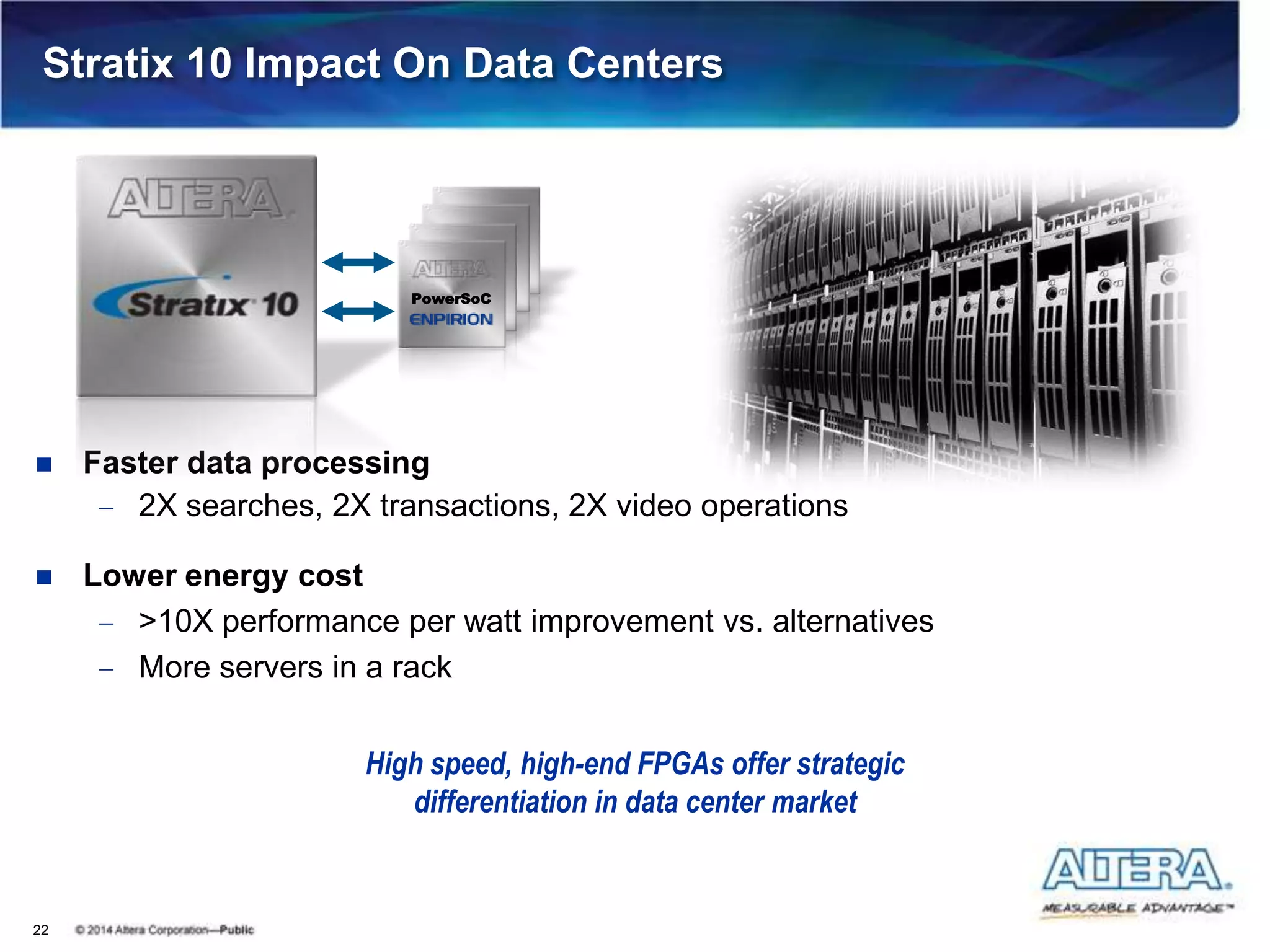

FPGAs are used throughout communications infrastructure and data centers for flexibility, adaptability, and faster time-to-market. Altera's new SoC devices combine FPGAs and ARM processors, making networks and data centers more ready to support the growing Internet of Things. The explosive growth of IoT devices is driving new requirements for communications infrastructure and data centers. Altera's newest FPGAs and SoCs will help enable these infrastructures to support the Internet of Things through increased flexibility and performance.