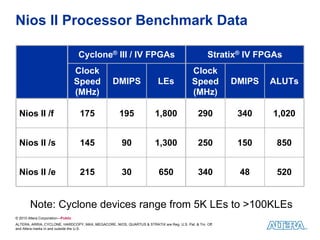

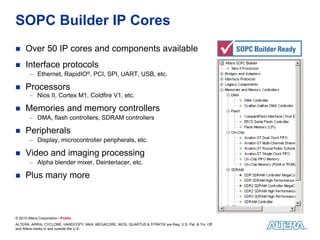

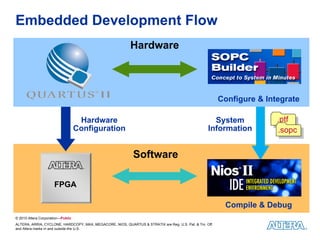

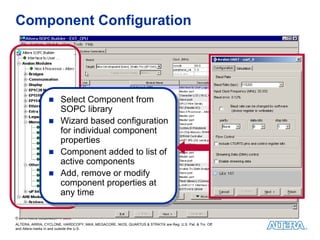

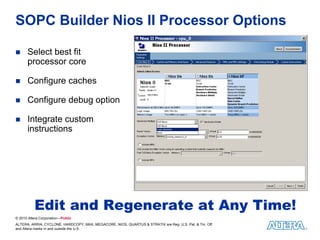

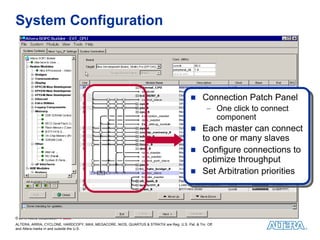

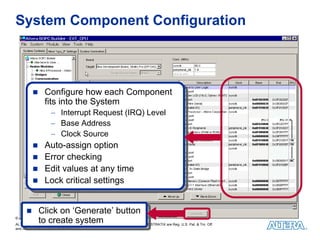

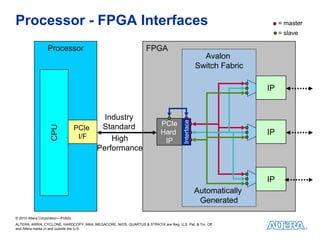

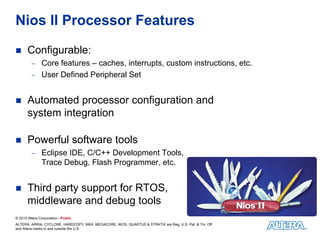

The document discusses the Nios II processor from Altera. It comes in three versions - FAST optimized for speed, STANDARD with balanced speed and size, and ECONOMY optimized for size. Software code is binary compatible across versions. The processor is configurable with features like caches and custom instructions. It integrates easily into systems using the SOPC Builder tool and works with development tools and operating systems.

![Nios II Processor Configuration

Nios II Processor Core

reset Instruction

General Master

Instruction and

Program

Instruction and

clock Purpose Port

Data Trace

Controller

Data Trace

Registers Instruction

JTAG interface Hardware- & Cache

to Software Assisted Address

Debugger Debug Module Generation Status &

Control

Registers Tightly

Tightly

High Speed Trace

Trace Coupled

Coupled

Connection Trace port

Trace port I-Memory

Memory

Memory I-Memory

to Trace Pod

Breakpoints

Breakpoints

Exception Tightly

Tightly

HW

Controller MMU

HW

Coupled

Coupled

D-Memory

D-Memory

Interrupt MPU

irq[31..0] Controller Data

Master

Port

Data

Custom Cache

Custom Instruction Arithmetic

I/O Signals Logic Logic Unit

© 2010 Altera Corporation—Public

= Configurable = Optional & Configurable

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U.S. Pat. & Tm. Off.

and Altera marks in and outside the U.S.

= Fixed = Debug Options](https://image.slidesharecdn.com/alteralearningzoneatembeddedworld2010-niosiiprocessor-100413134822-phpapp01/85/Nios-II-Embedded-Processor-Embedded-World-2010-4-320.jpg)