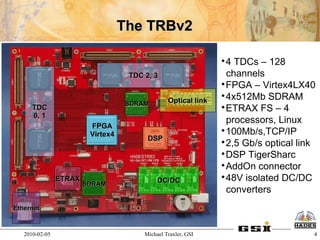

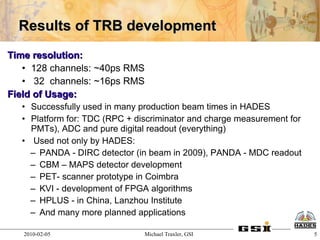

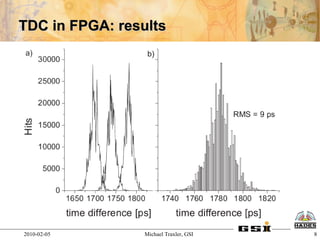

The TRB was developed as a general purpose platform for time-to-digital converters (TDCs) and fast data acquisition for nuclear physics experiments with thousands of channels. It provides integrated TDC, data acquisition, and local computing capabilities in a modular design that can be directly mounted on detectors. Measurements showed time resolutions of 40 picoseconds for 128 channels and 16 picoseconds for 32 channels. The TRB has been successfully used in several experiments and more developments are planned to further improve performance and reduce costs.