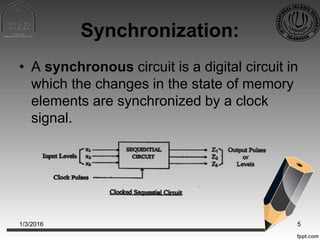

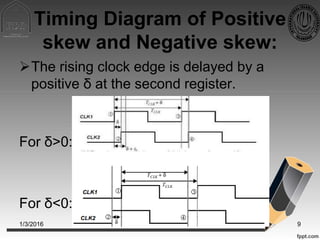

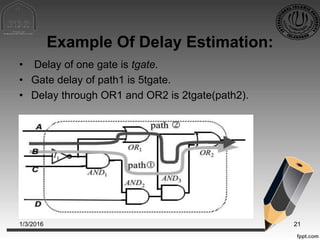

The document discusses timing issues in digital circuits such as synchronization, clock skew, and clock jitter. It provides definitions and examples of these timing phenomena. Sources of skew and jitter are explained, including clock signal generation, manufacturing variations, interconnect variations, and environmental factors. The dynamic behavior of a CMOS inverter is analyzed by examining its parasitic capacitances. Solutions to timing issues include reducing clock skew through careful clock distribution, tolerating skew with circuit designs, and minimizing jitter.