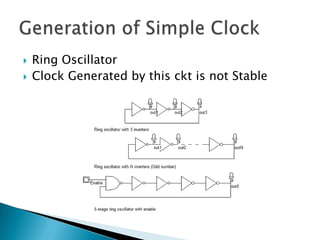

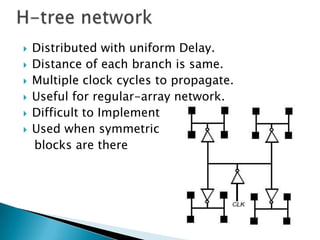

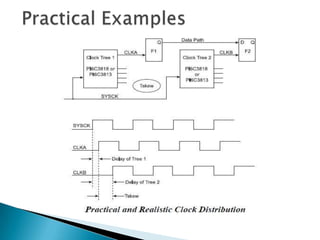

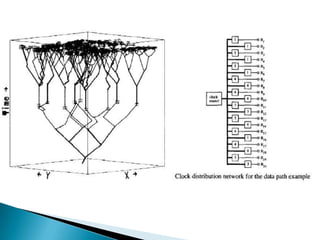

This document discusses various clock generation and distribution strategies for digital systems. It covers topics such as clock skew, jitter, ring oscillators, Pierce crystal oscillators, generating non-overlapping clock signals, H-tree networks, clock decoders, buffering clock signals, and eliminating clock skew through buffer cross-connections. The document provides an overview of ideal clock signal properties and challenges in practical implementations, as well as important considerations for high-performance clock distribution such as minimizing load capacitance and inductive networks.