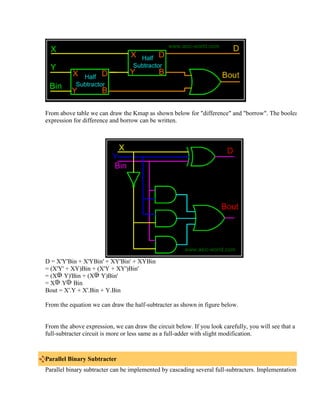

Subtracter circuits take two binary numbers as input and output their difference and a borrow value. There are two main types: half subtracters, which perform subtraction on two bits, and full subtracters, which perform subtraction on three bits including a borrow-in. A parallel binary subtracter can be implemented by cascading multiple full subtracters to perform subtraction on binary numbers of any length.