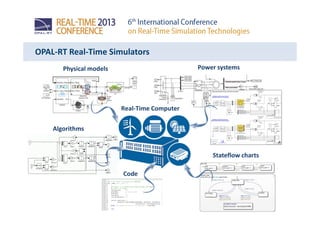

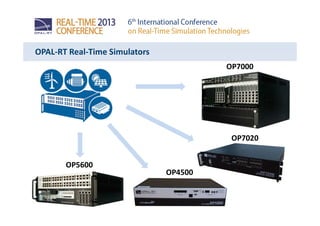

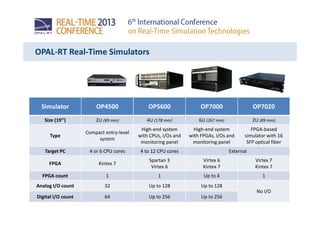

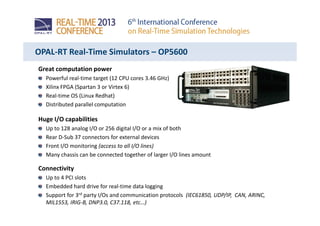

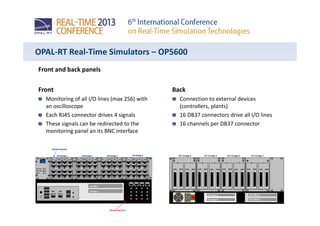

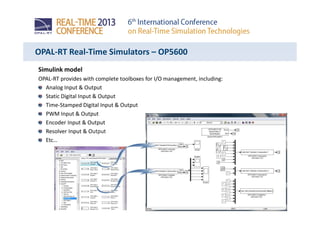

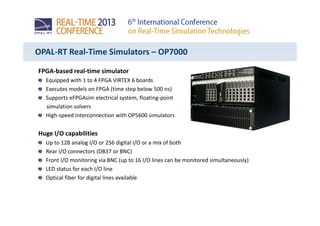

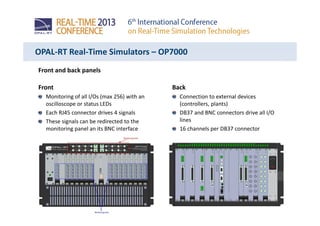

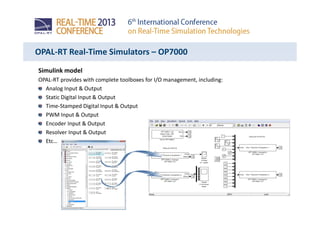

The document discusses OP5600 and OP7000 real-time simulators from OPAL-RT for applications like rapid control prototyping and hardware-in-the-loop testing. The OP5600 is a high-end system with up to 12 CPU cores and FPGA that allows distributed parallel computation and large I/O capabilities. The OP7000 is FPGA-based and can execute models on FPGAs faster than 500ns. Both simulators support real-time execution of Simulink models and have flexible and scalable I/O options.