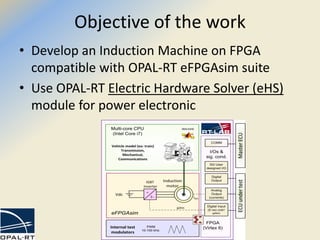

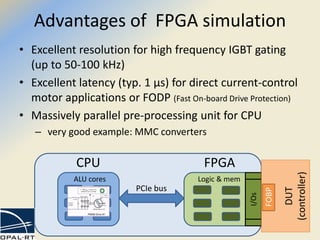

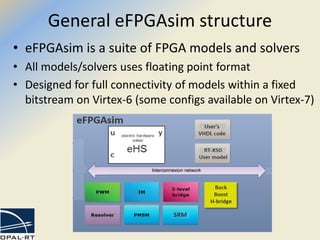

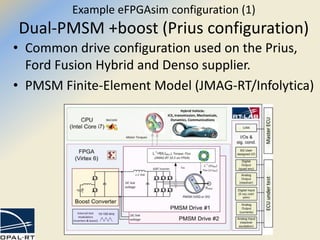

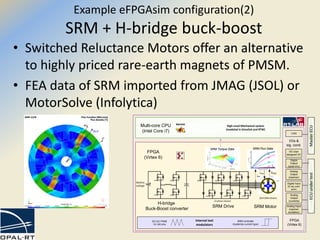

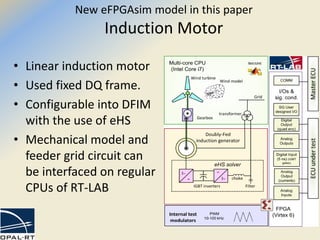

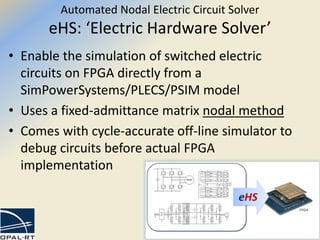

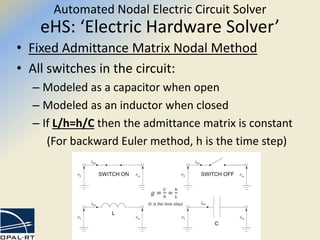

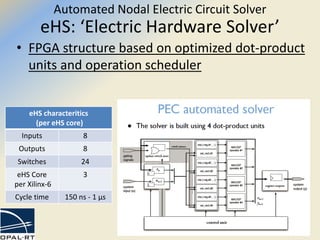

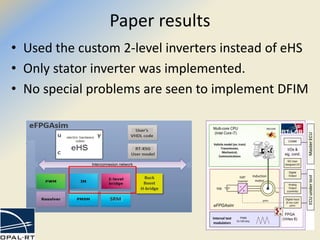

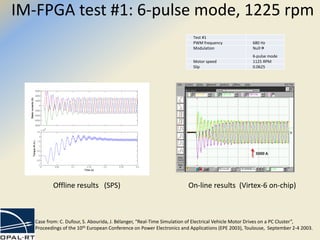

The document discusses the development of an induction machine simulation compatible with the Opal-RT eFPGASim suite using FPGA technology, highlighting its advantages like high frequency response and low latency, while addressing challenges such as coding complexity and long compilation times. It outlines the functionalities of the electric hardware solver (EHS) for simulating switched electric circuits, emphasizing the new induction machine model that leverages this technology for efficiency in power electronics. Overall, eFPGASim is presented as an effective tool to enhance testing and reduce costs in motor drive and power electronic systems development.