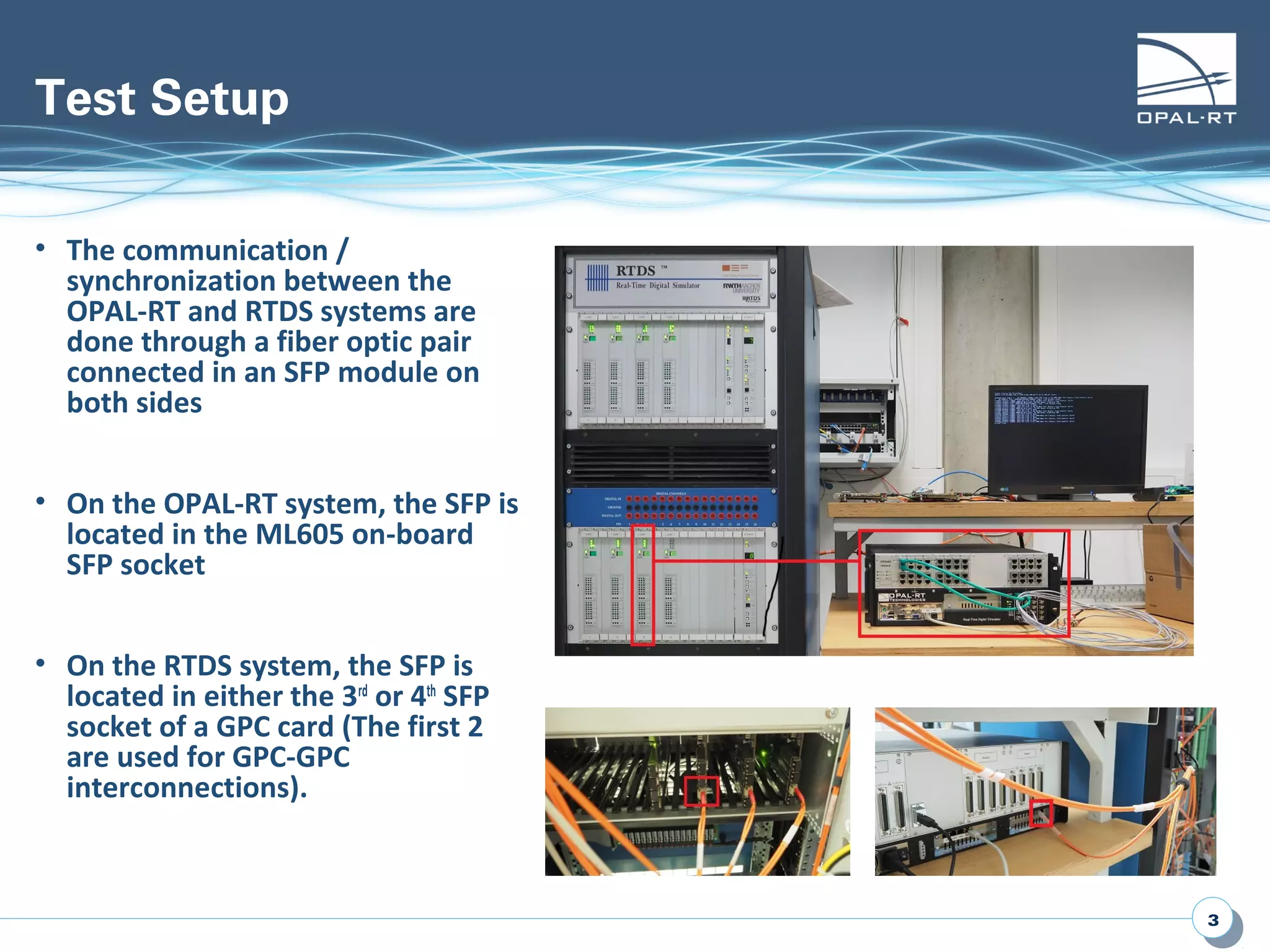

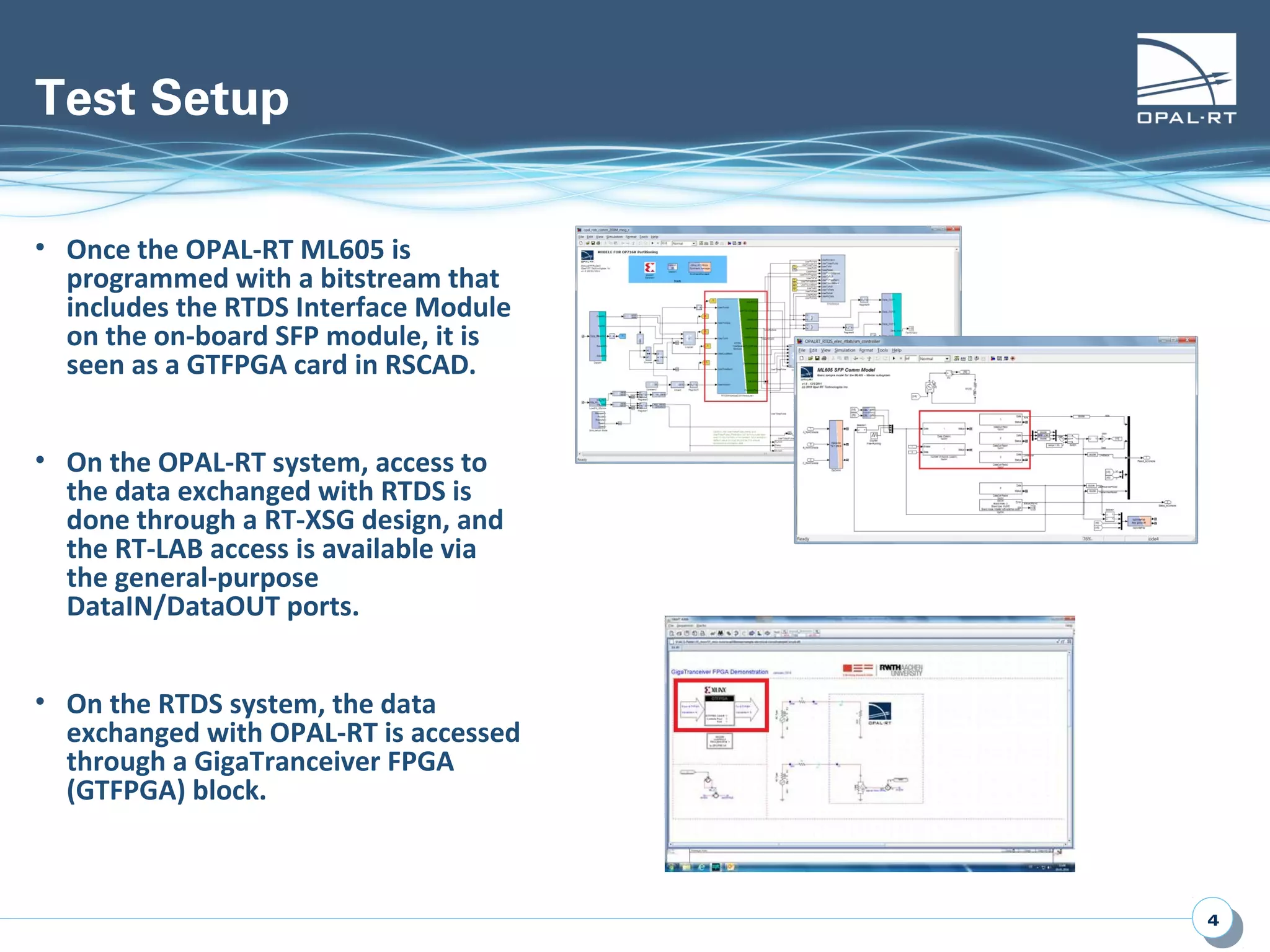

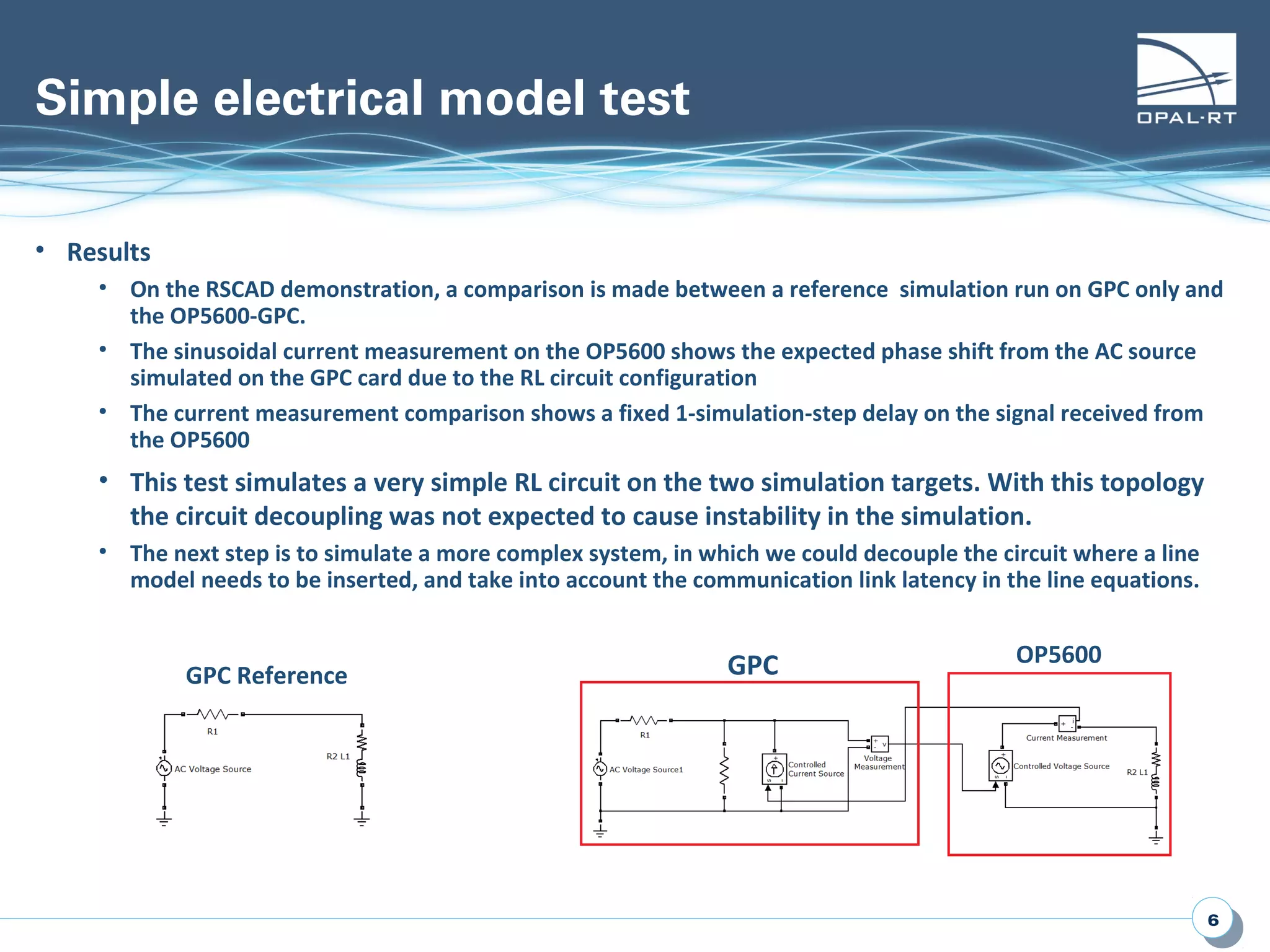

The document details the co-simulation setup between Opal-RT and RTDS systems, specifying hardware and software requirements. It describes the testing of a simple RL circuit and synchronization model, highlighting communication and latency measurements between the two systems. The results indicate successful synchronization and the impact of communication delays on simulation performance, guiding potential enhancements for complex system simulations.