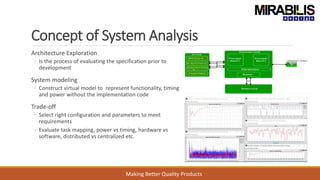

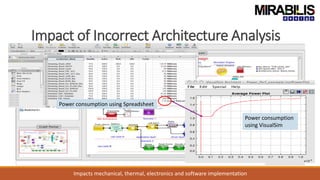

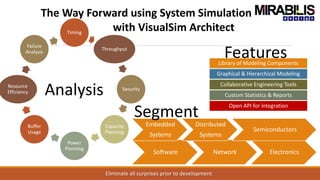

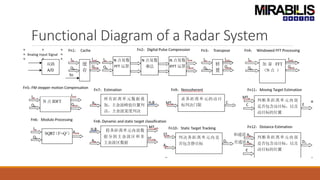

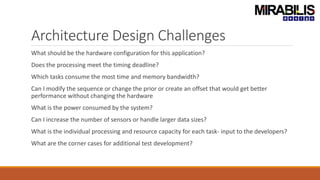

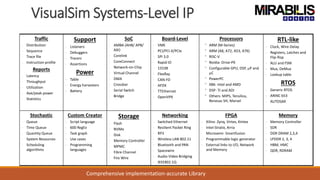

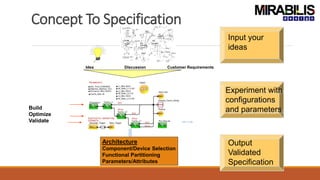

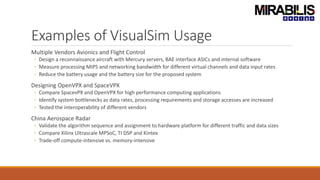

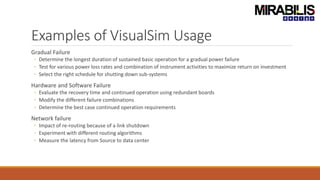

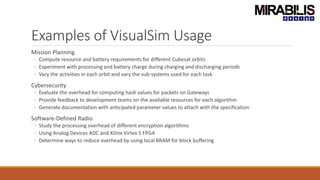

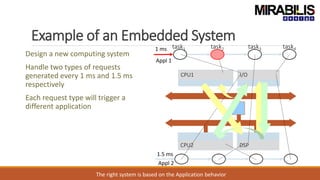

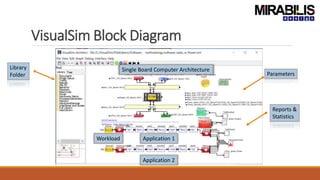

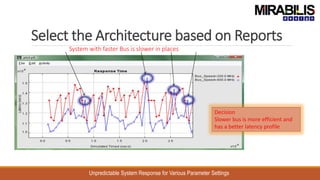

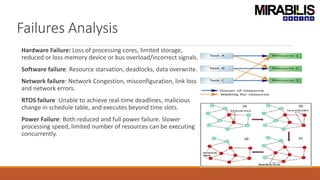

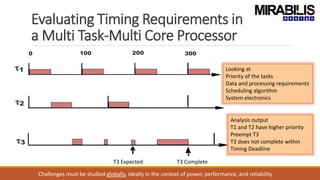

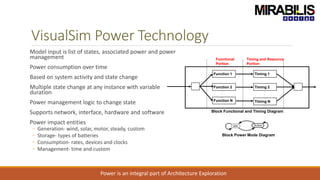

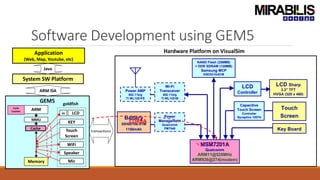

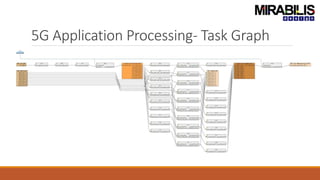

The document discusses the use of VisualSim Architect software for system modeling and simulation, emphasizing its applications in radar systems and software-defined radios. It explores the challenges of system architecture, power consumption, and task mapping while providing examples of VisualSim in various industries such as aerospace and automotive. The overall aim is to assist engineers in optimizing designs by evaluating specifications and performance metrics before the development phase.