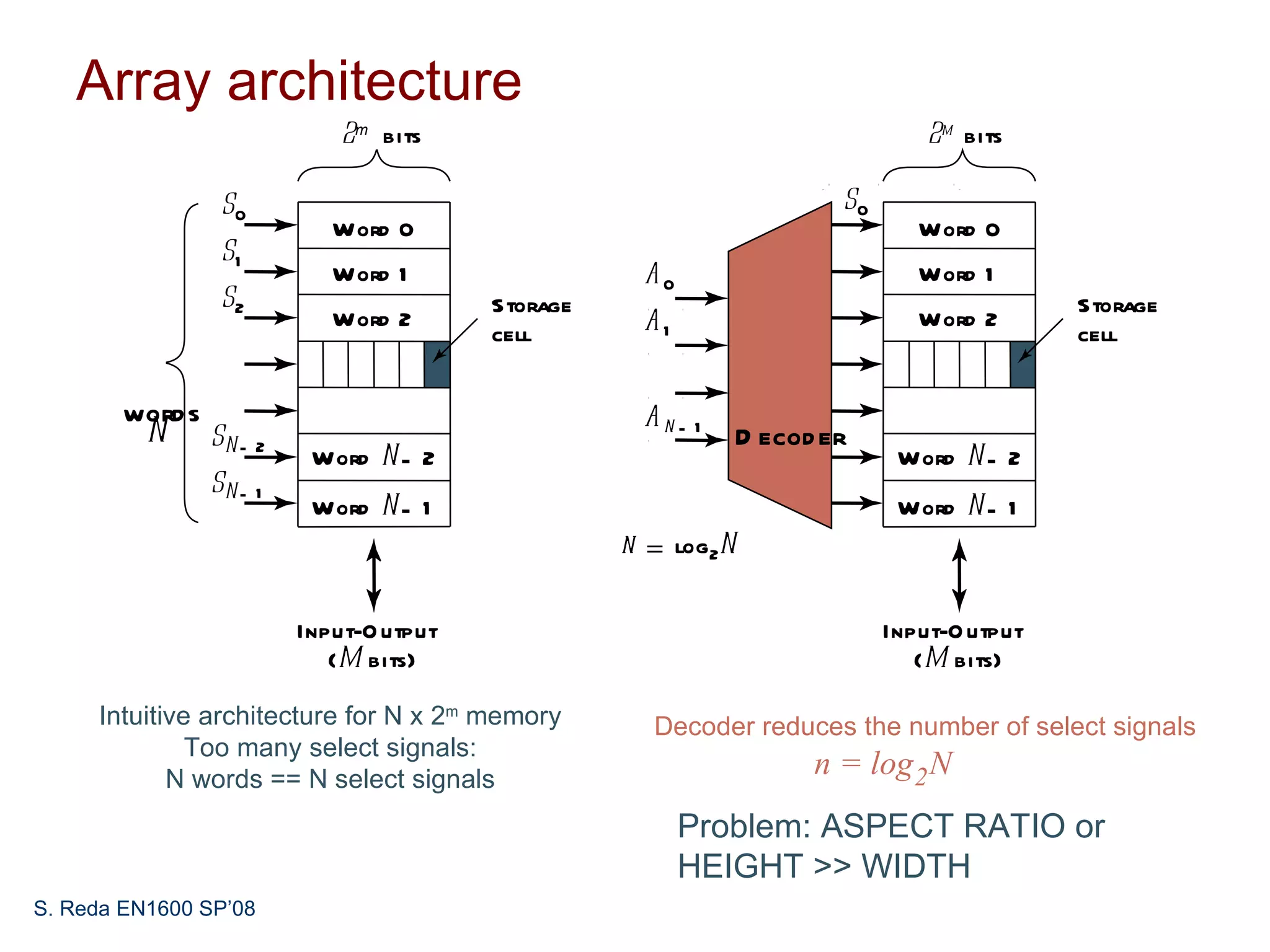

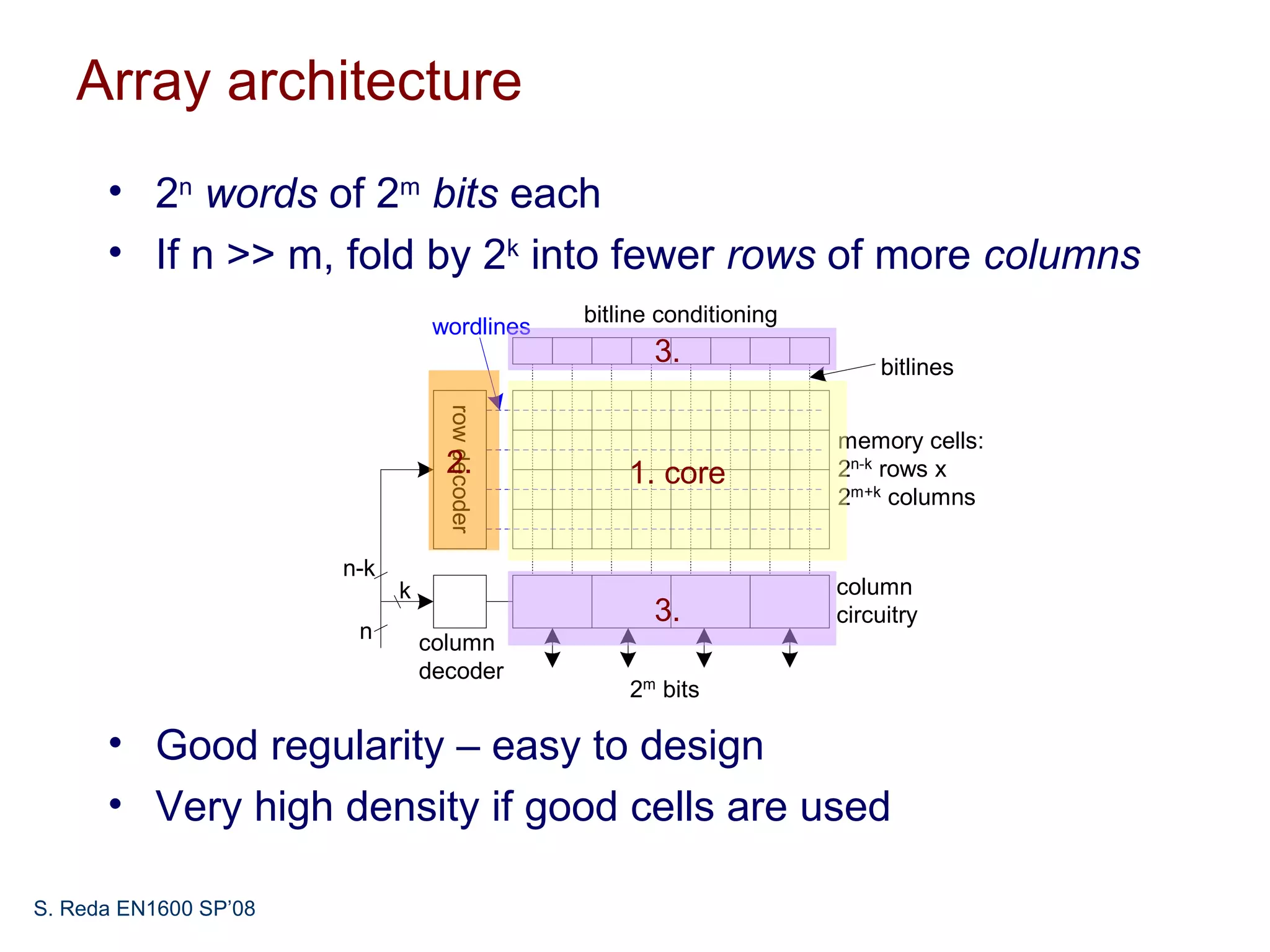

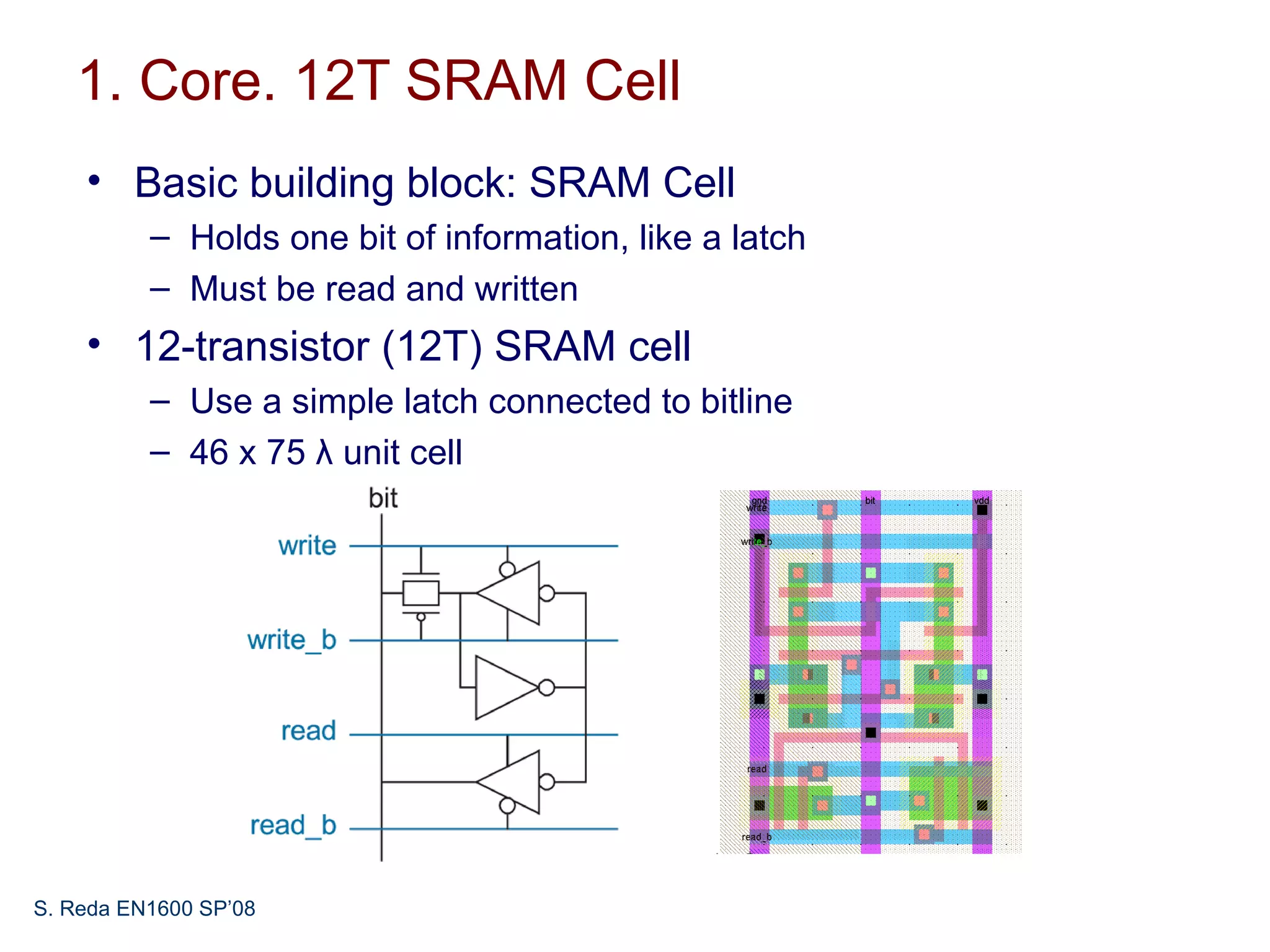

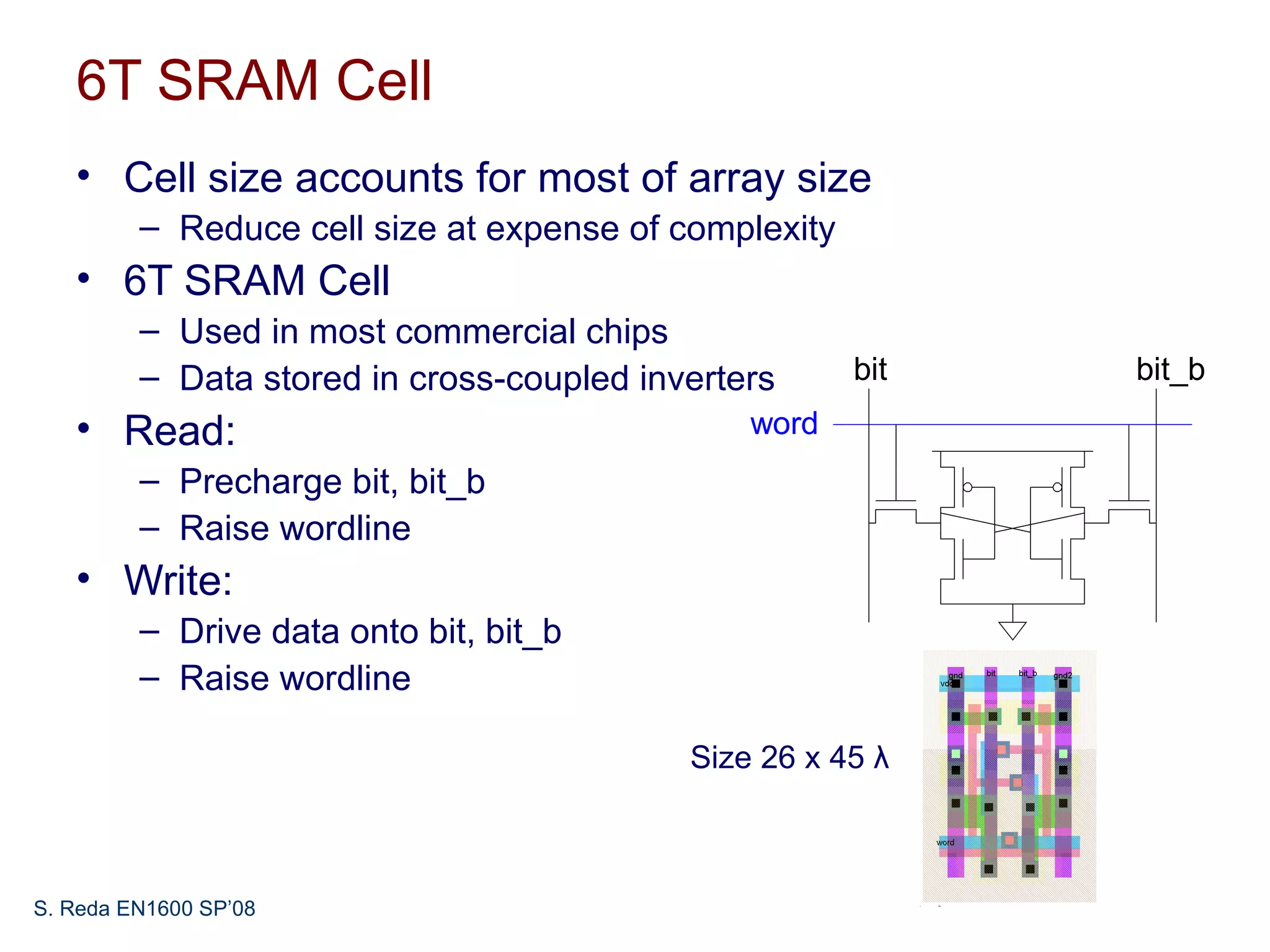

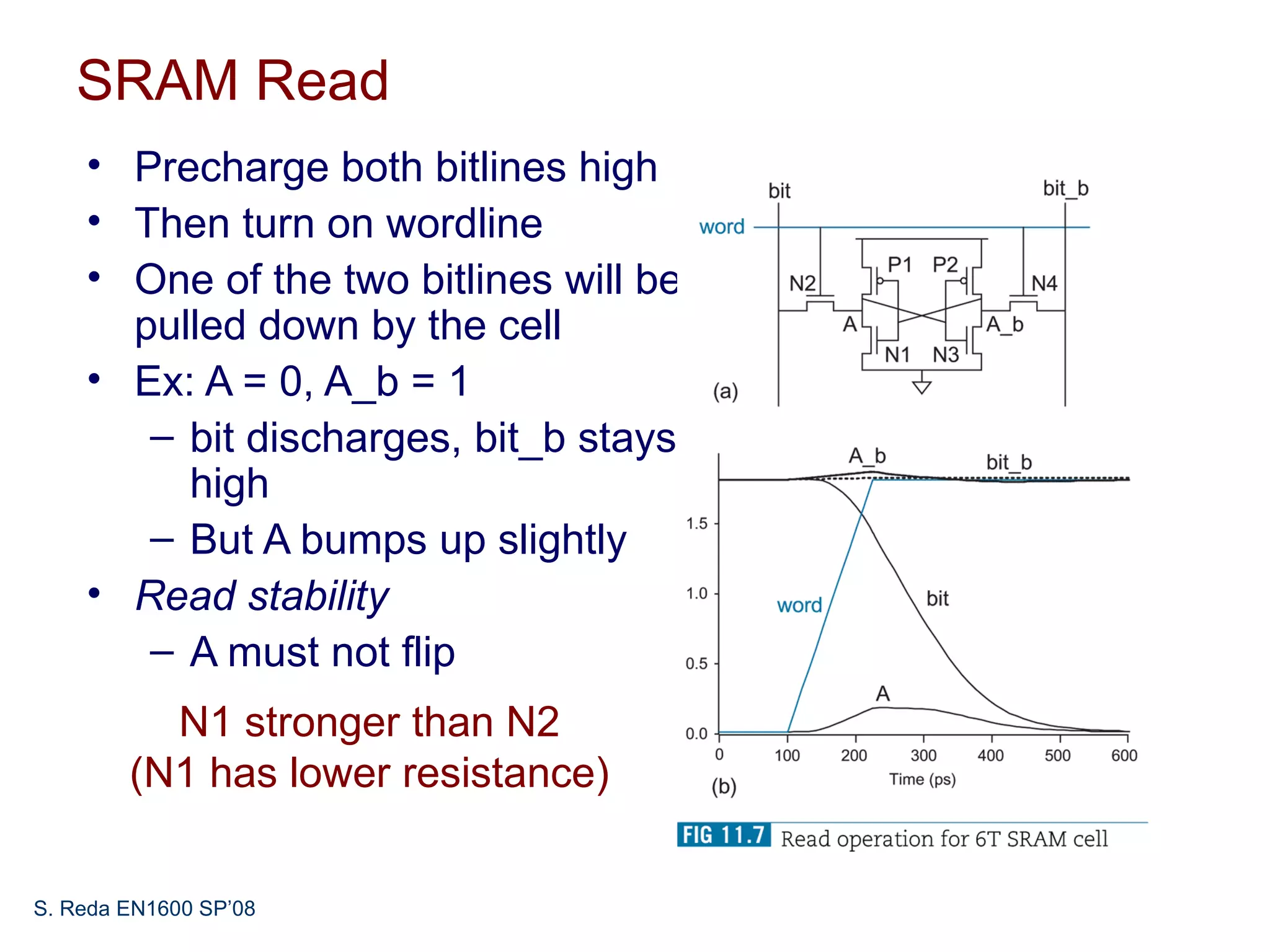

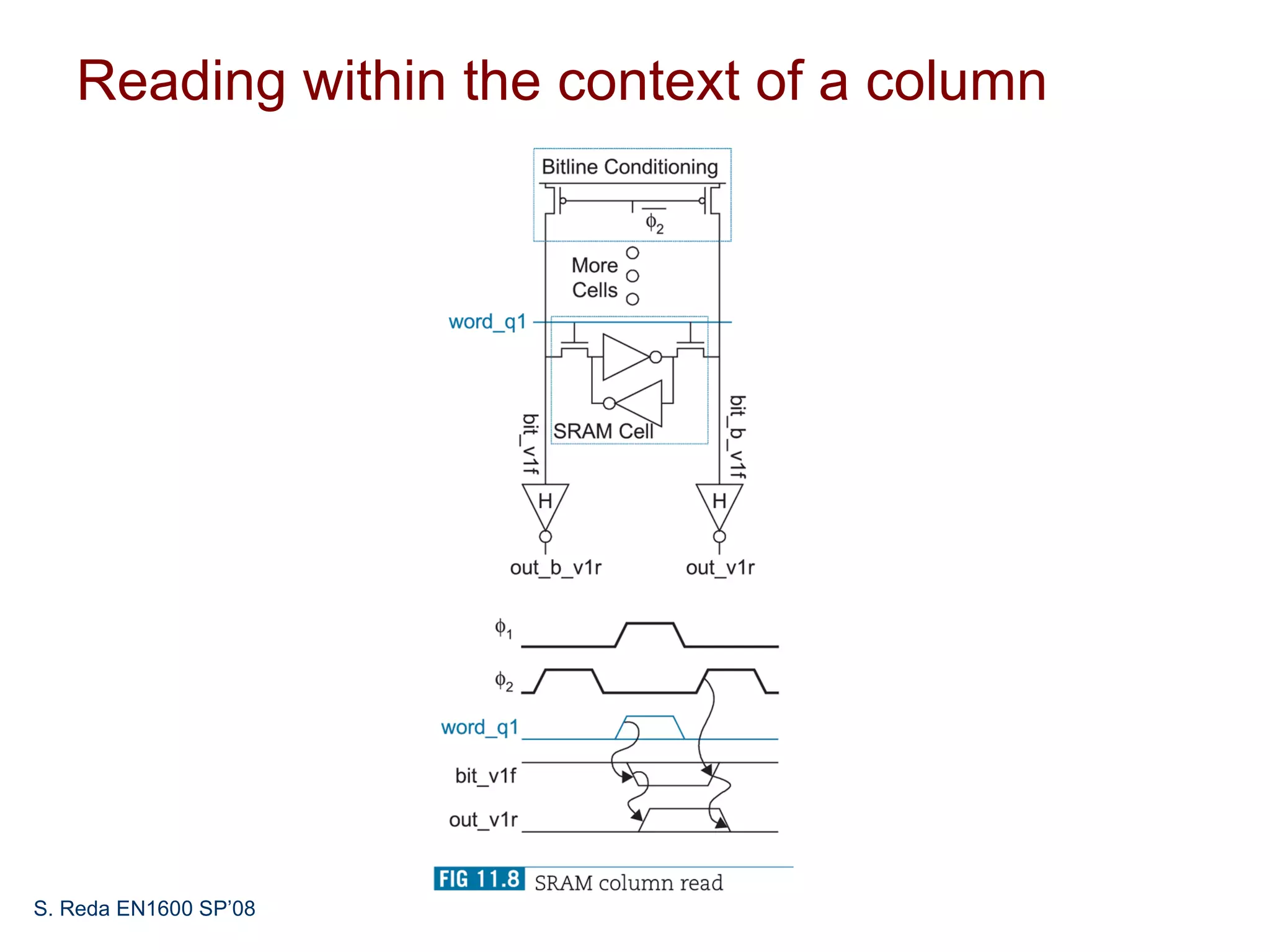

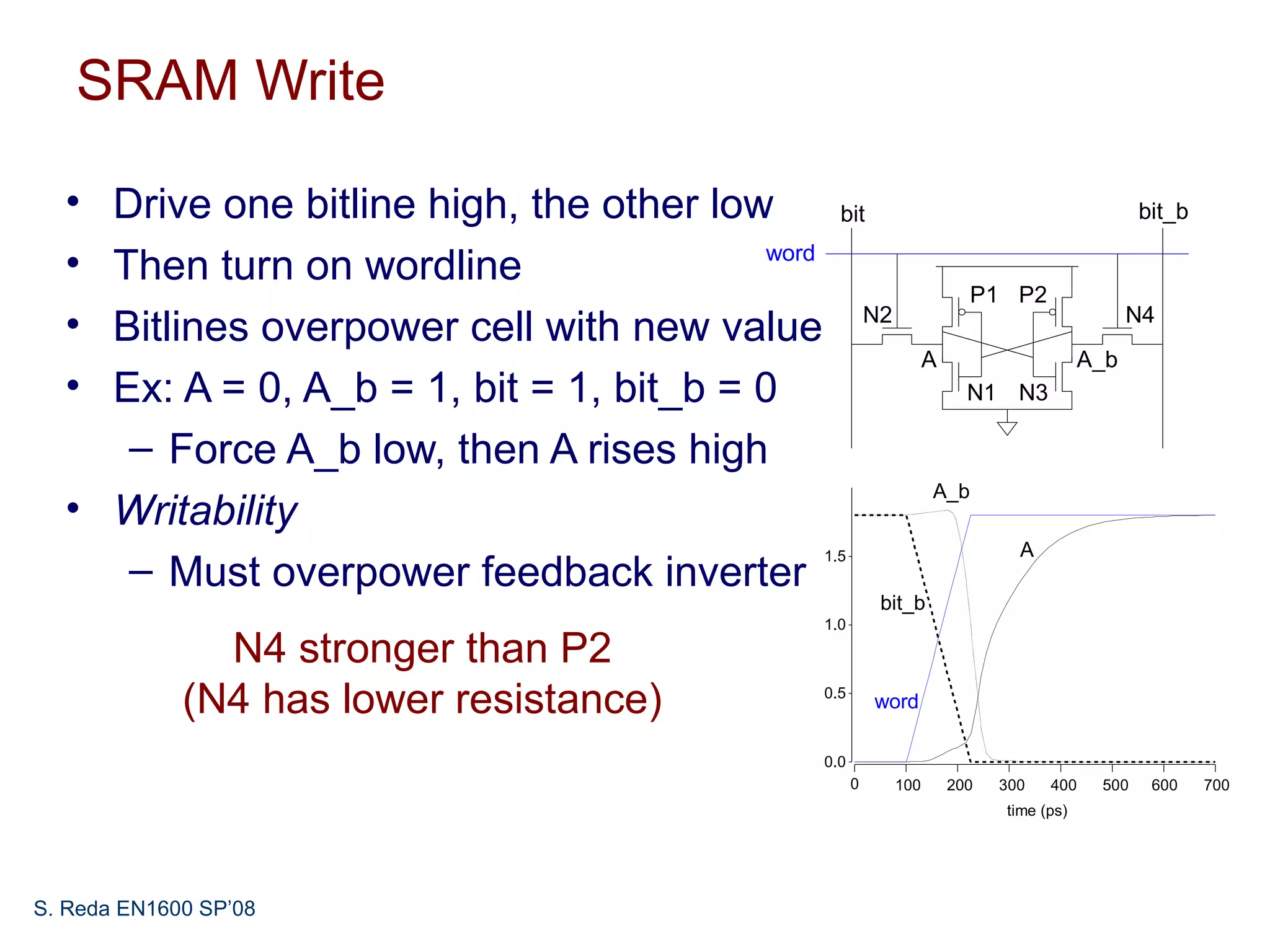

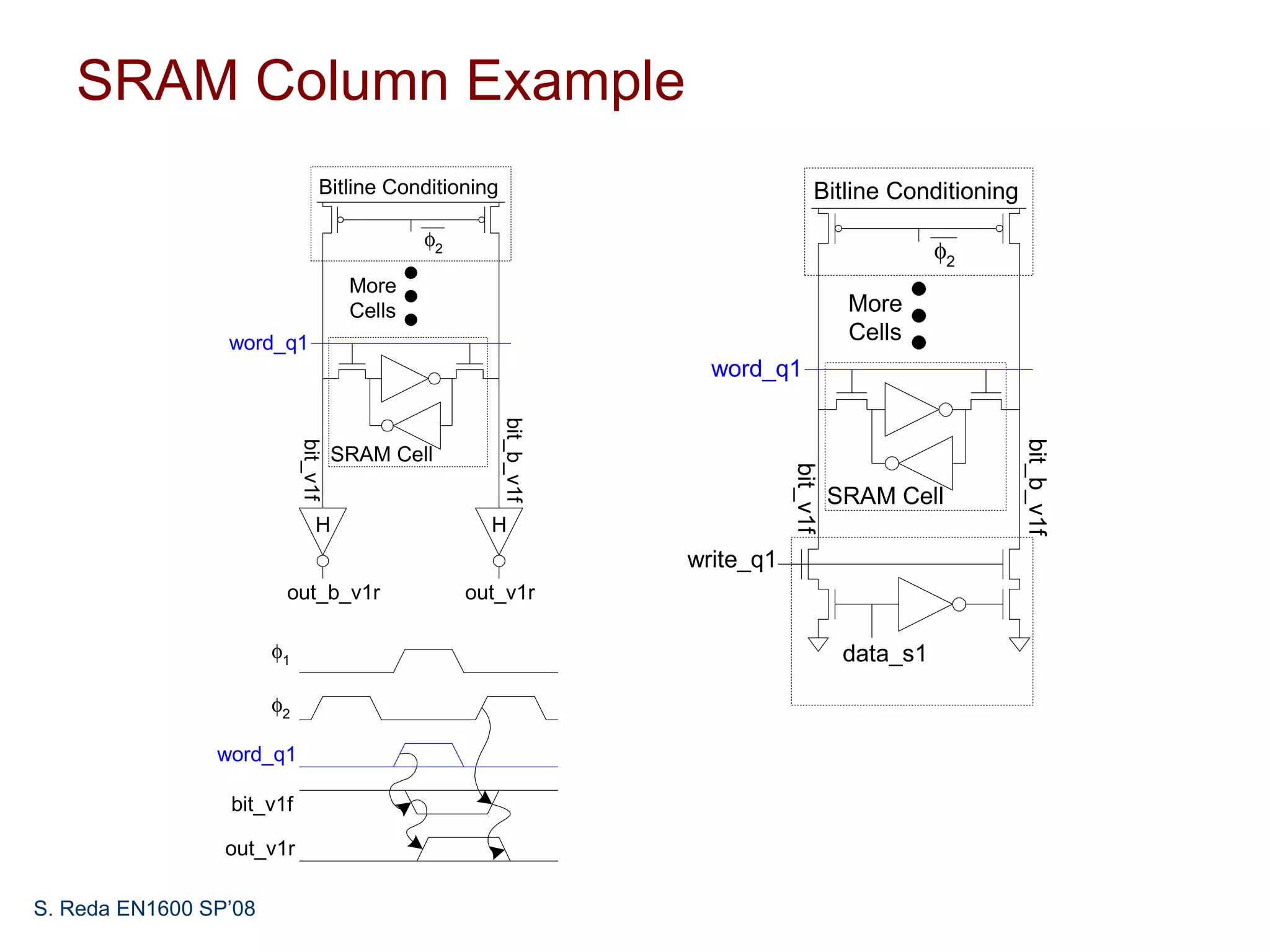

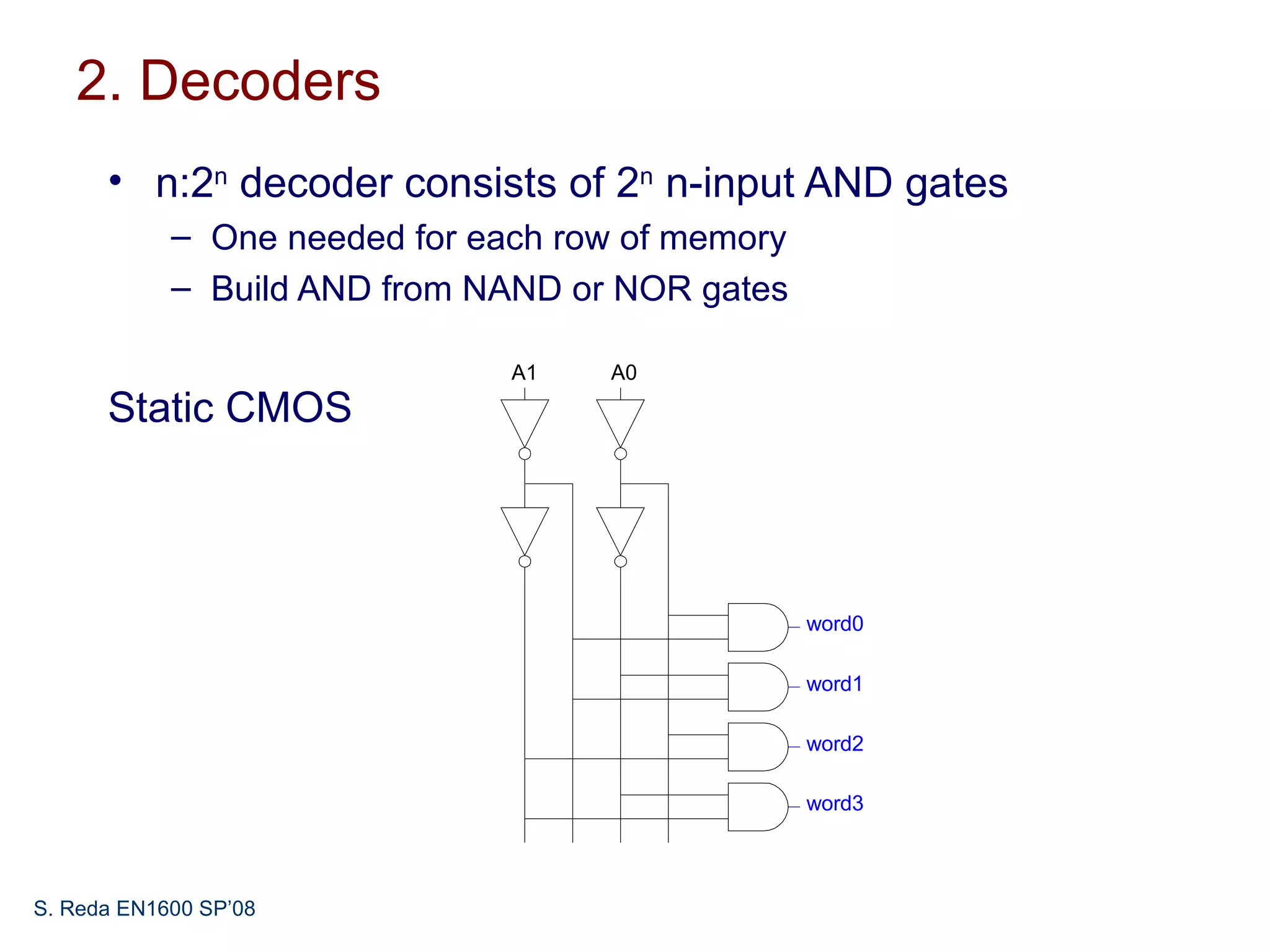

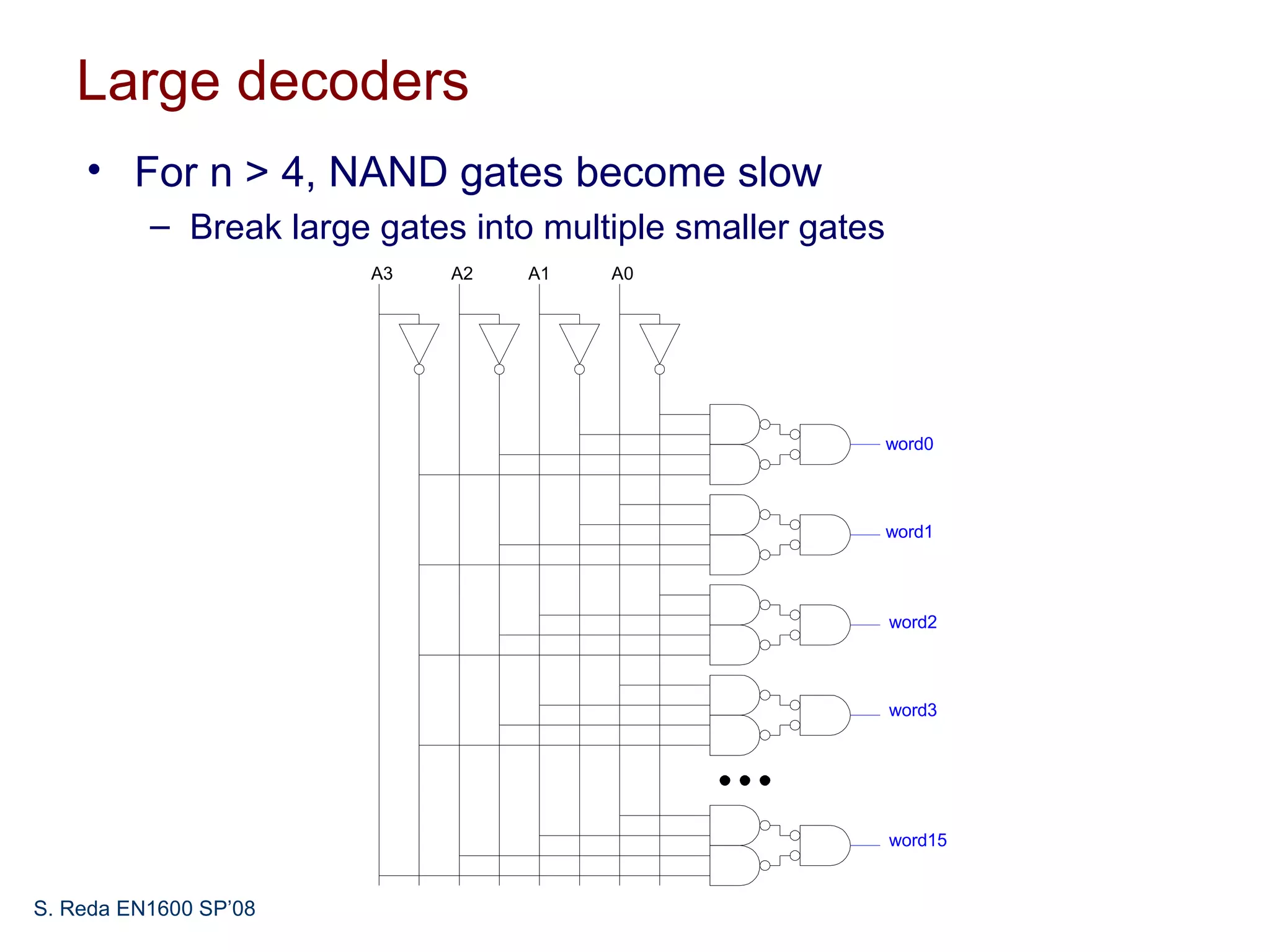

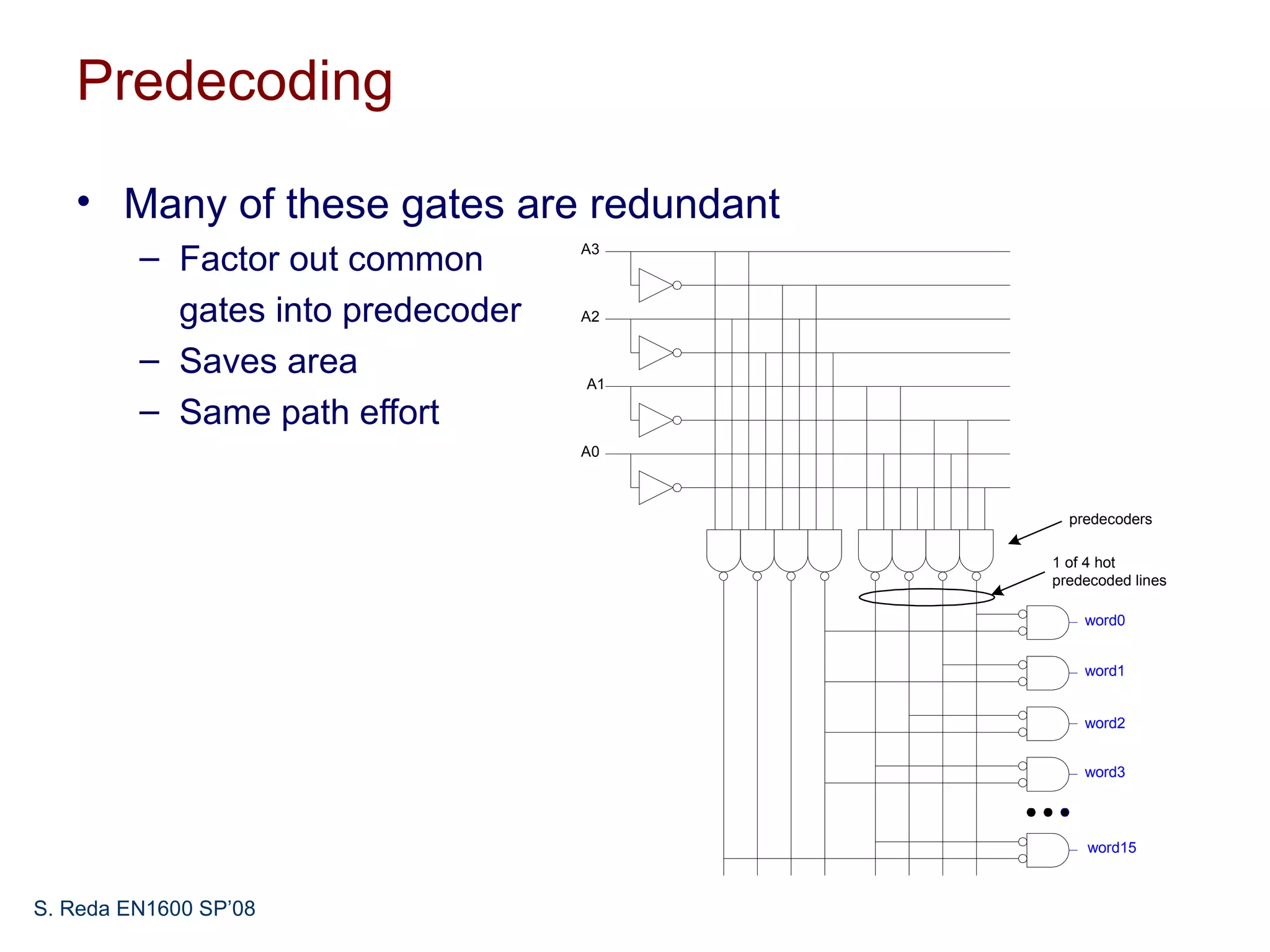

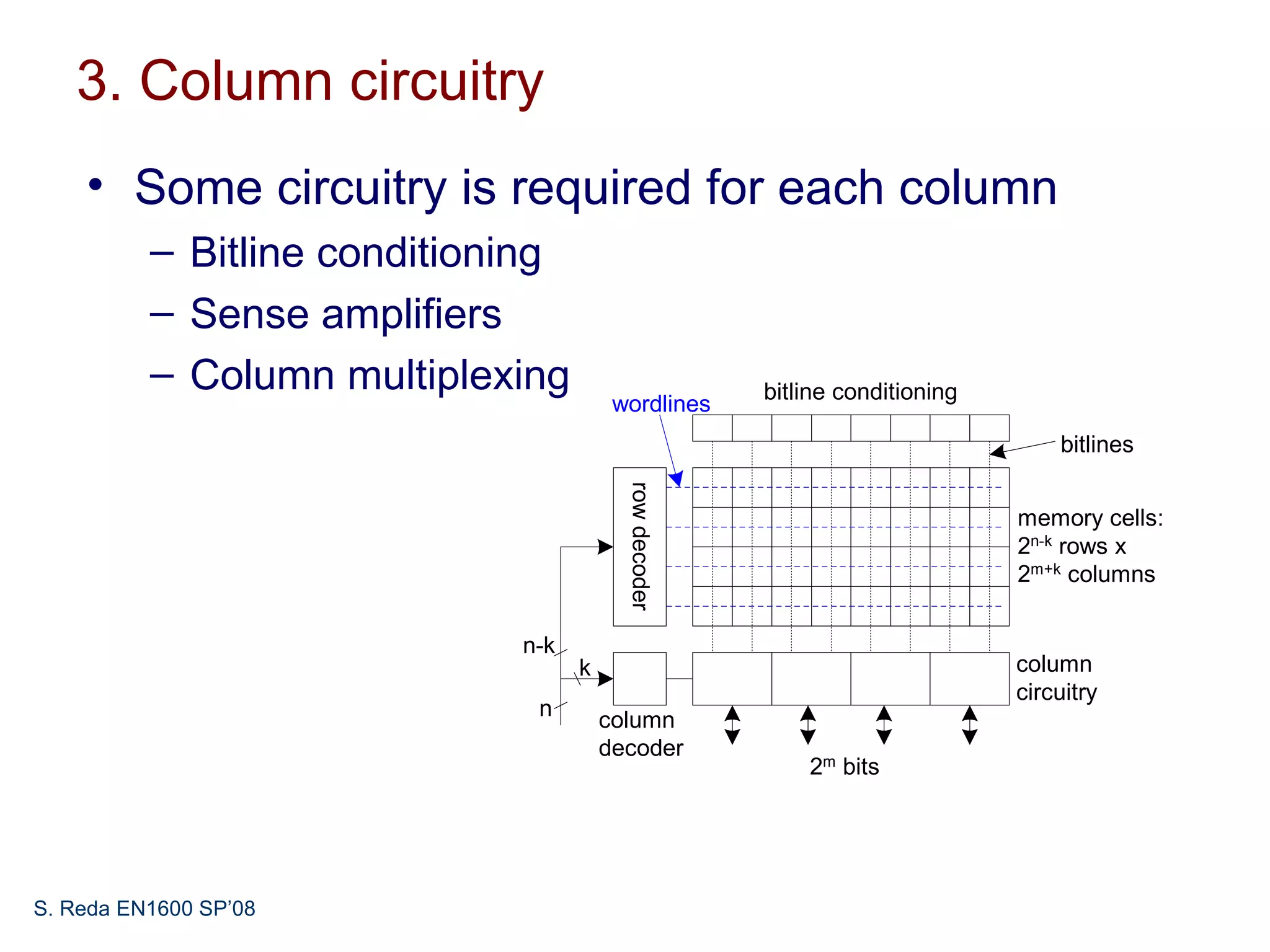

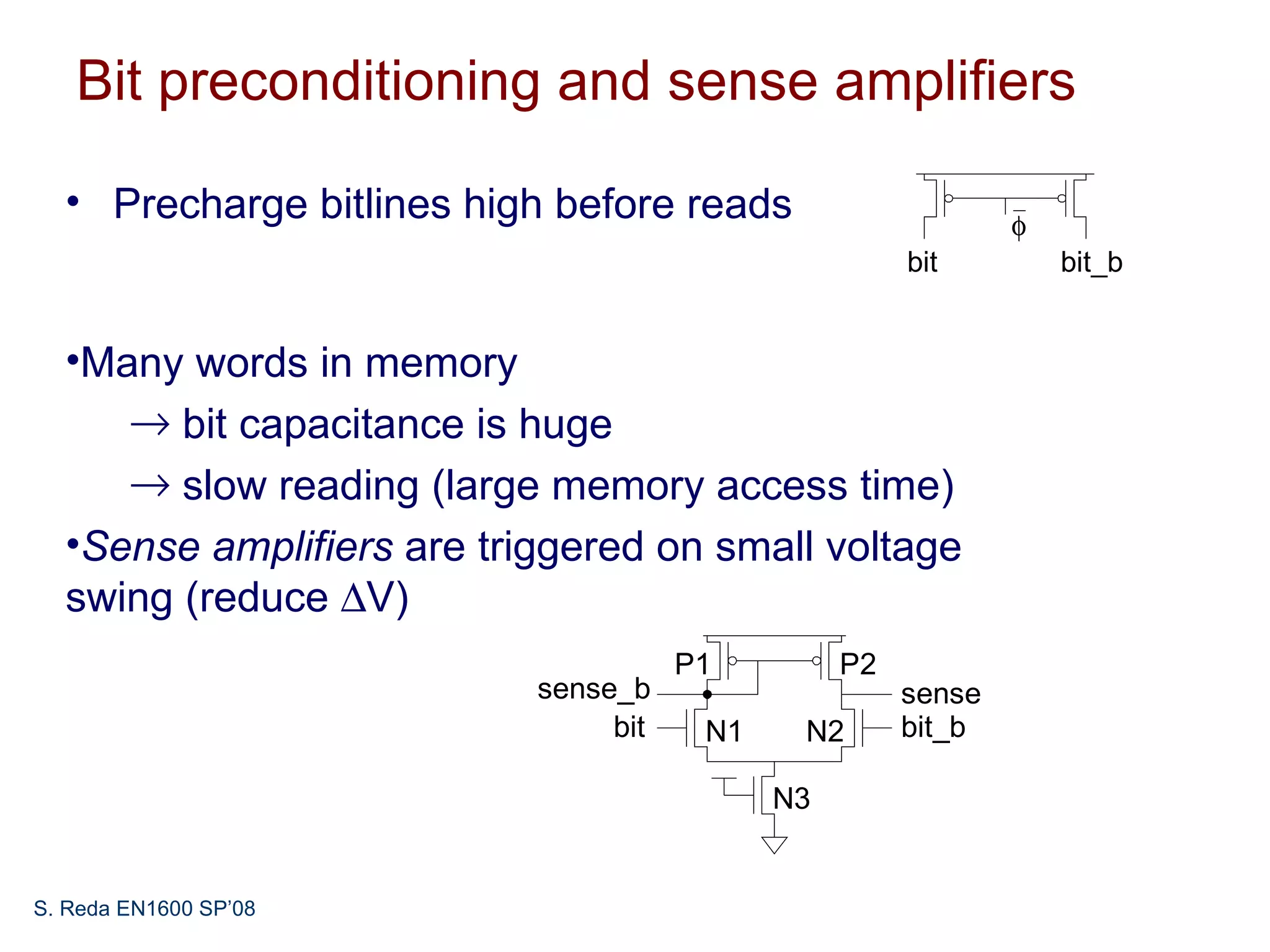

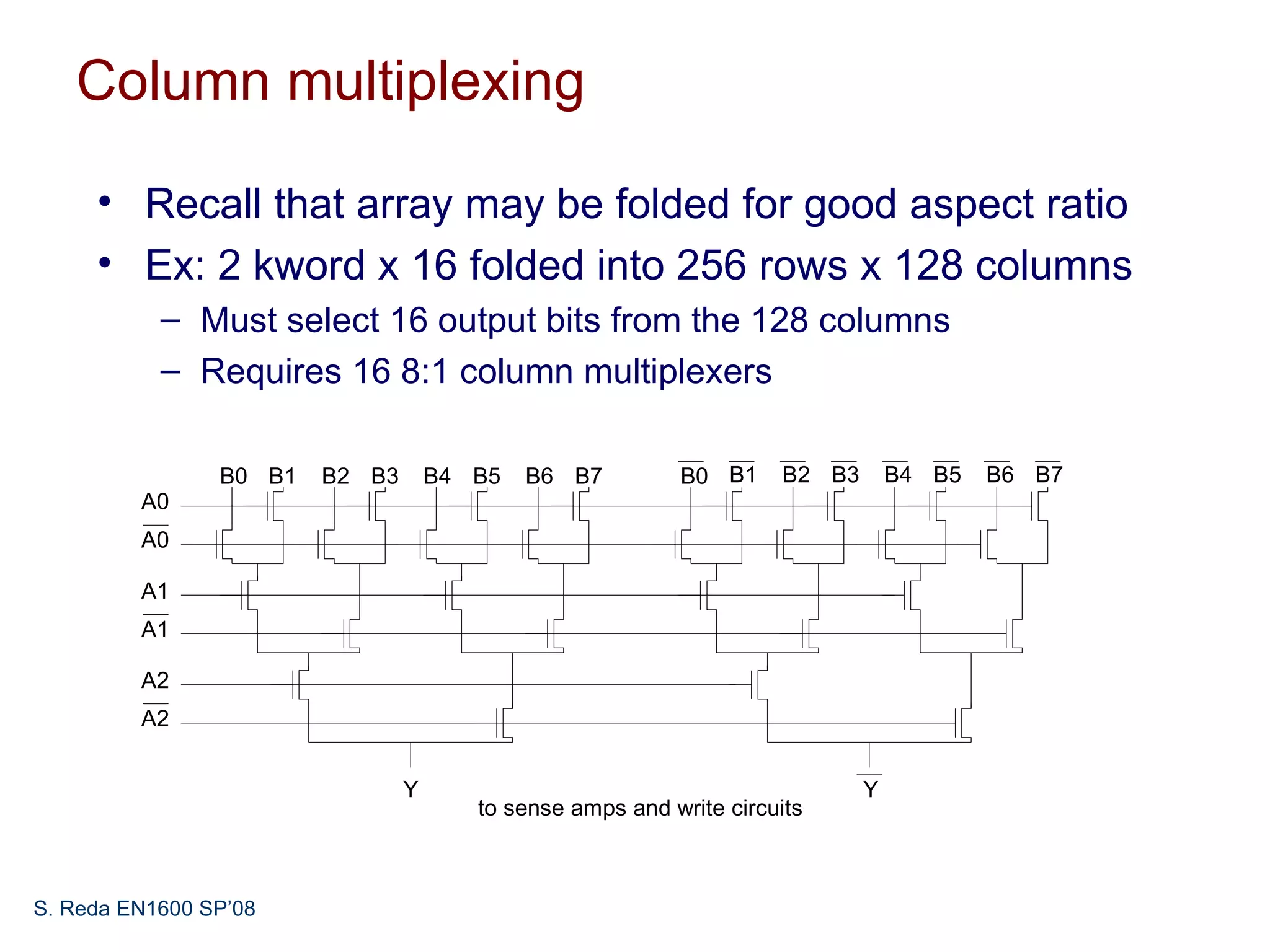

This document discusses the design and implementation of SRAM array subsystems. It covers the basic SRAM cell, including 6T and 12T cells. It describes the operation of reading and writing to SRAM cells. The document also discusses SRAM array architecture, including decoders, bitline conditioning, sense amplifiers, and column multiplexing circuits. The goal is to efficiently store and access data from the SRAM array.