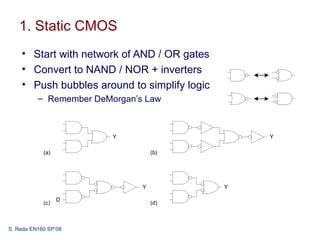

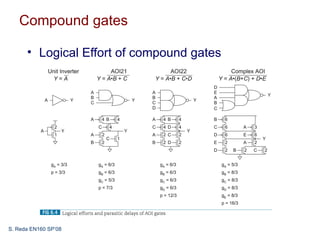

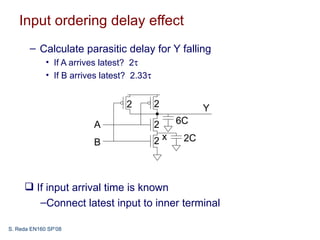

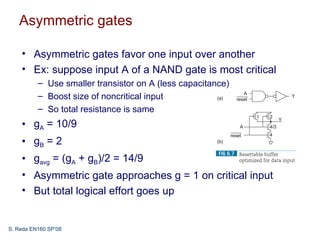

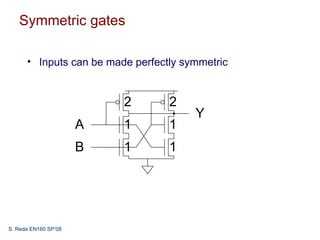

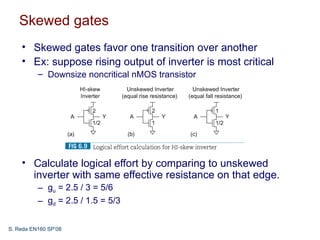

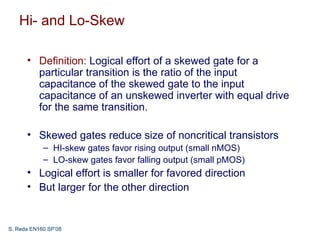

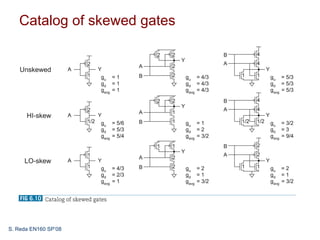

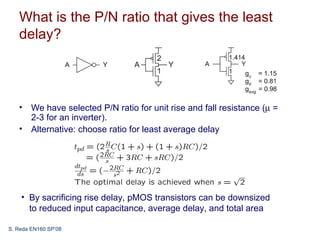

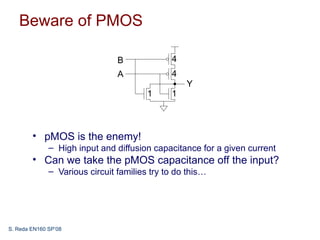

This document discusses different circuit families for combinational logic design, including static CMOS, ratioed circuits, CVSL, dynamic circuits, and pass-transistor circuits. It focuses on static CMOS, explaining how to simplify logic using DeMorgan's laws and discussing the effects of input ordering, asymmetric gates, symmetric gates, and skewed gates on delay. Skewed gates can reduce the size of non-critical transistors to lower input capacitance and delay by favoring one transition over the other. The document cautions that pMOS transistors contribute significantly more capacitance than nMOS.