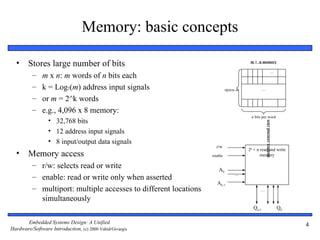

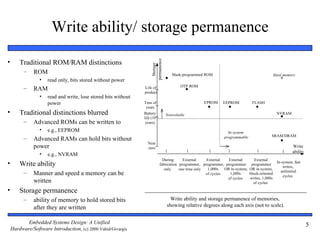

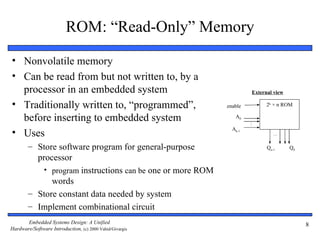

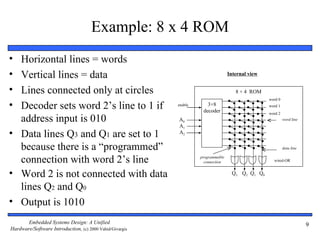

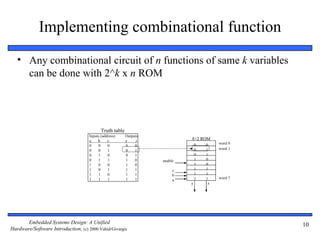

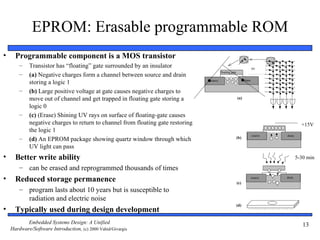

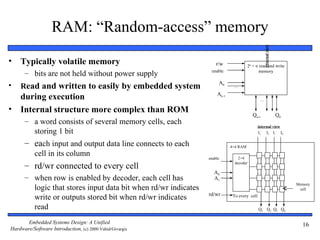

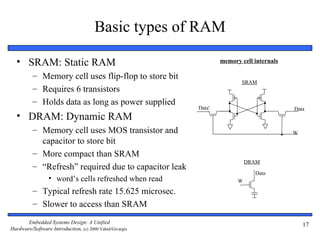

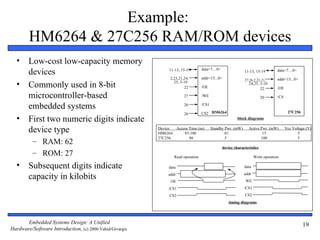

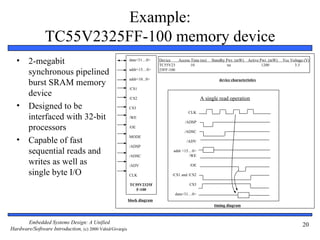

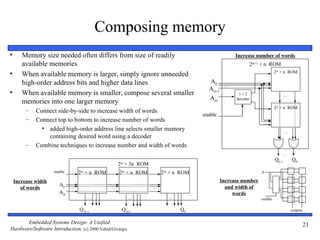

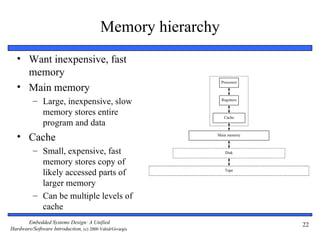

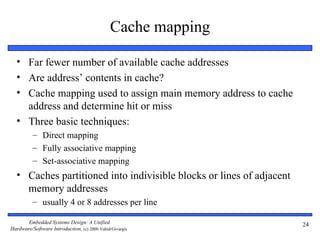

The document discusses different types of computer memory used in embedded systems. It describes the basic concepts of memory including read/write ability and storage permanence. Common memory types are described such as ROM, RAM, EEPROM, and flash memory. Details are provided on each type's write ability, storage permanence, typical uses, and example technologies. Memory hierarchy and concepts like cache are also mentioned.