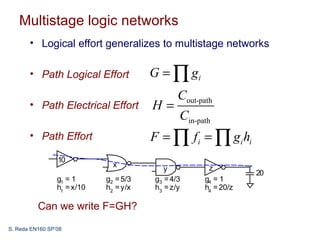

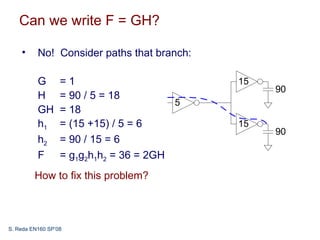

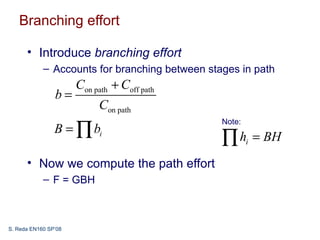

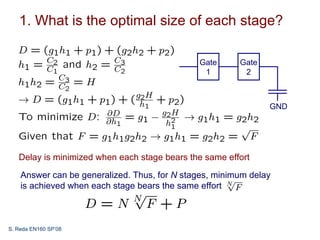

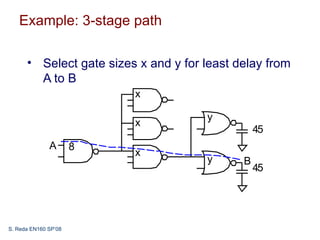

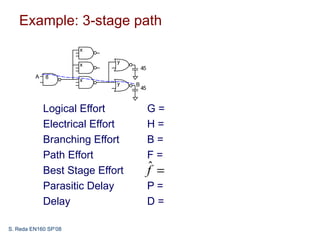

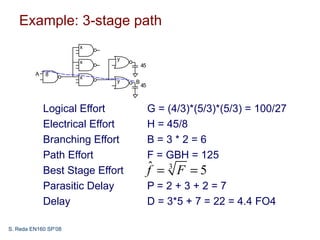

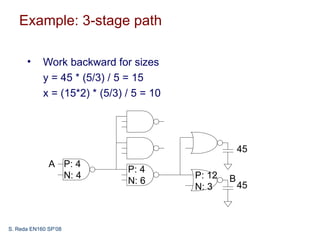

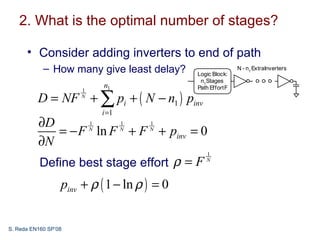

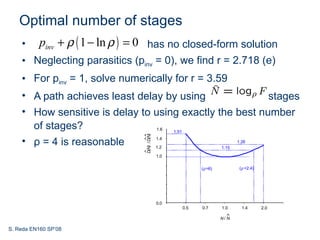

This document discusses logical effort and how it can be used to analyze multistage logic networks. It explains that logical effort can be generalized to account for branching in multistage paths. When branching is considered, the path effort is equal to the product of logical effort, electrical effort, and branching effort. Logical effort analysis can also be used to determine the optimal size of each stage and number of stages to minimize delay in a multistage network.