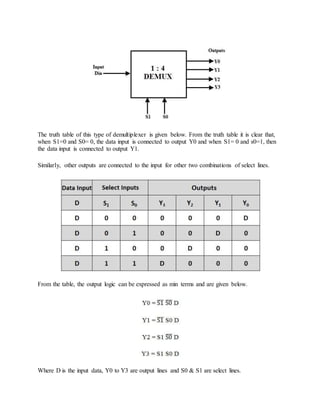

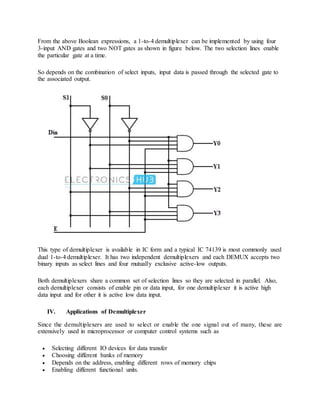

The document provides a comprehensive overview of a 1:4 demultiplexer, detailing its function as a device that routes a single input to one of four outputs based on selection lines. It includes descriptions of various configurations, applications such as memory selection in computer systems, and provides VHDL code examples for implementation. Additionally, it highlights commonly used integrated circuits (ICs) and the operational principles of demultiplexers.