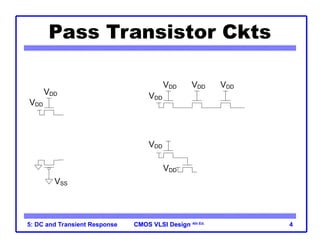

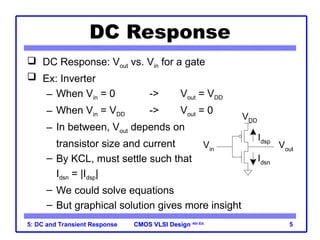

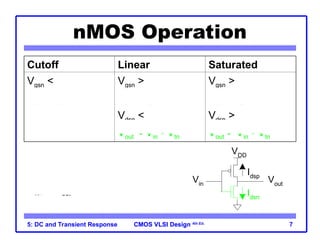

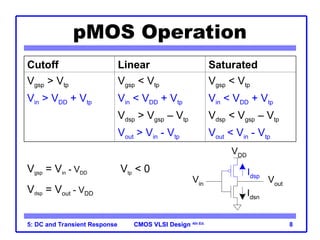

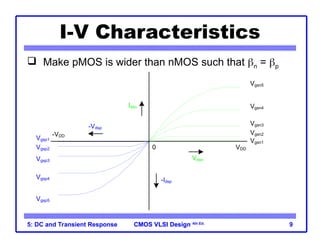

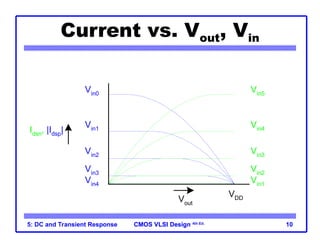

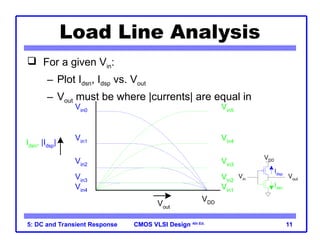

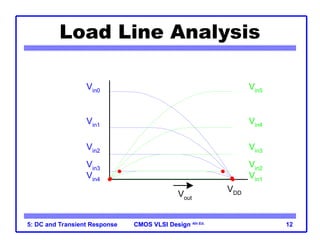

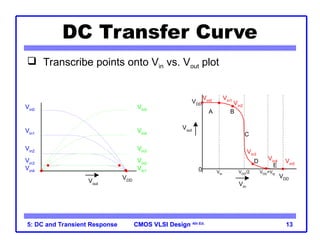

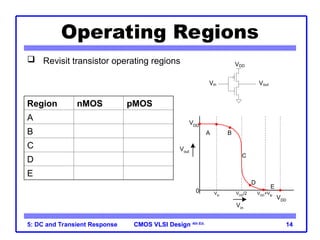

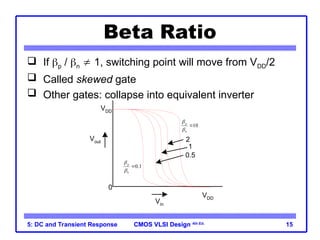

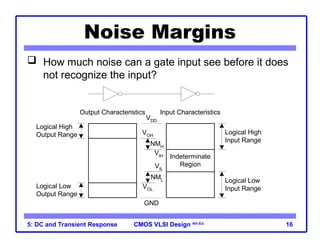

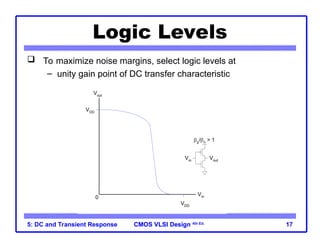

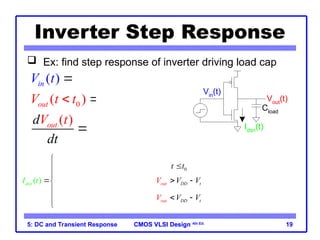

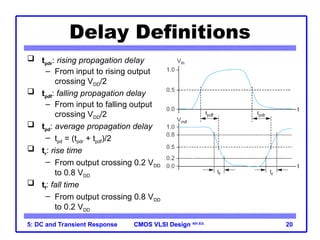

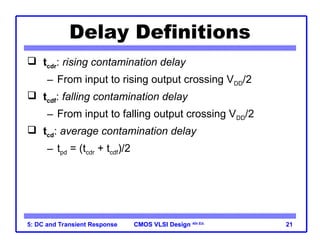

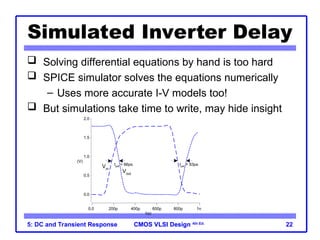

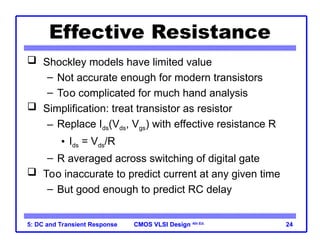

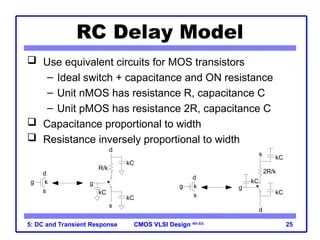

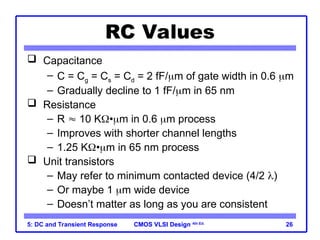

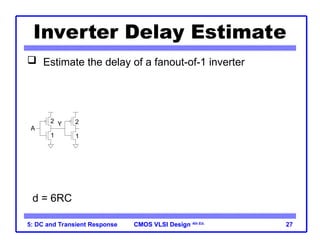

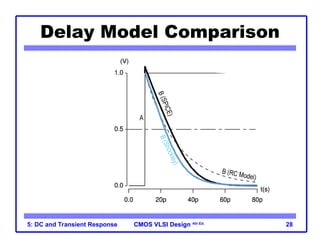

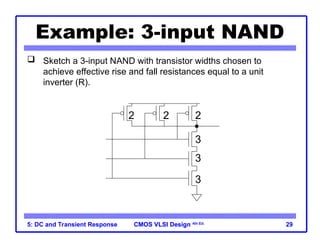

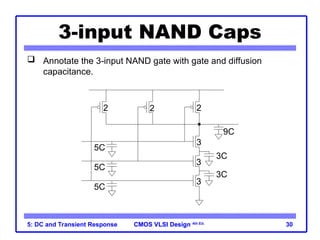

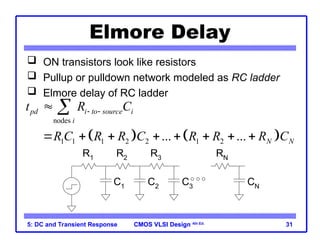

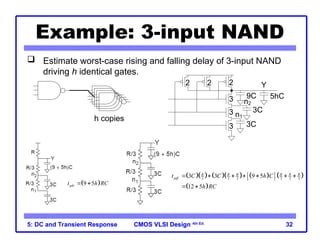

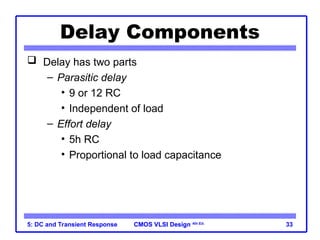

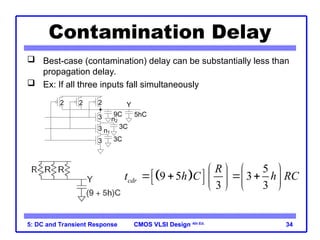

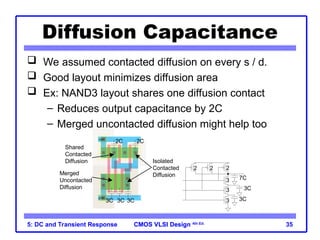

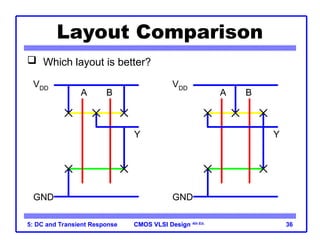

The document outlines the DC and transient response in CMOS VLSI design, focusing on pass transistors, DC response characteristics like logic levels, noise margins, and transient analysis for different operating regions of NMOS and PMOS transistors. It covers core concepts including I-V characteristics, delay estimation, and load line analysis, alongside more complex topics like effective resistance and Elmore delay for circuit modeling. Practical examples illustrate the estimation of delays in inverter and NAND gate designs.