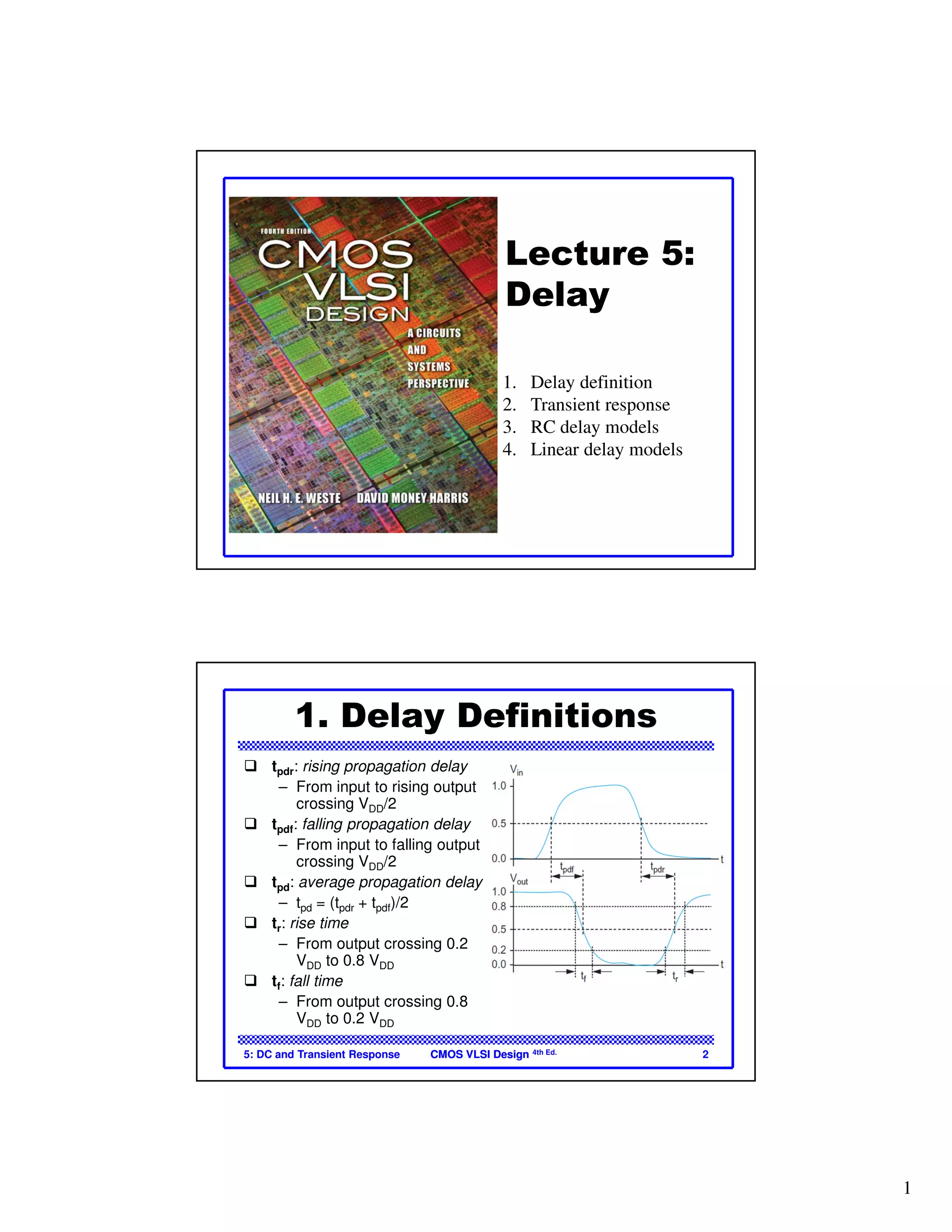

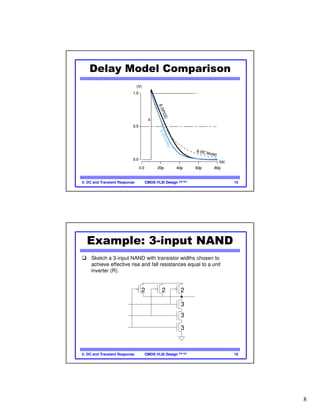

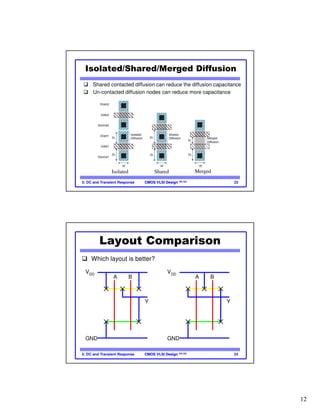

This document discusses delay modeling and analysis in CMOS VLSI circuits. It defines various delay metrics like propagation delay, rise/fall times, and contamination delay. RC delay models are presented to estimate delay where transistors are modeled as resistors and capacitances. Logical effort and parasitic delay linear models are also introduced for estimating gate delays based on their structure and fanout. Elmore delay calculations and minimizing diffusion capacitance through layout are covered as techniques for analyzing transient response and optimizing speed.