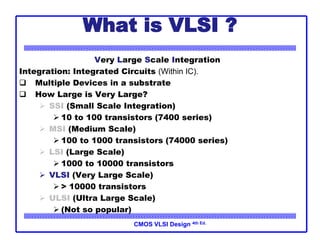

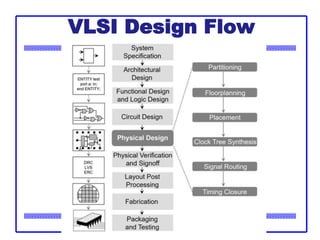

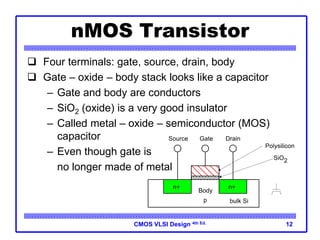

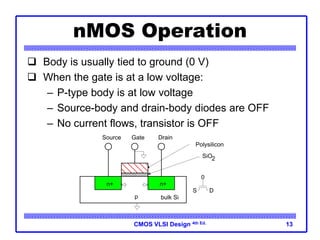

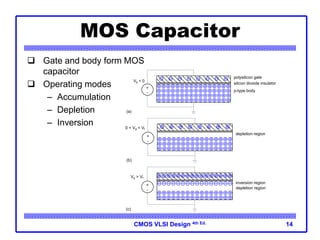

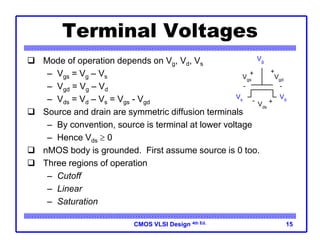

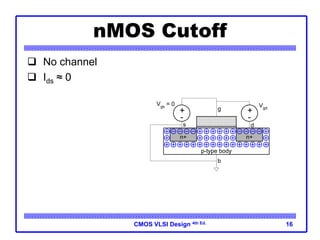

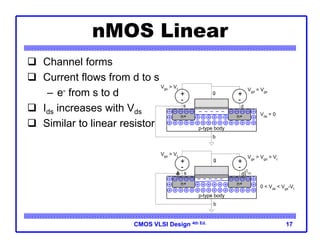

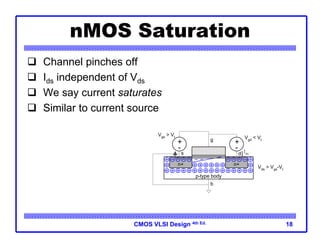

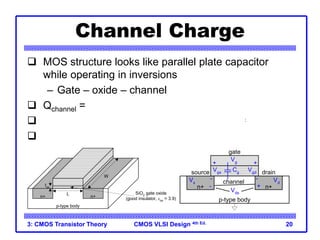

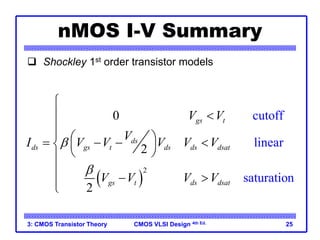

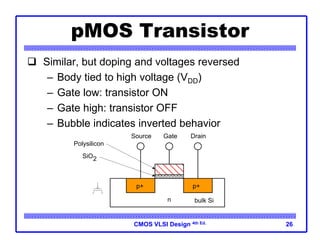

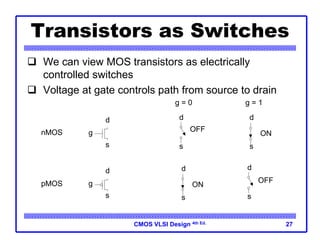

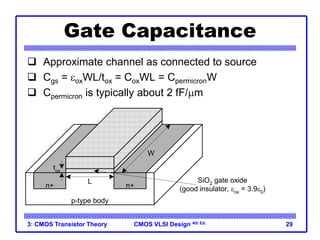

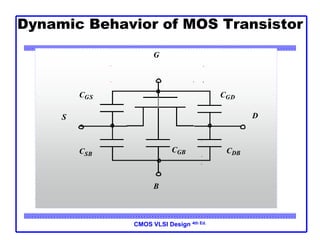

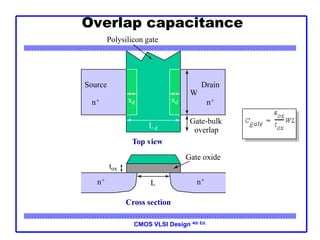

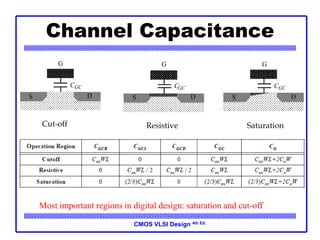

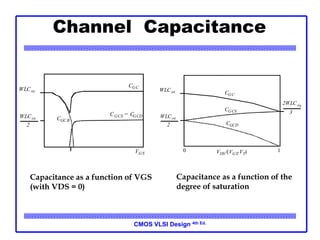

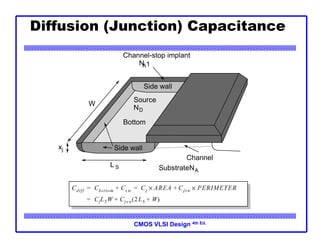

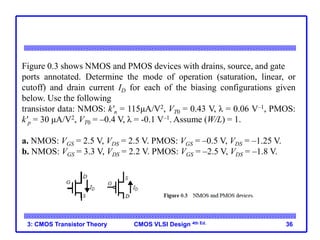

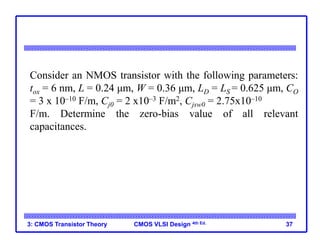

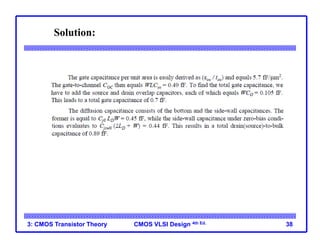

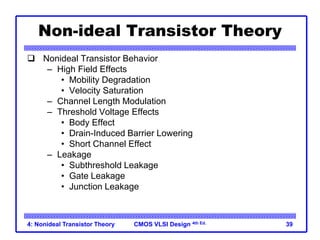

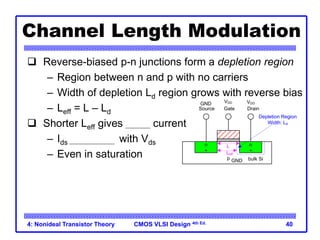

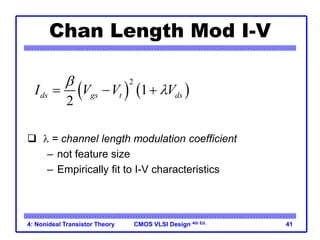

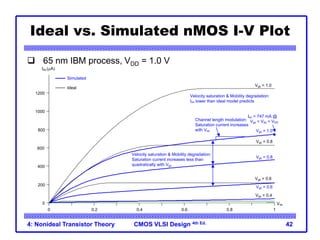

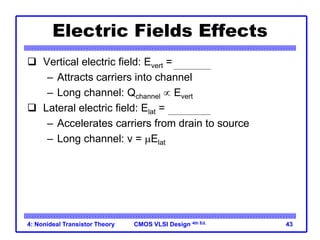

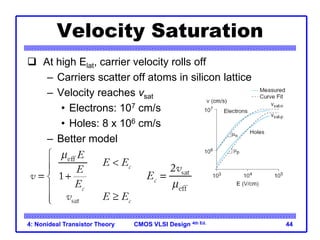

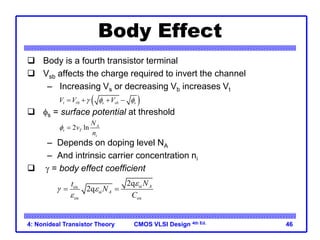

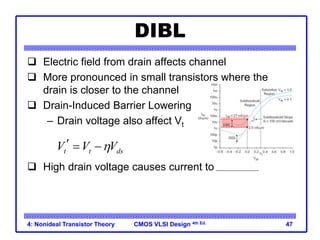

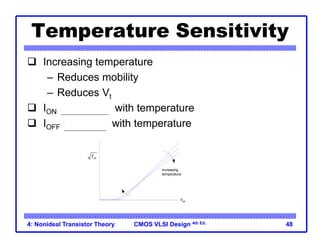

This document discusses CMOS VLSI design and transistor theory. It begins with an introduction to VLSI and the different scales of integration. It then covers MOSFET operation and I-V characteristics in cutoff, linear, and saturation regions. The document discusses capacitance components of MOS transistors including gate, diffusion, overlap, and channel capacitances. It also summarizes non-ideal transistor effects such as mobility degradation, velocity saturation, channel length modulation, and threshold voltage variations.