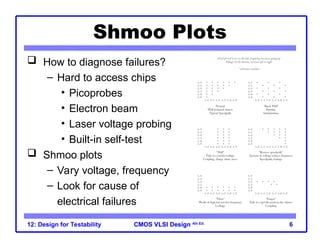

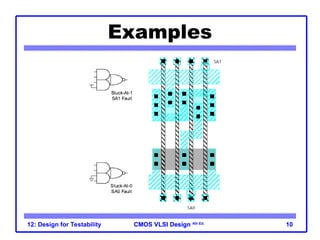

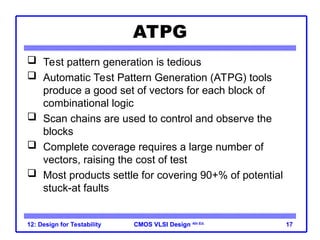

The document discusses design for testability in CMOS VLSI design, emphasizing the importance of testing throughout the design process. It covers various topics such as testing strategies, fault models, and methodologies like scan and built-in self-test to enhance observability and controllability. The document concludes with the necessity of planning for testing from the beginning to ensure functionality post-fabrication.

![CMOS VLSI Design

CMOS VLSI Design 4th Ed.

12: Design for Testability 19

PRSG

Linear Feedback Shift Register

– Shift register with input taken from XOR of state

– Pseudo-Random Sequence Generator

Flop

Flop

Flop

Q[0] Q[1] Q[2]

CLK

D D D

Step Y

0 111

1 110

2 101

3 010

4 100

5 001

6 011

7 111 (repeats)

Flops reset to 111

Y](https://image.slidesharecdn.com/lect12-test-240914095716-03c7c86d/85/Test-generation-in-VLSI-design-and-Testing-19-320.jpg)

![CMOS VLSI Design

CMOS VLSI Design 4th Ed.

12: Design for Testability 20

BILBO

Built-in Logic Block Observer

– Combine scan with PRSG & signature analysis

MODE C[1] C[0]

Scan 0 0

Test 0 1

Reset 1 0

Normal 1 1

Flop

Flop

Flop

1

0

D[0] D[1] D[2]

Q[0]

Q[1]

Q[2] / SO

SI

C[1]

C[0]

PRSG

Logic

Cloud

Signature

Analyzer](https://image.slidesharecdn.com/lect12-test-240914095716-03c7c86d/85/Test-generation-in-VLSI-design-and-Testing-20-320.jpg)