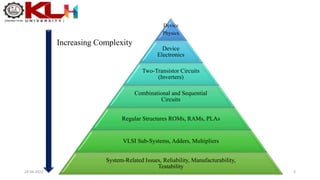

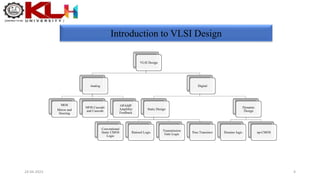

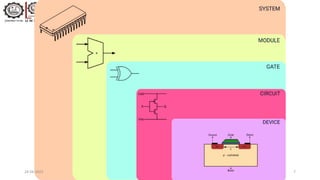

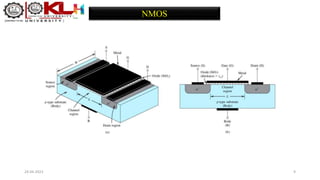

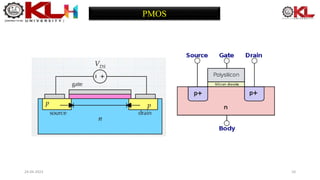

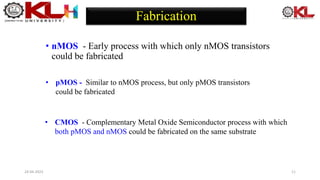

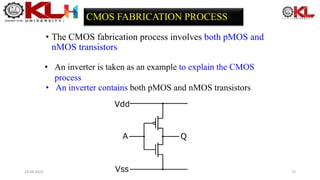

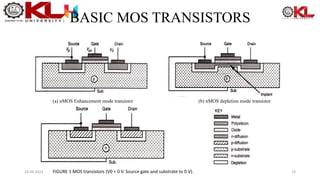

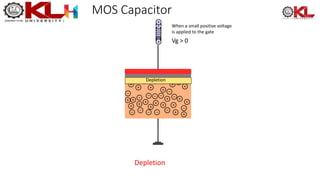

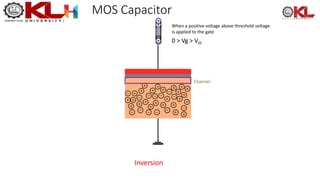

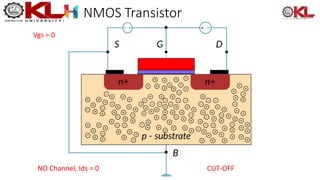

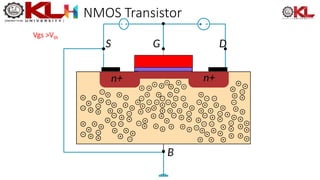

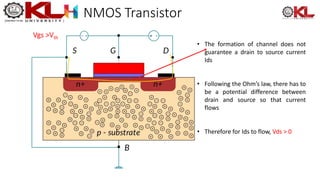

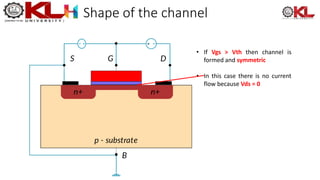

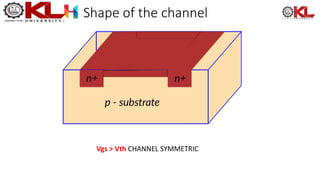

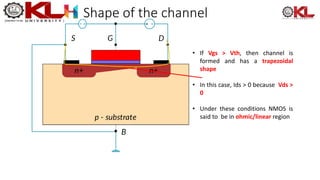

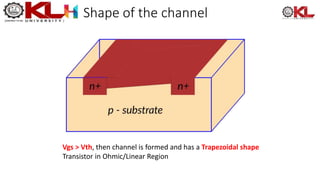

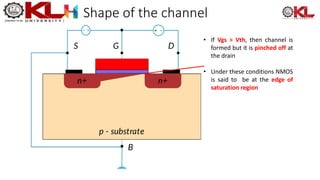

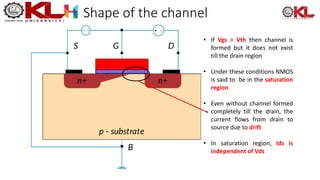

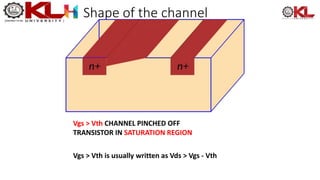

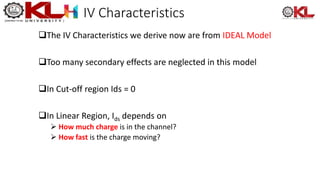

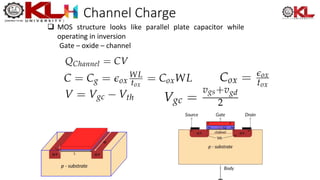

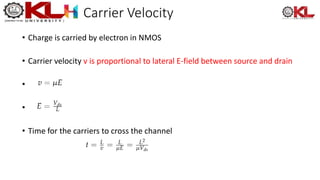

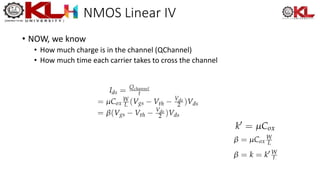

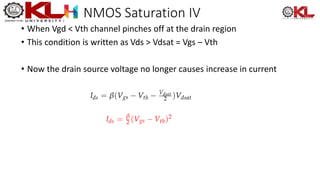

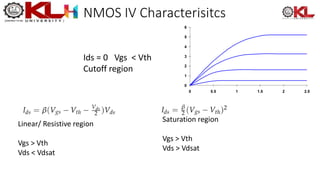

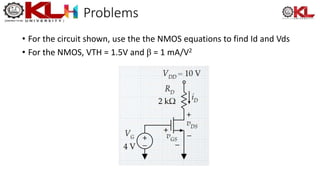

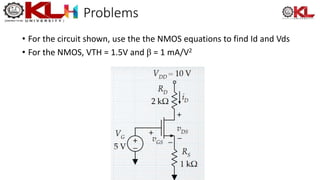

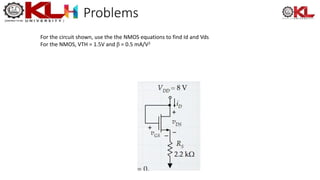

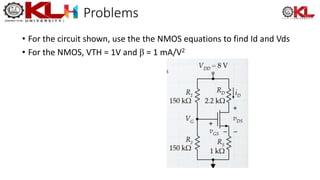

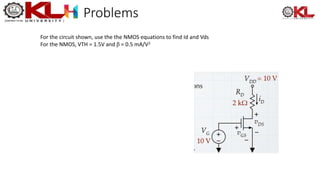

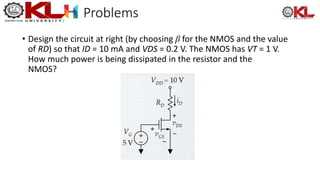

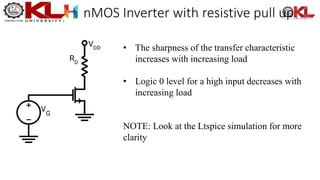

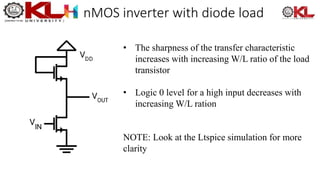

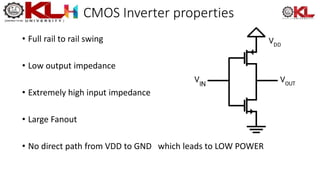

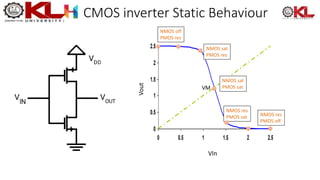

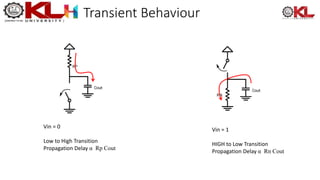

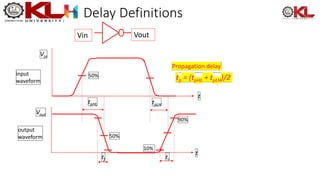

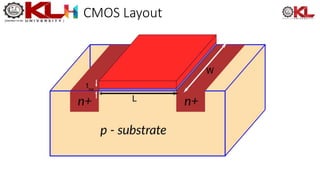

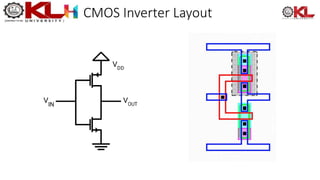

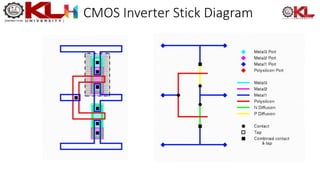

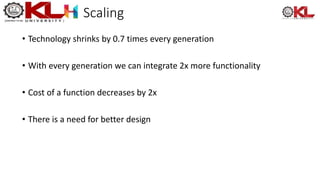

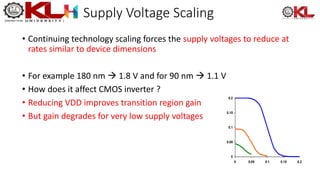

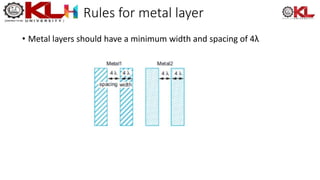

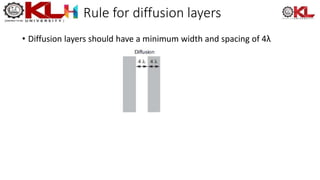

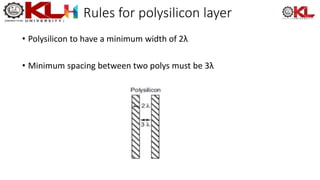

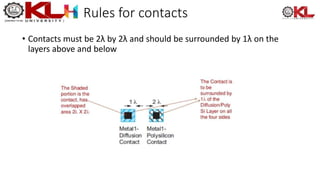

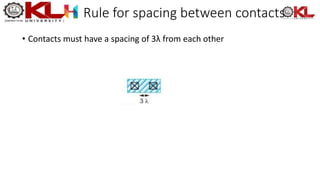

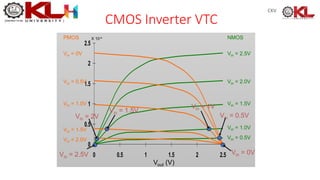

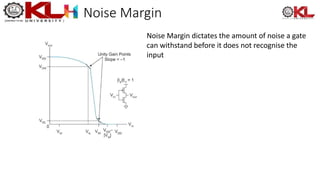

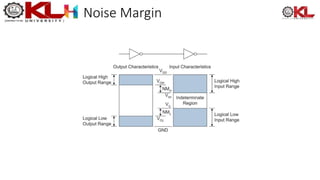

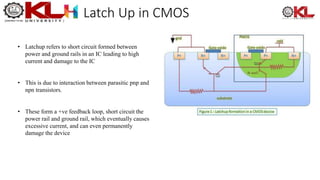

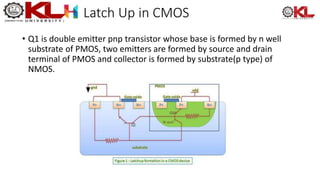

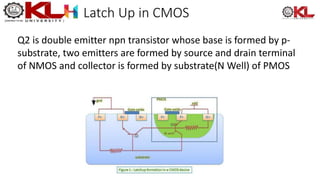

The document discusses VLSI design fundamentals with a focus on MOS transistor analysis, integrated circuits advantages, and design abstraction levels. It covers fabrication processes for NMOS, PMOS, and CMOS technologies, and explores concepts like inverter behavior, logic design, and layout design rules. Additionally, it addresses issues such as latch-up phenomena in CMOS and the impacts of technology scaling on performance and power consumption.