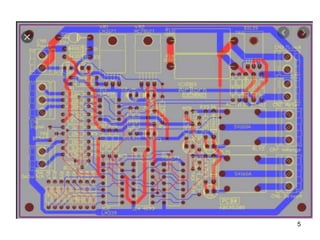

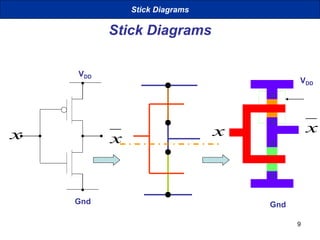

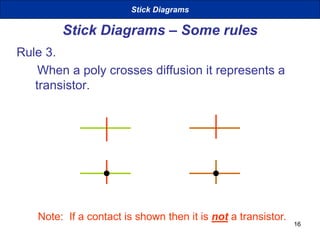

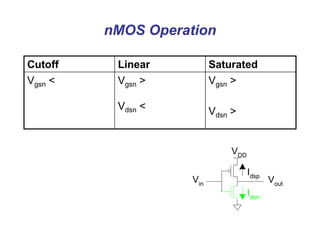

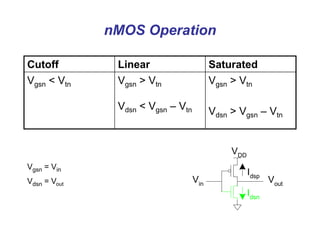

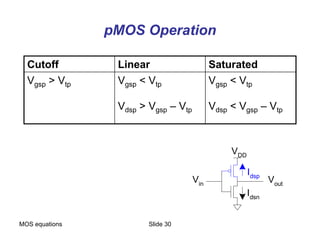

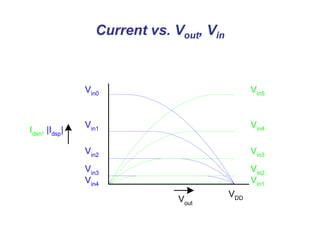

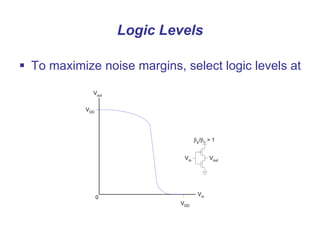

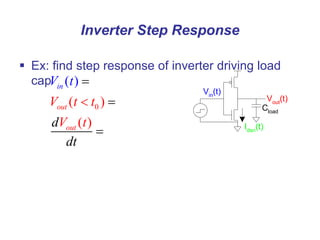

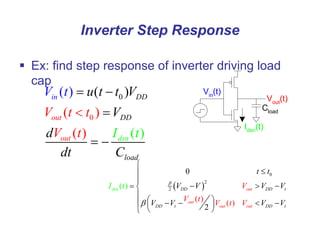

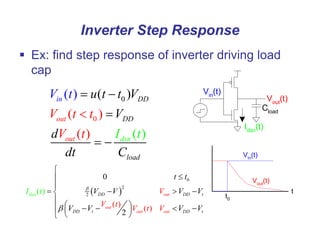

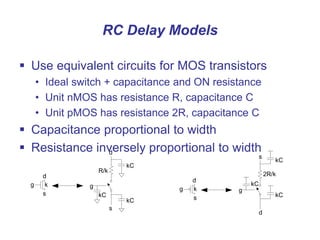

This document presents a comprehensive overview of MOS and BiCMOS circuit design processes as part of a VLSI design course at Gitam University, focusing on stick diagrams, circuit concepts, and various MOS characteristics. Key topics include stick diagram rules, transistor operations, DC transfer curves, noise margins, delay definitions, and methods for estimating delays in circuits. The document serves as a foundational resource for students to understand VLSI design principles and methodologies.