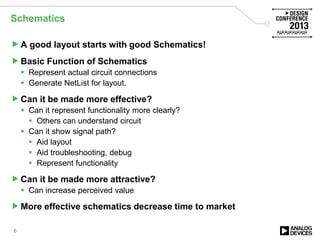

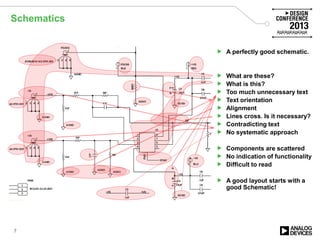

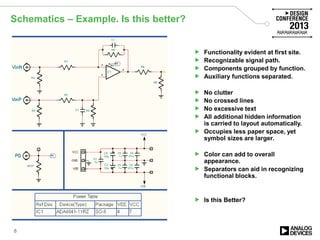

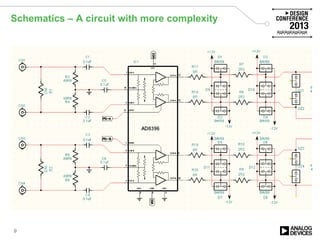

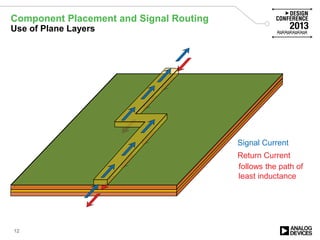

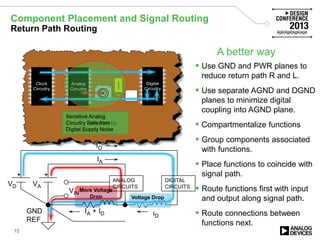

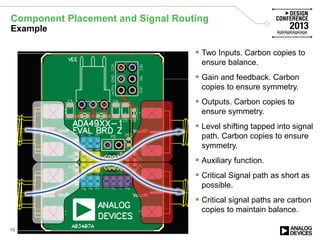

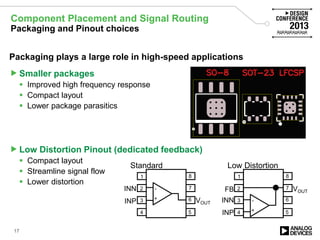

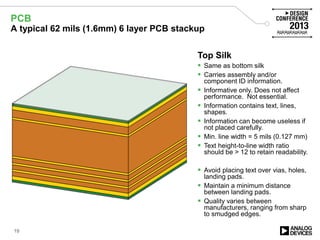

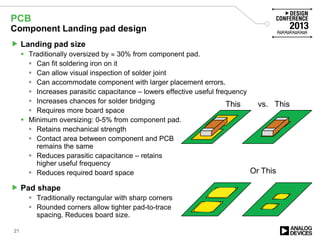

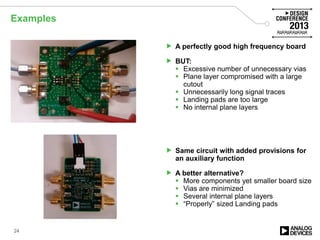

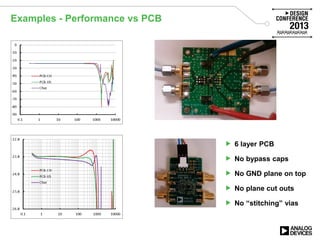

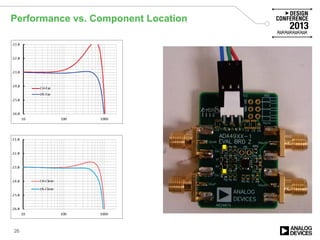

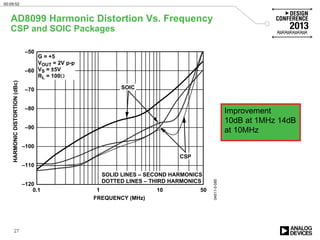

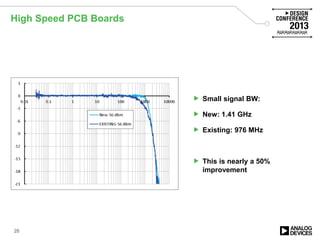

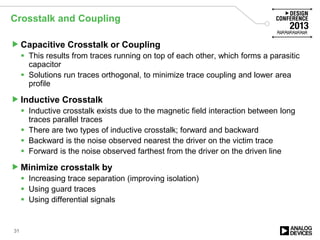

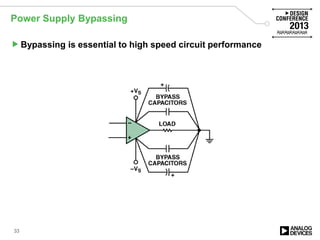

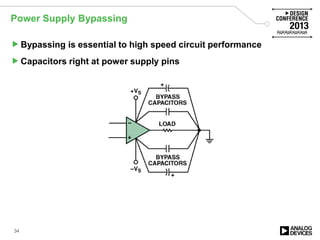

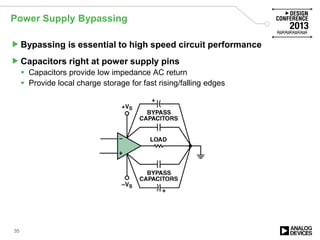

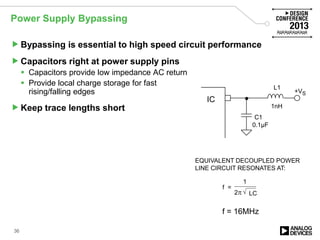

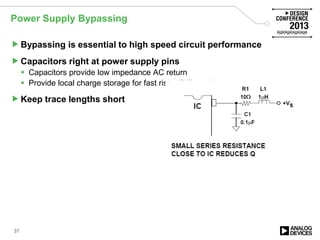

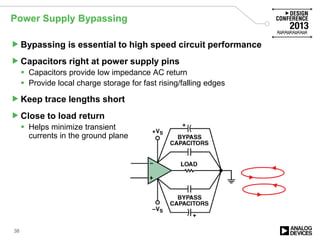

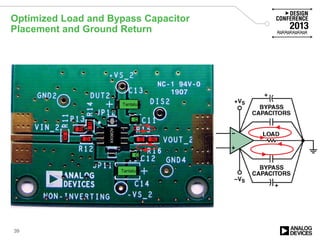

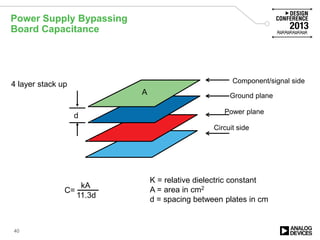

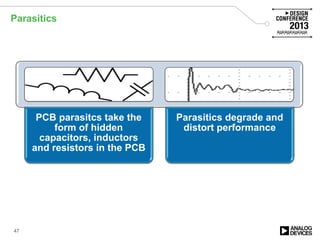

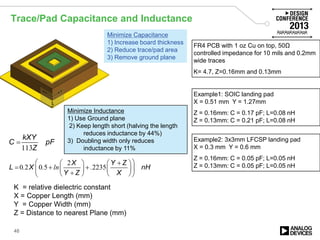

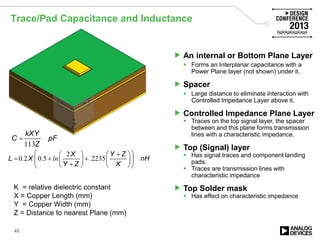

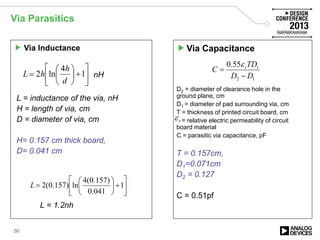

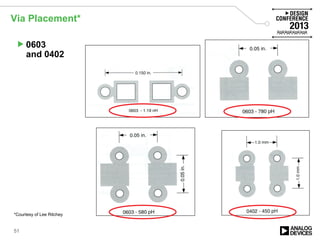

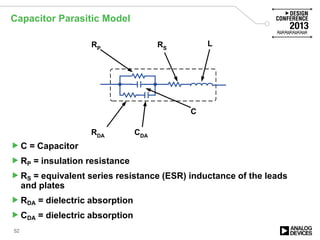

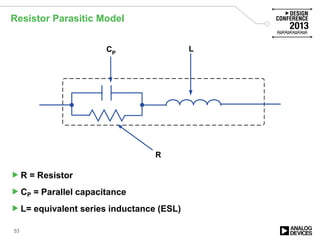

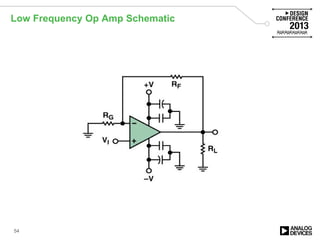

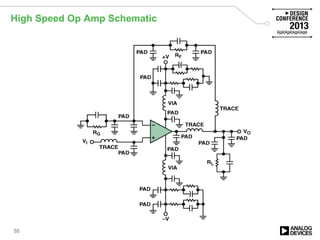

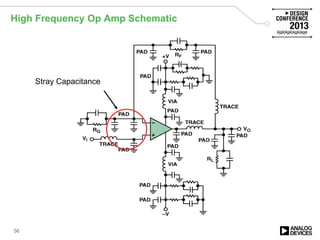

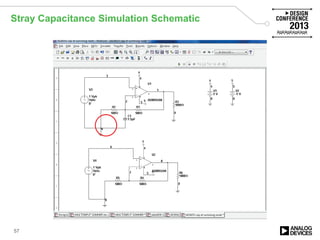

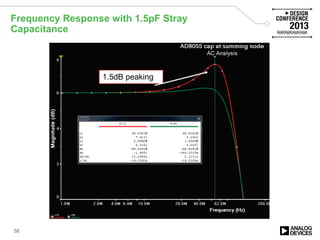

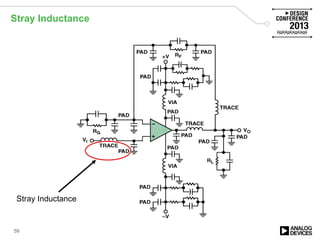

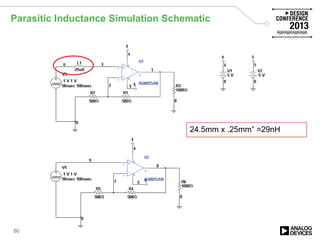

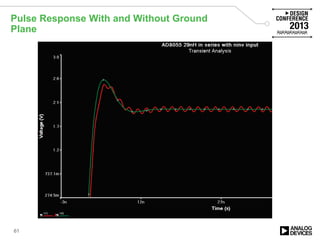

The document provides guidelines and techniques for high-speed PCB design, emphasizing proper component placement, signal routing, and power supply bypassing to enhance circuit performance. It discusses the importance of effective schematics, the selection of materials, and considerations for minimizing parasitics and crosstalk. Additionally, it covers legal disclaimers regarding the proprietary nature of the content and lists a structured agenda outlining the key topics addressed.