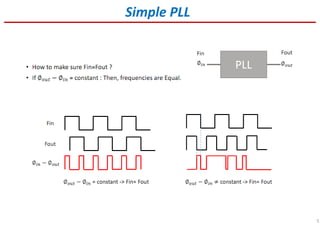

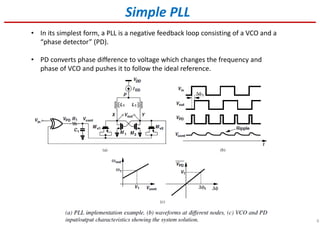

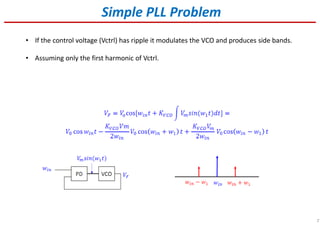

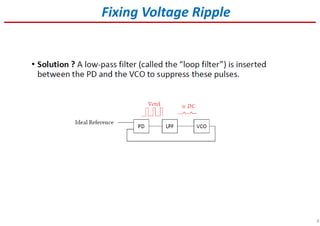

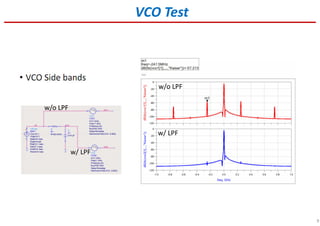

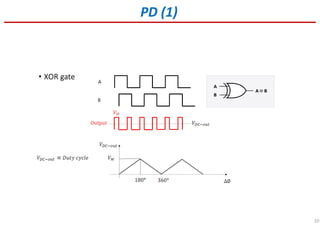

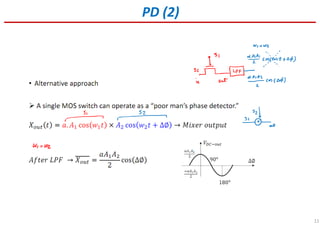

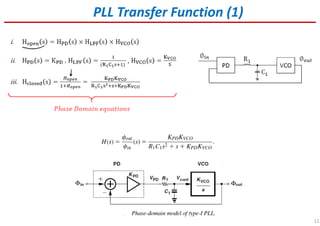

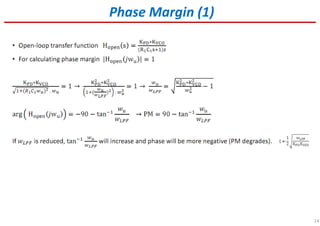

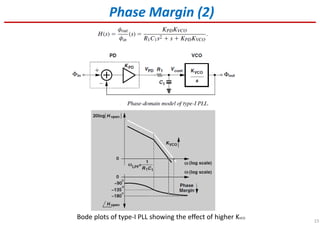

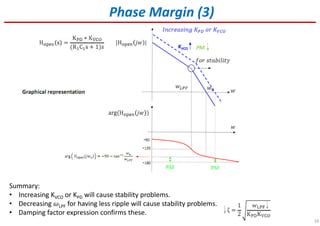

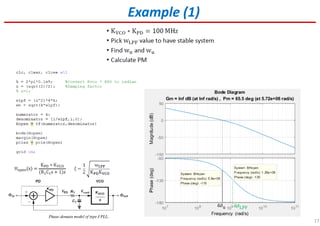

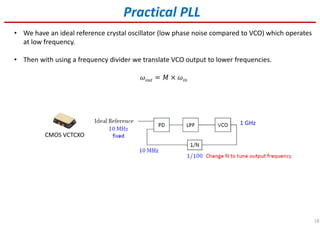

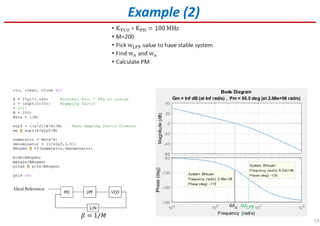

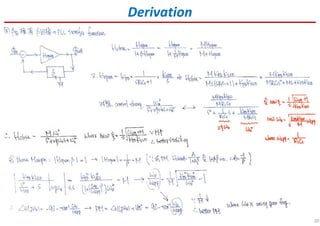

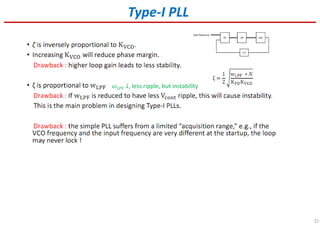

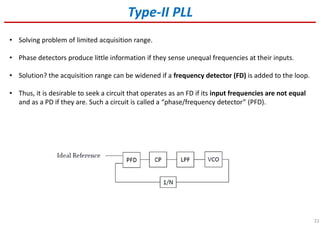

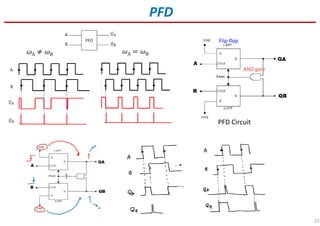

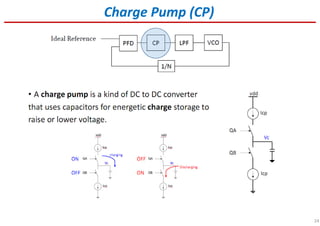

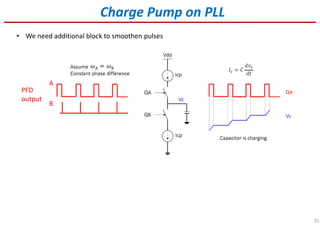

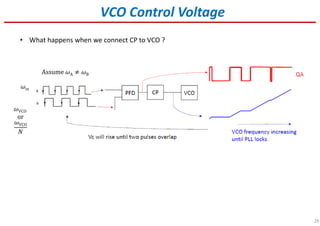

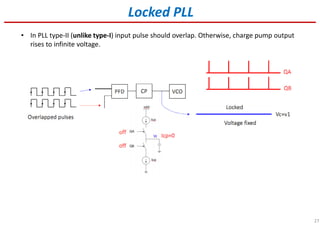

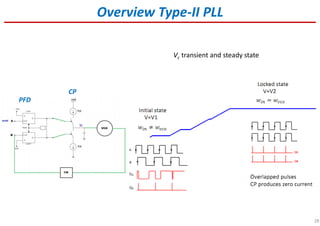

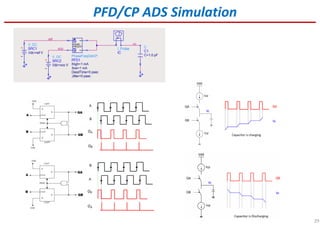

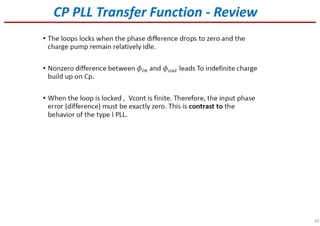

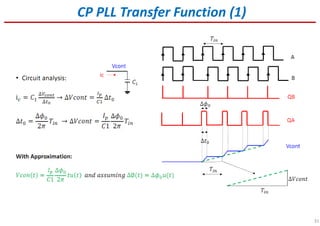

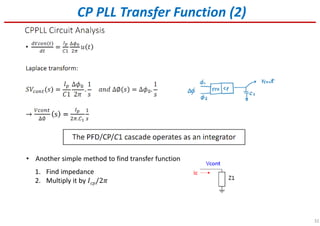

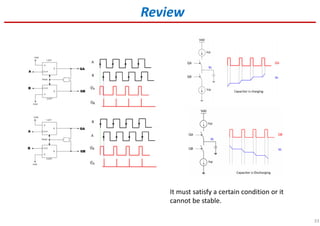

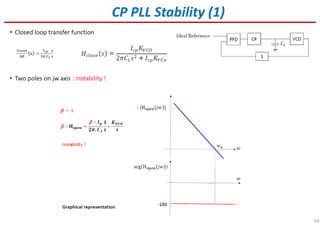

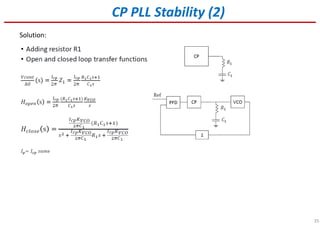

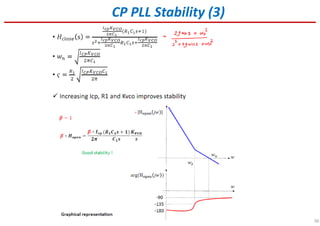

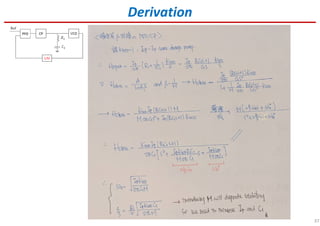

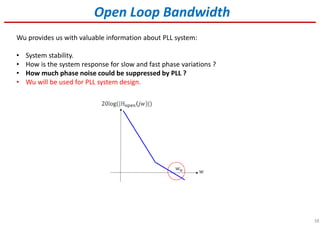

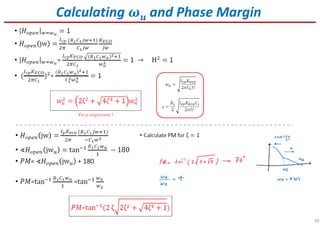

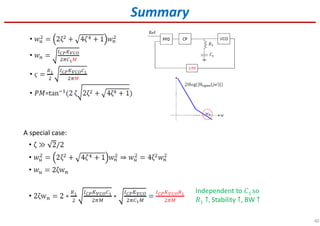

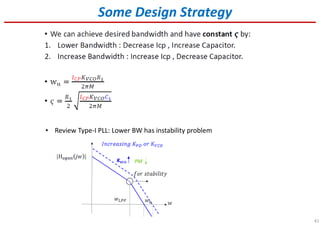

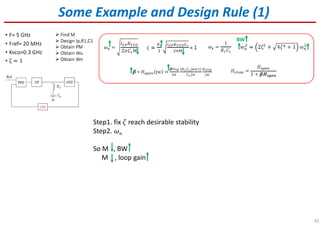

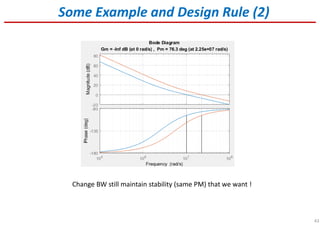

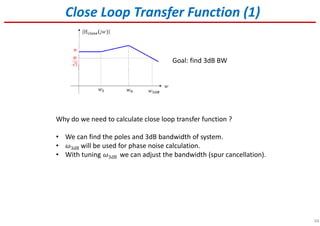

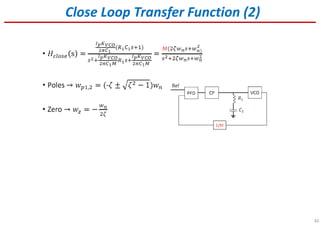

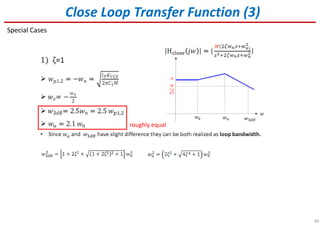

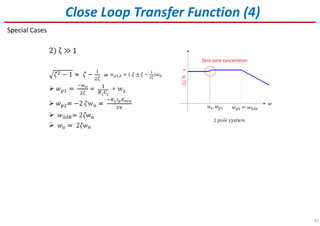

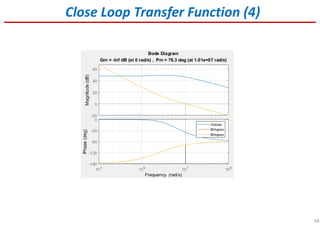

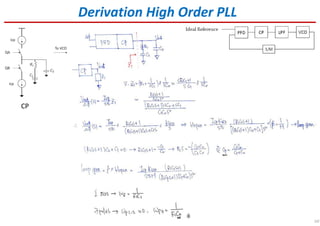

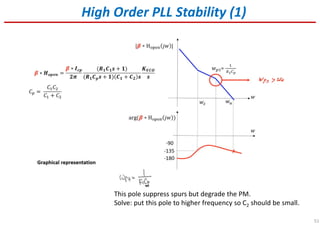

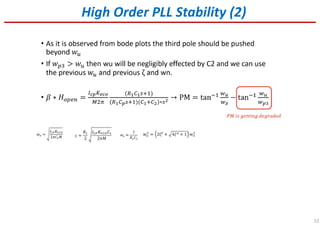

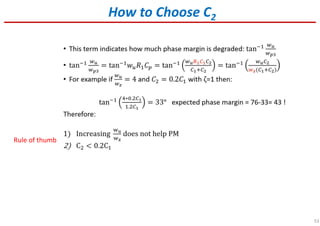

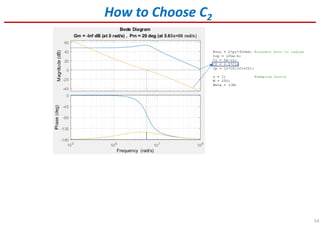

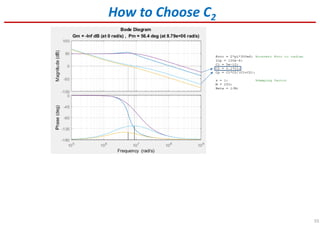

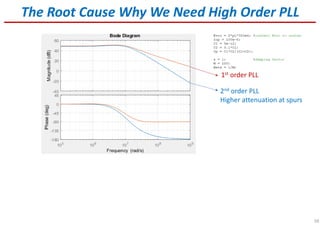

The document provides an overview of phase-locked loops (PLLs), explaining their components such as voltage-controlled oscillators (VCOs) and phase detectors (PDs), as well as their functionality in synchronizing and tracking frequency signals. It discusses issues like stability, phase noise, and the importance of components like charge pumps and phase/frequency detectors in improving performance. Additionally, it outlines design strategies and considerations for achieving optimal bandwidth and minimizing ripple effects in PLLs.