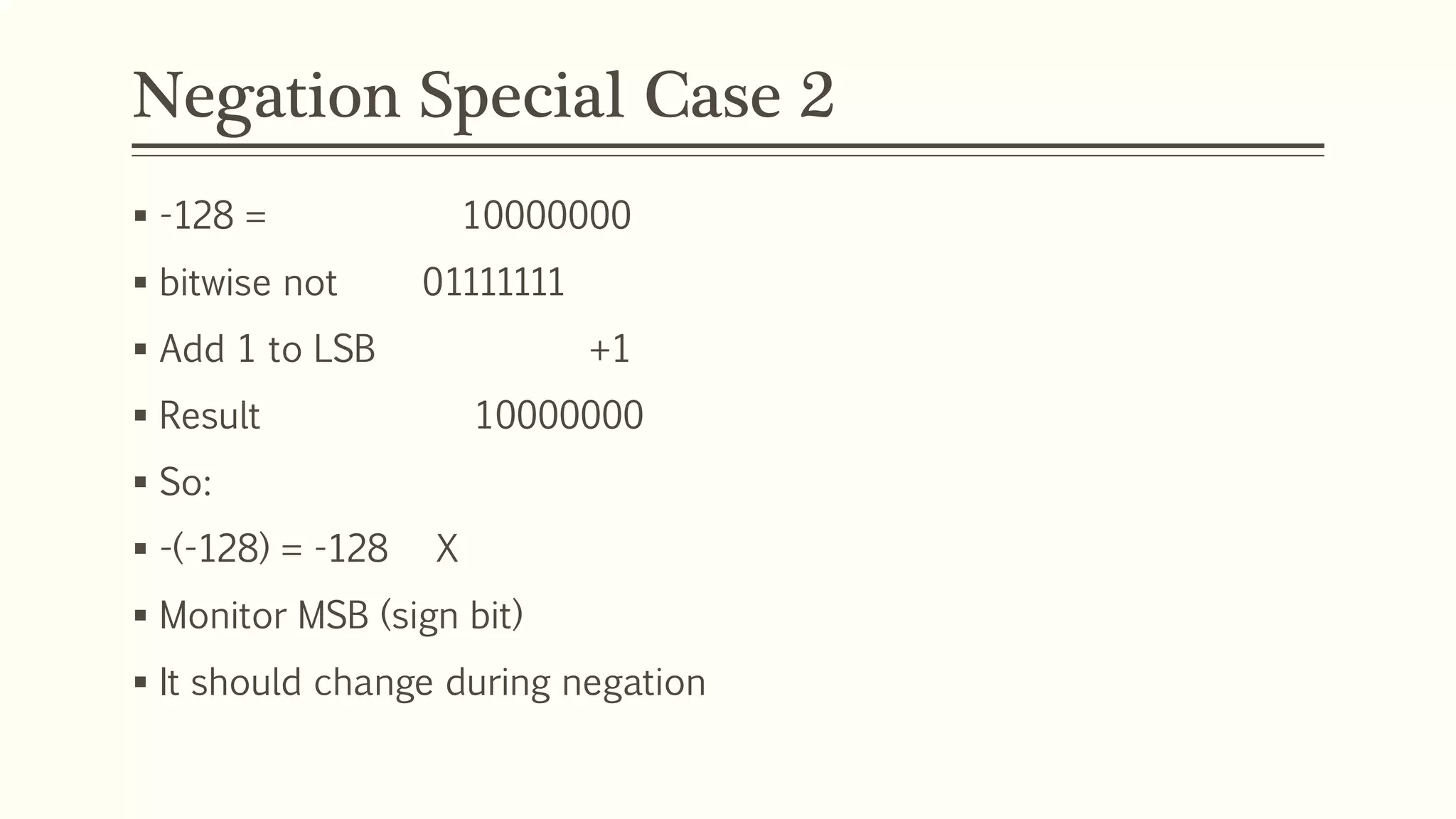

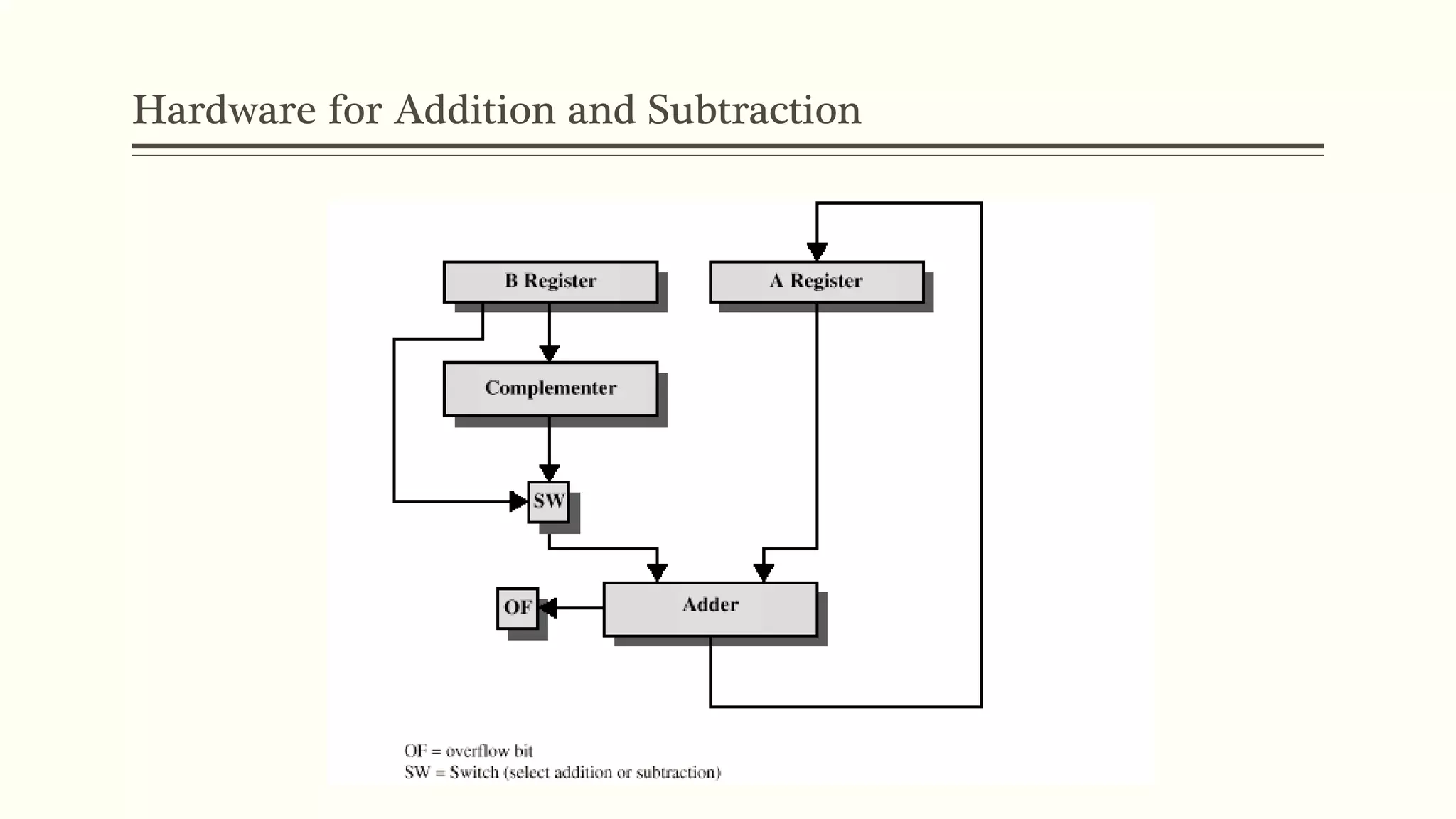

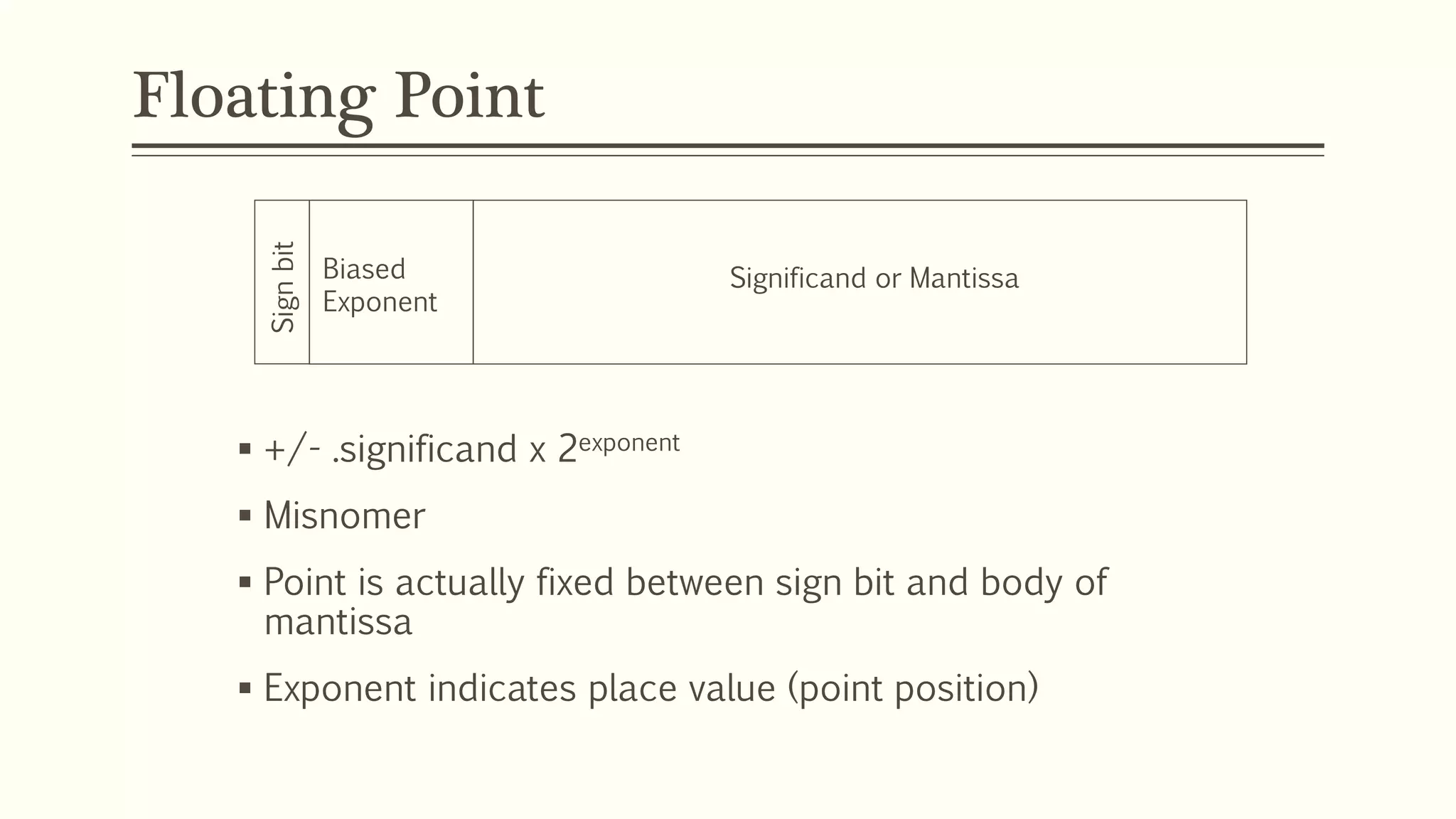

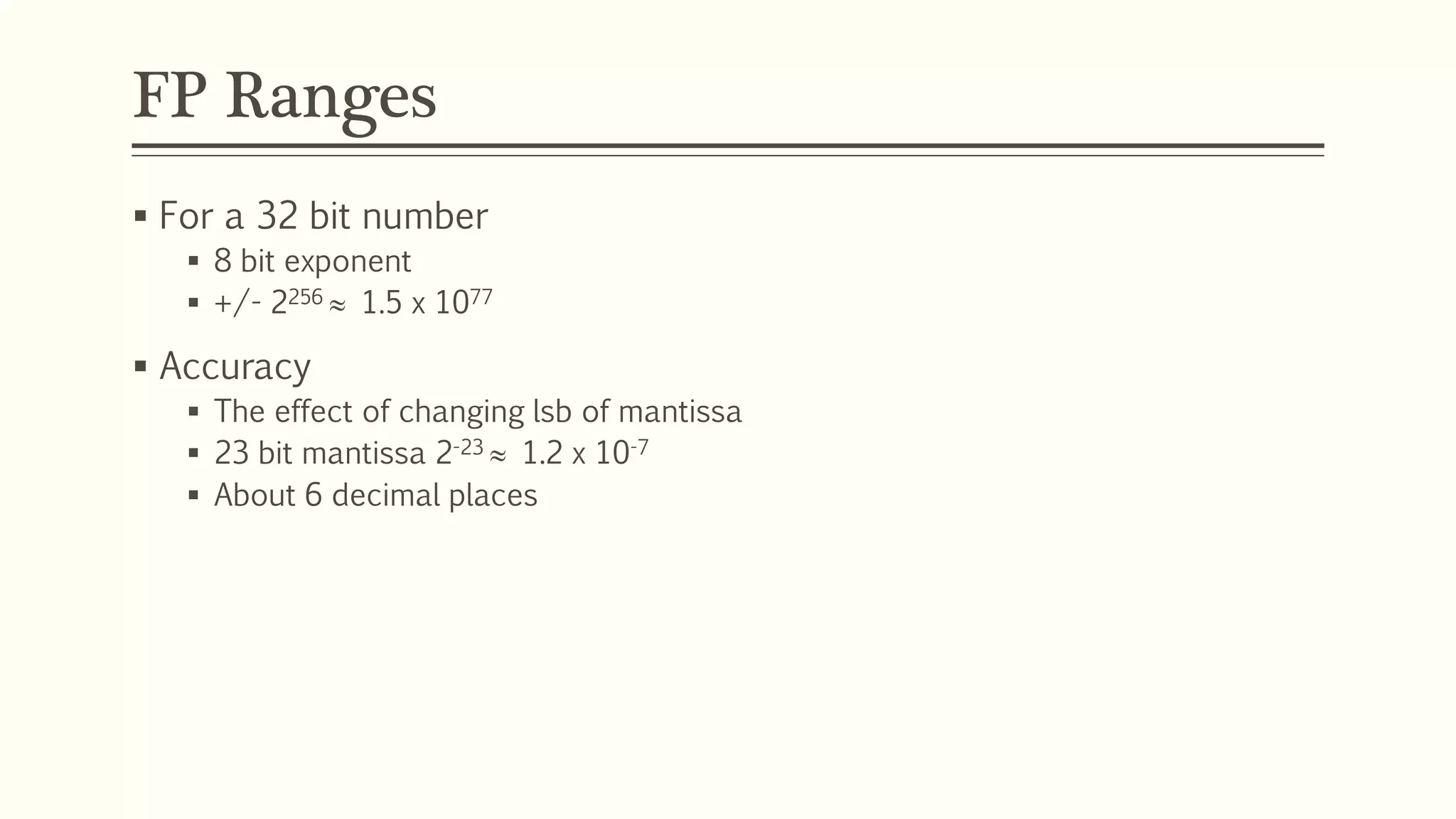

The document discusses the Arithmetic Logic Unit (ALU) and how it handles integer and floating point arithmetic in a computer. The ALU performs calculations and is supported by other parts of the computer. It describes how integers are represented in binary using sign-magnitude and two's complement methods. Two's complement allows for easier arithmetic operations. Floating point numbers use a sign bit, exponent field, and significand to represent values with a fixed or floating decimal point. IEEE 754 standard defines common floating point formats. The ALU performs operations on operands from registers and stores results back in registers.