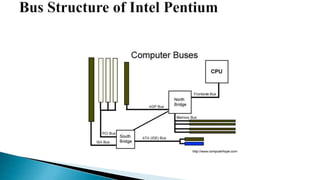

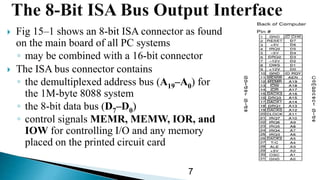

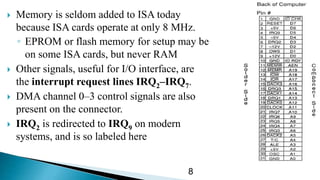

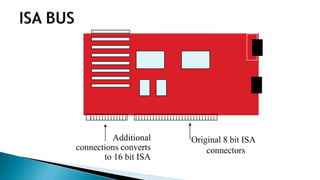

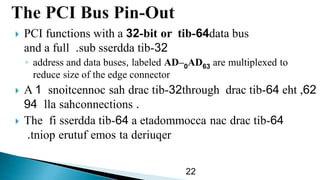

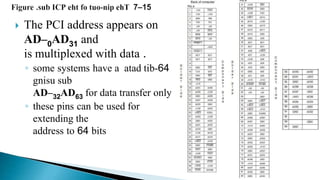

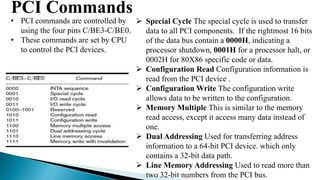

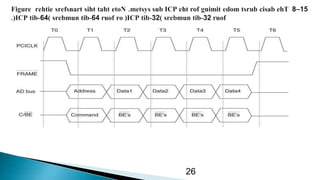

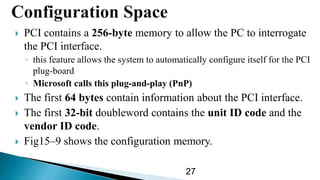

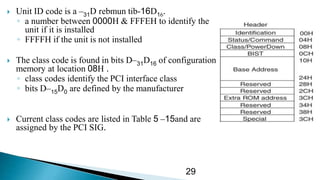

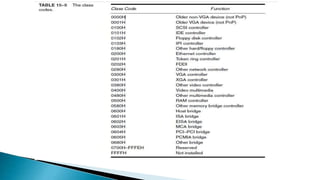

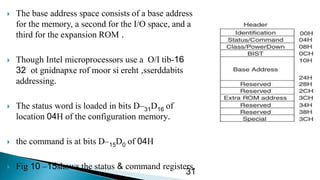

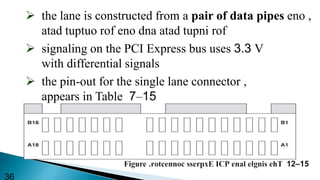

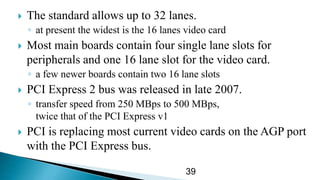

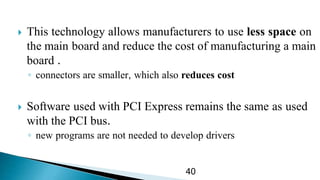

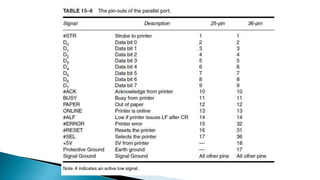

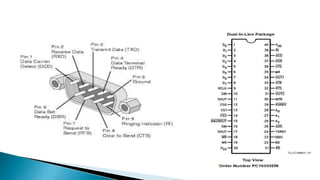

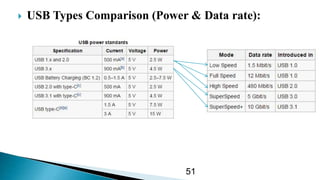

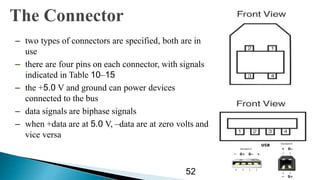

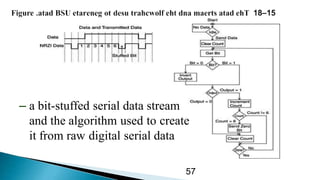

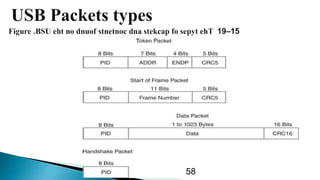

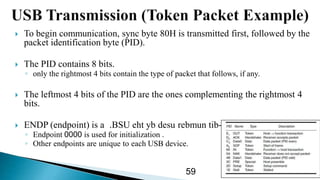

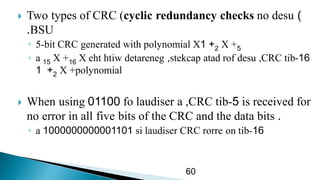

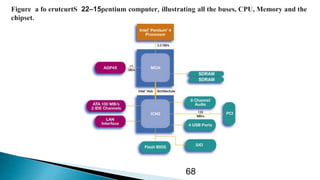

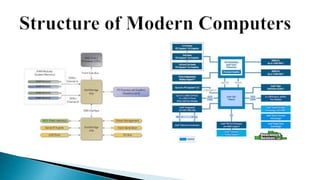

The document provides an overview of various computer bus architectures including ISA, PCI, and USB, detailing their functionalities, data transfer rates, and historical significance. It describes the evolution of these bus systems, highlighting technological advancements such as plug-and-play features in PCI and serial data transfer in PCI Express. Additionally, it addresses parallel and serial communication interfaces, discussing their configurations and operational mechanisms.