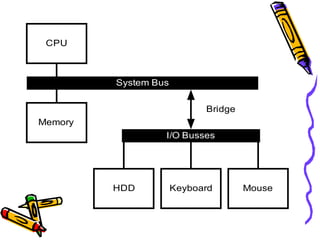

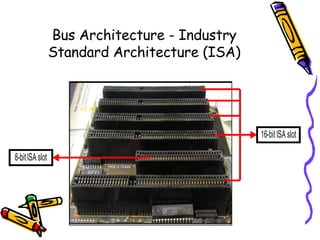

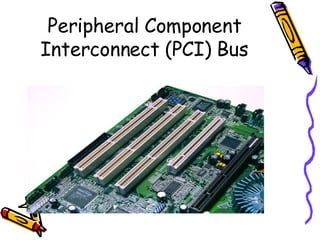

Expansion buses connect the CPU to other components on the system board and allow communication between these components. There have been several standard expansion bus architectures over time including ISA, EISA, VESA Local Bus, and PCI buses. PCI bus is the most widely used today as it offers high throughput, scalability, and a standard specification. Expansion buses define system resources like interrupts, memory addresses, and DMA channels that components use to communicate on the bus.