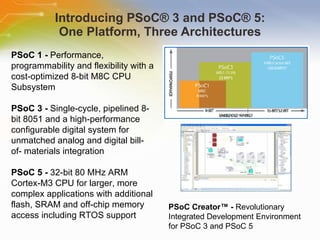

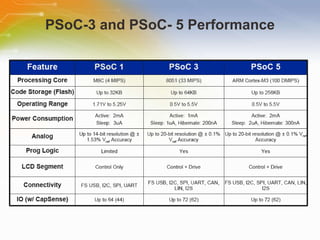

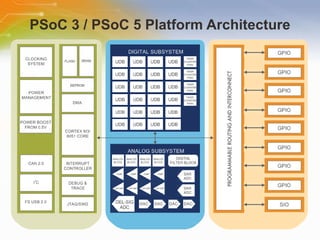

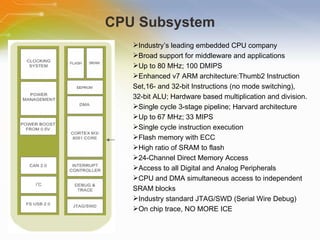

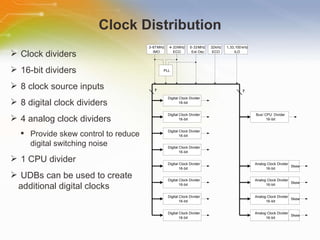

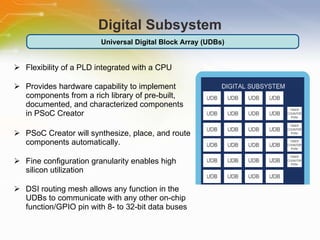

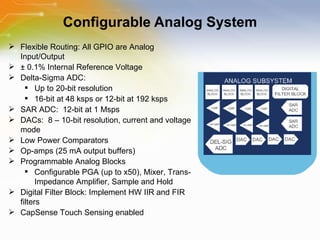

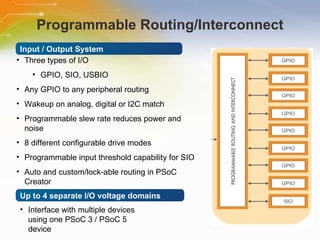

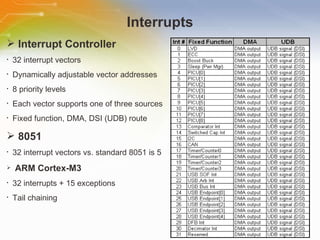

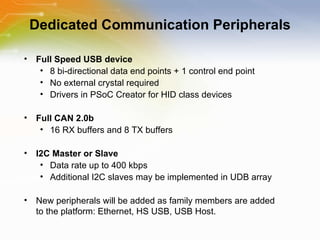

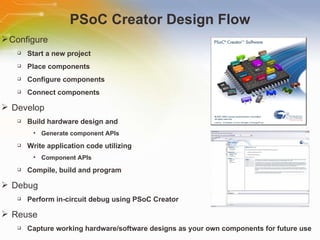

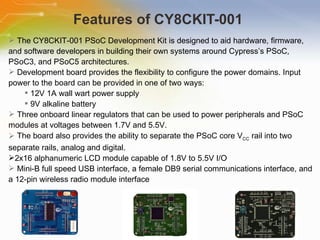

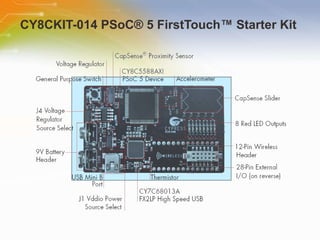

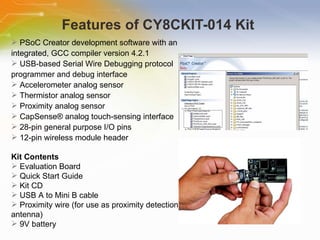

The document provides an overview of Cypress Semiconductor's Programmable System on Chip (PSoC)-5. It describes the key features of PSoC-5 including its 32-bit ARM Cortex-M3 CPU, digital and analog subsystems, low power modes, communication peripherals, and PSoC Creator design flow. It also summarizes the features of the CY8CKIT-001 and CY8CKIT-014 kits for developing with PSoC-5.