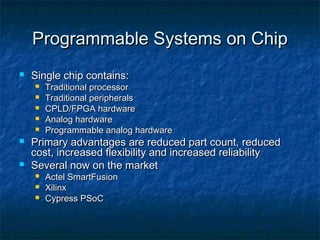

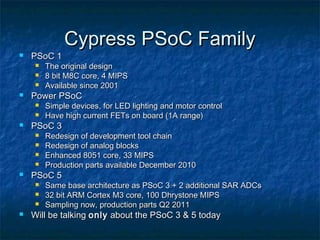

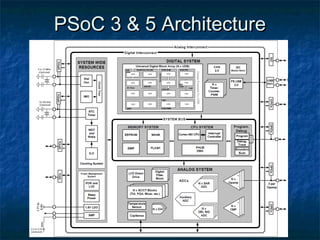

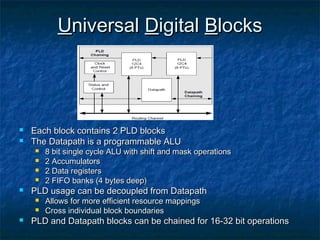

The document provides an overview of the Cypress PSoC (Programmable Systems on Chip) processors, focusing on the PSoC 3 and PSoC 5 models, which integrate programmable analog and digital functionalities with traditional processing cores. It outlines the key features, advantages, development tools, and best practices for utilizing these processors in various applications, particularly in robotics. Additional resources and contact information are also provided for further assistance.