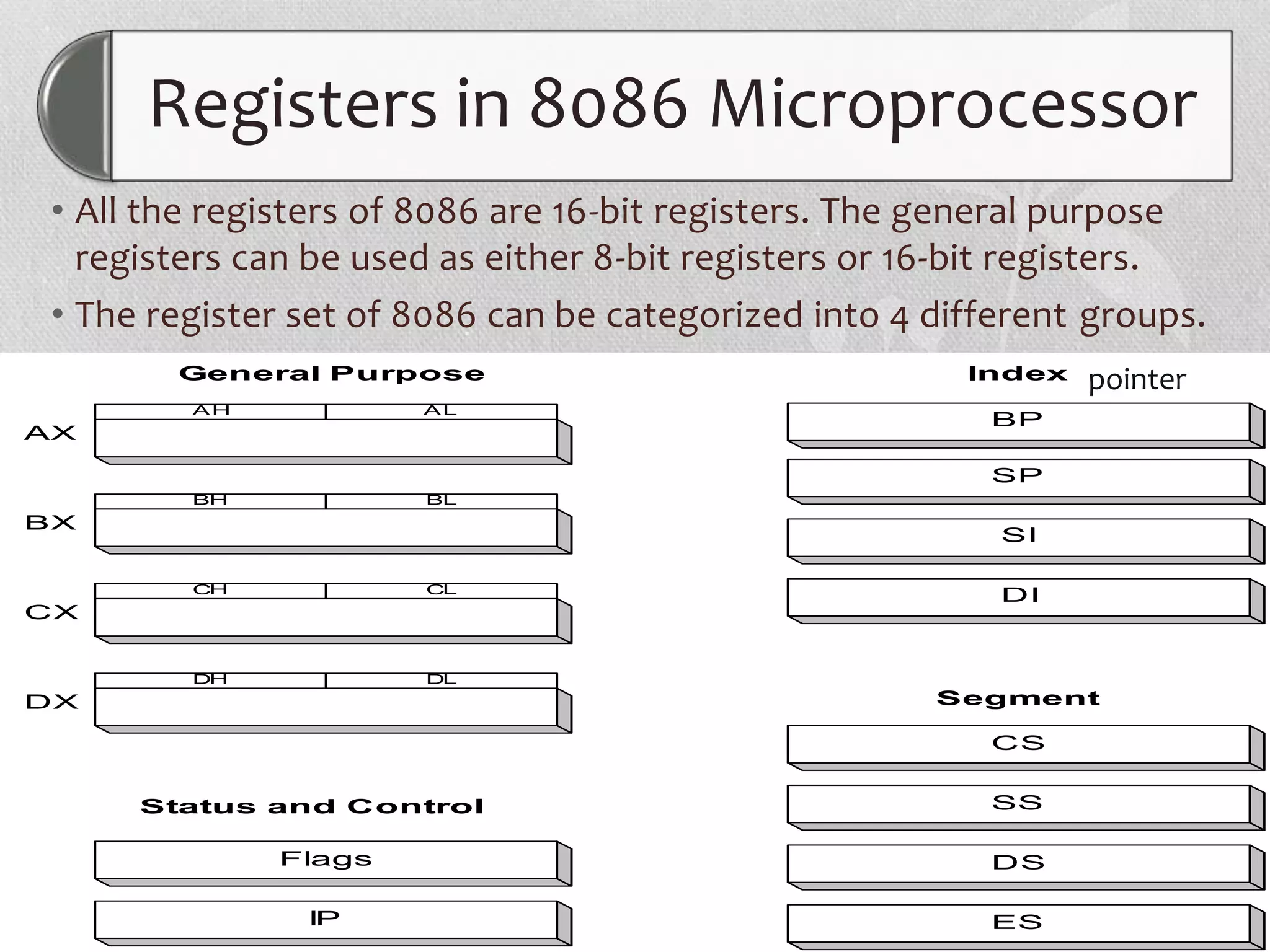

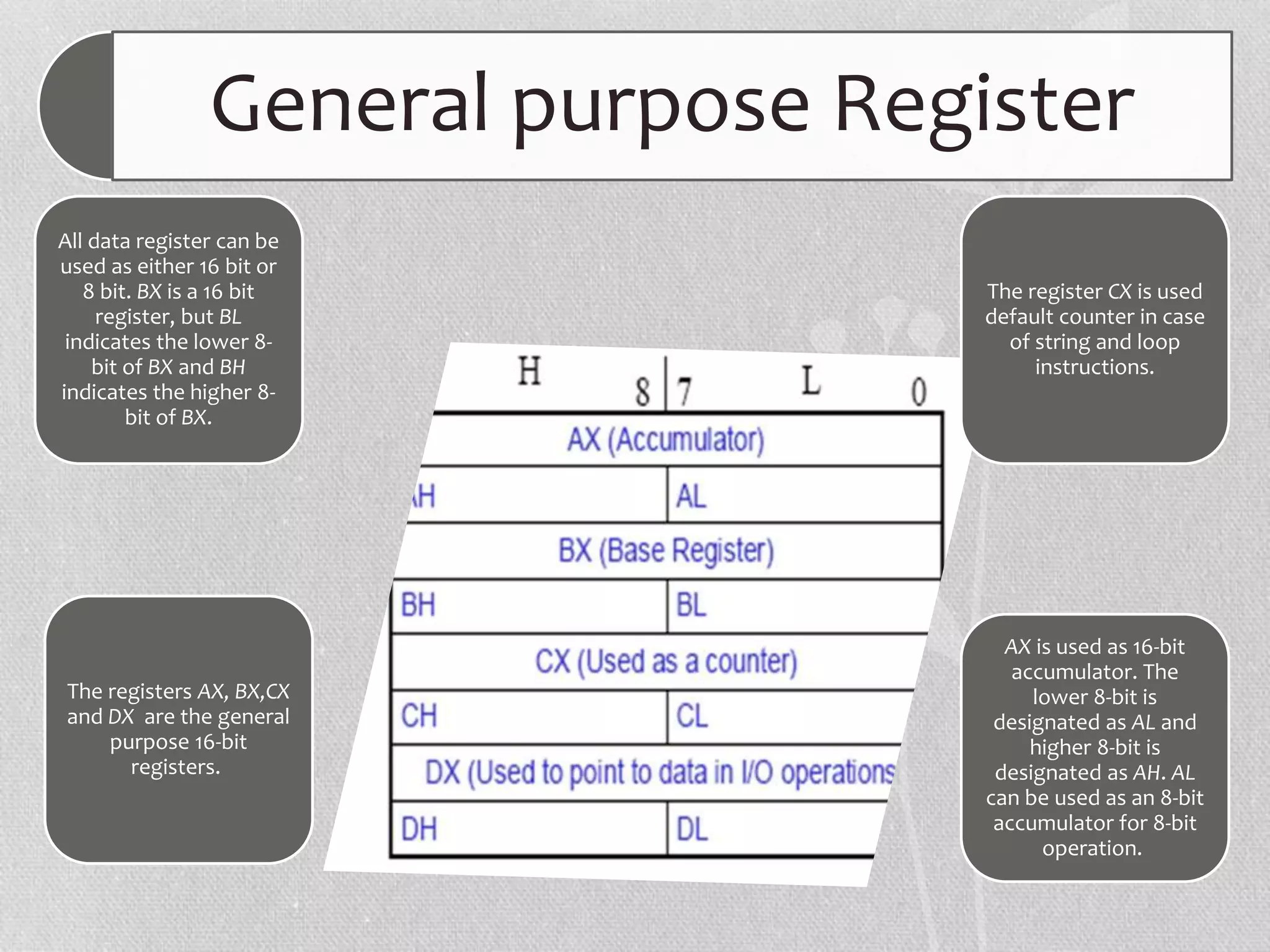

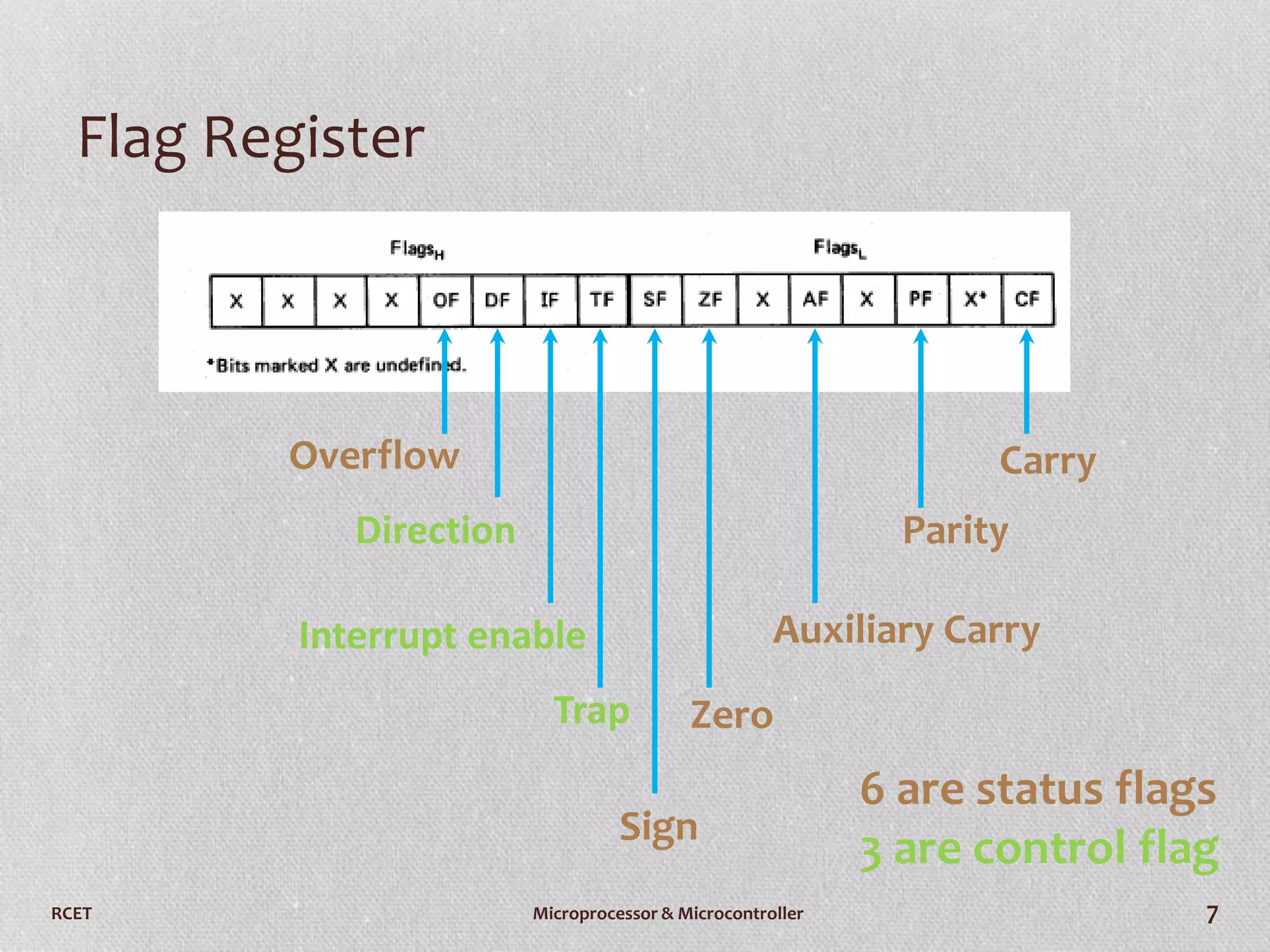

The document summarizes the register organization of the 8086 microprocessor. It discusses that the 8086 has 16-bit registers that can be used as either 8-bit or 16-bit. The registers are categorized into general purpose, segment, index, status and control flag, and pointer registers. The general purpose registers include AX, BX, CX, and DX that can be used for data manipulation. The segment registers point to different memory segments. The index registers include SI and DI that are used for addressing data. The flag register contains status flags for results and control flags for CPU operation.