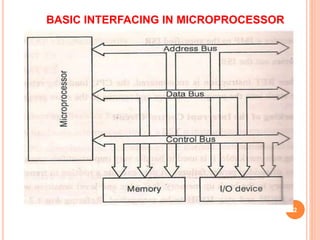

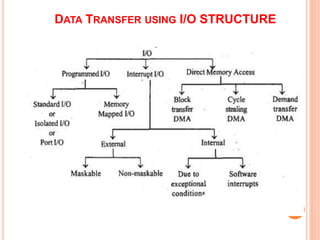

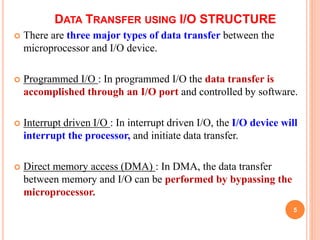

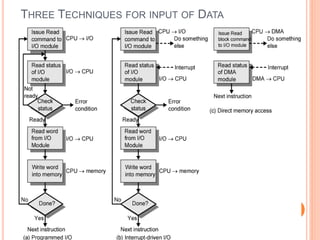

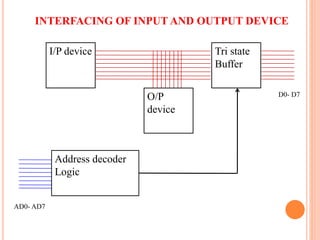

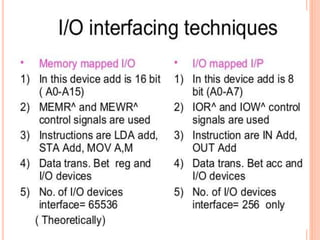

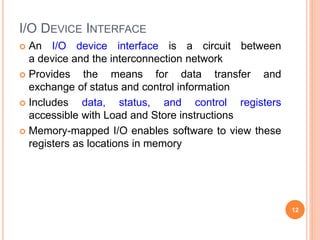

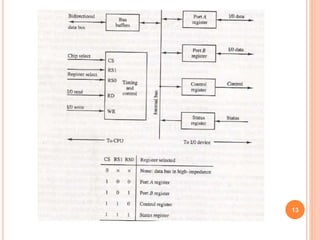

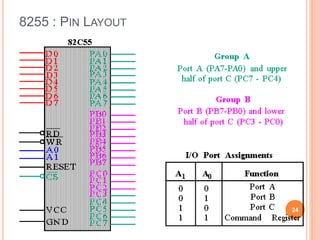

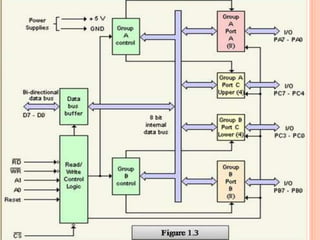

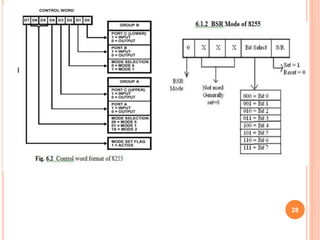

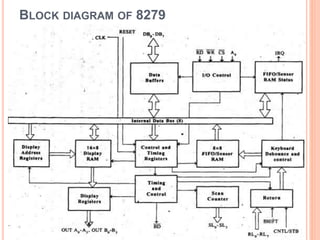

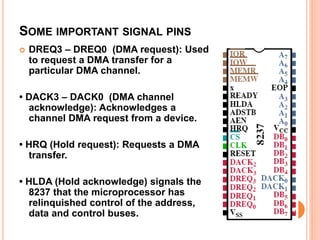

This document discusses memory and I/O interfacing using microprocessors. It describes how memory and I/O devices are interfaced by connecting data and address lines, as well as control signals. It also discusses the three main types of data transfer between microprocessors and I/O devices: programmed I/O, interrupt-driven I/O, and direct memory access. Additionally, it provides information on common I/O interface chips like the 8255 Programmable Peripheral Interface and the 8279 Keyboard/Display Controller.