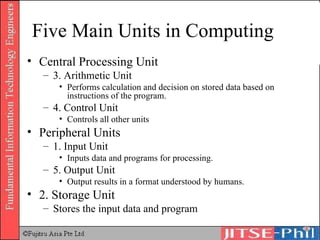

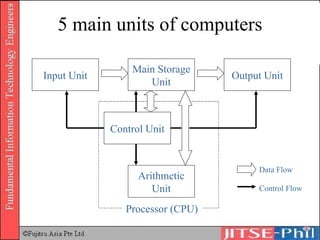

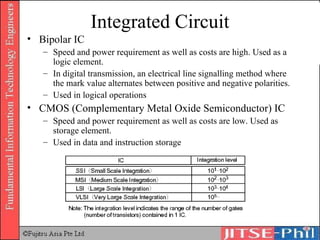

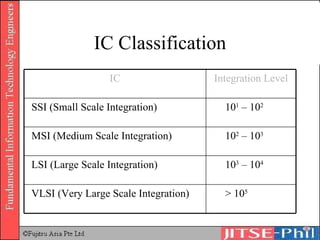

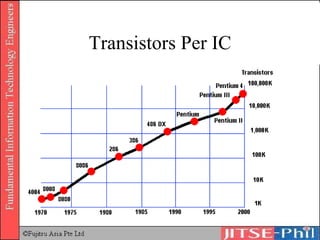

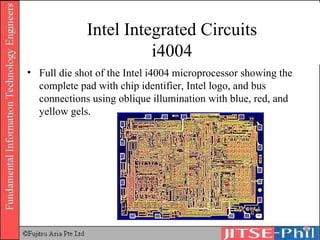

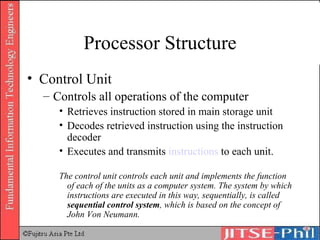

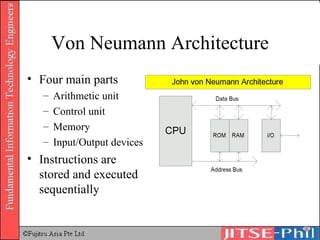

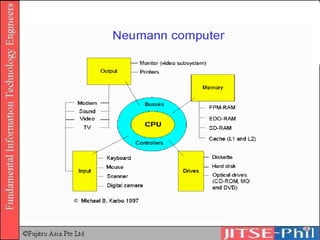

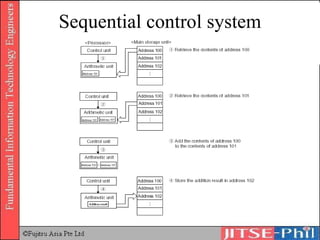

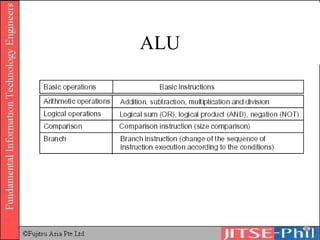

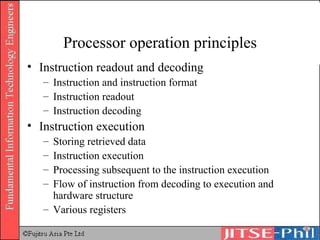

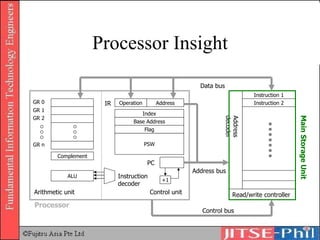

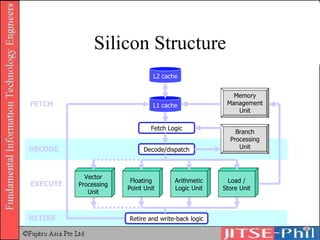

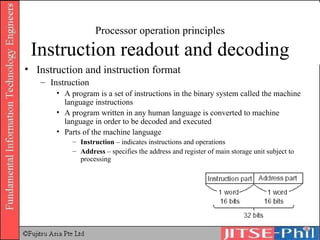

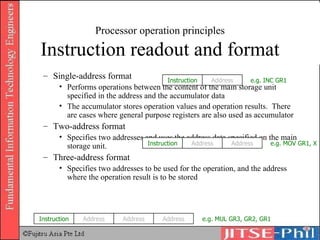

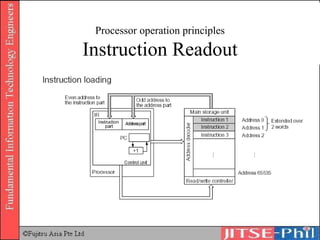

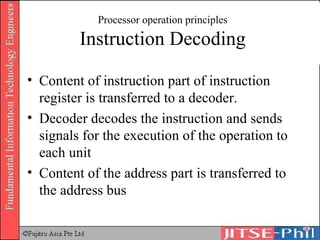

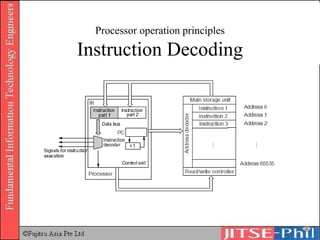

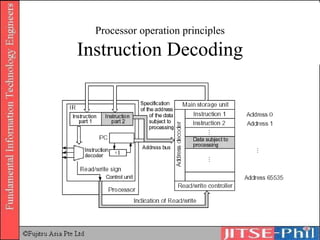

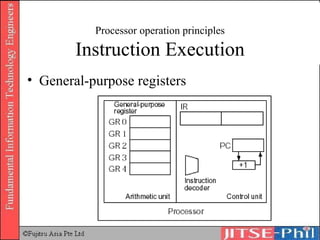

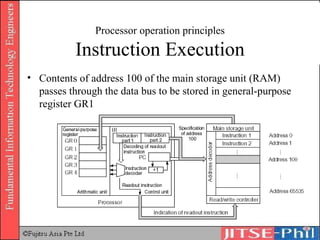

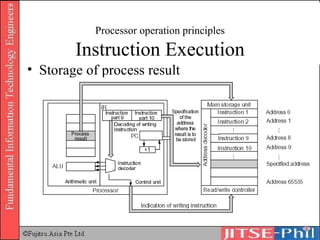

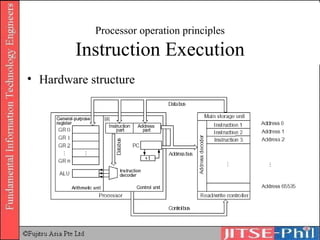

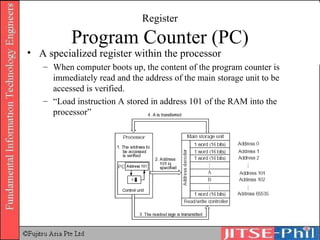

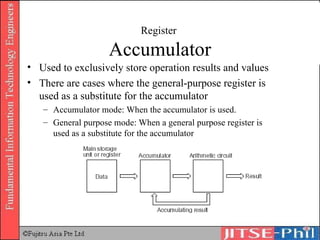

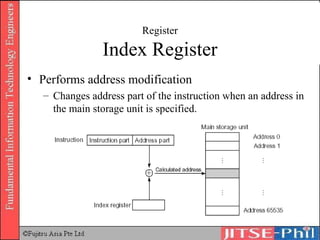

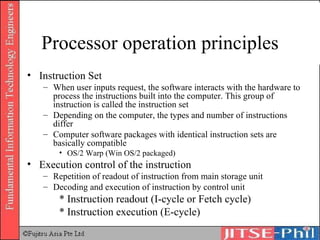

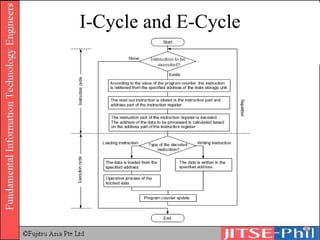

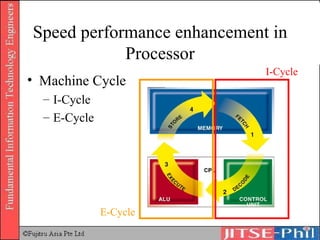

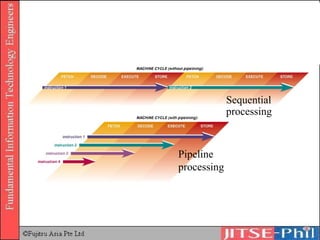

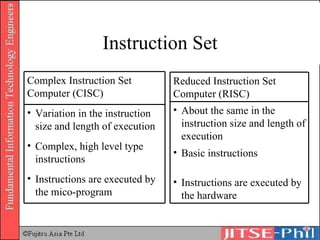

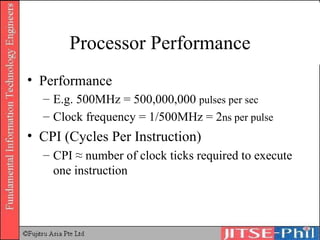

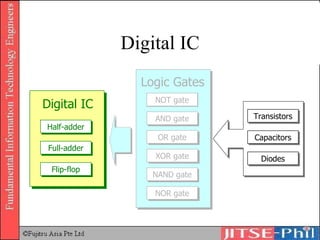

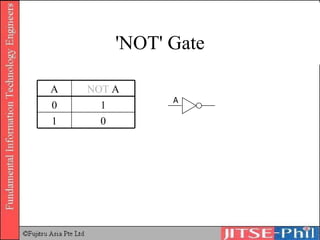

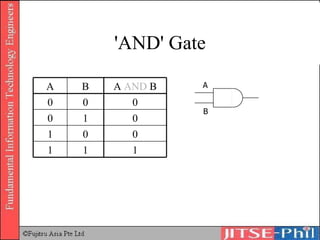

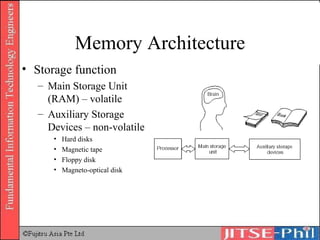

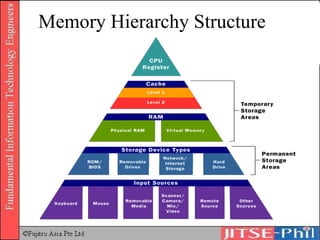

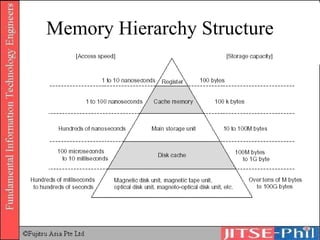

The document summarizes the five main units of a computer system: input, output, storage, arithmetic, and control units. It describes the functions of hardware components like integrated circuits, memory (RAM and ROM), and the processor. The processor has a control unit that retrieves and decodes instructions from memory and an arithmetic logic unit that performs calculations. Instructions are fetched, decoded, executed, and retired in sequence using the von Neumann architecture.