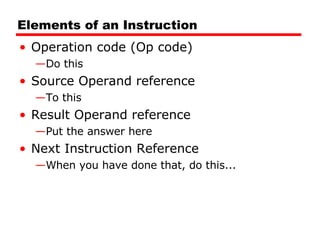

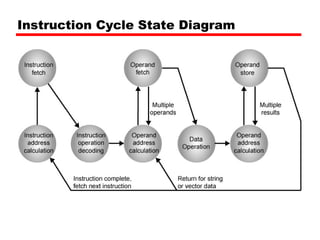

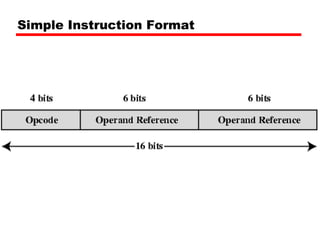

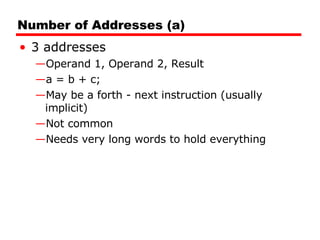

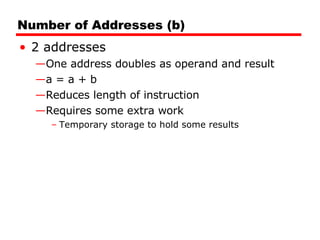

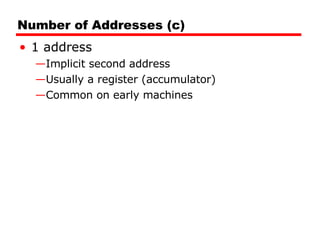

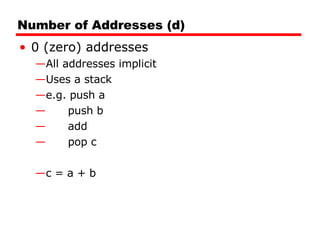

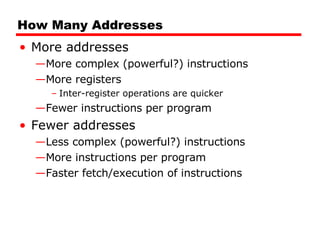

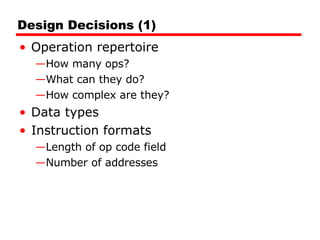

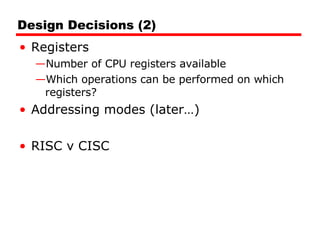

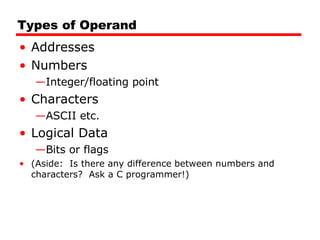

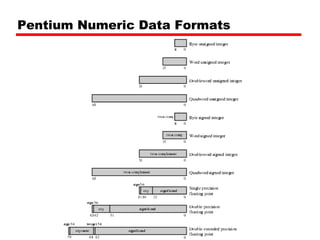

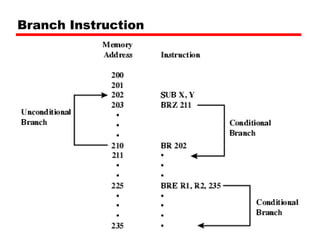

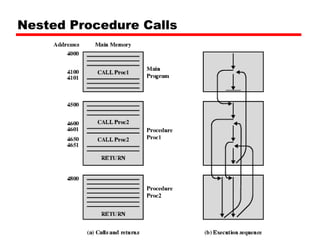

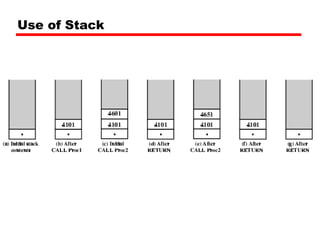

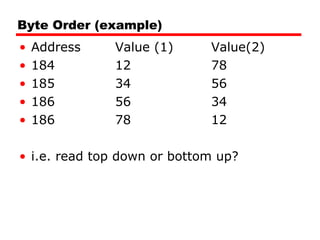

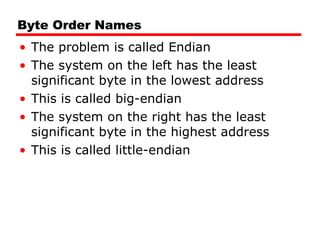

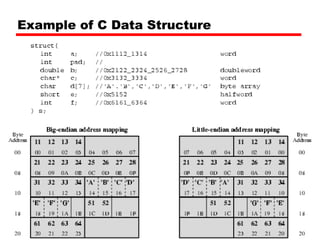

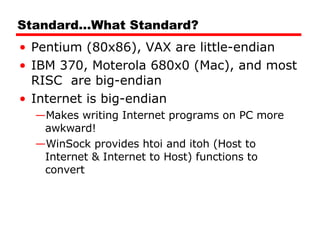

The document discusses instruction sets and their characteristics. It covers topics like instruction formats, types of instructions, addressing modes, operand types, and byte ordering. Instruction sets have operation codes, operands, and addressing that reference locations in memory or registers. Design decisions for instruction sets include the operation repertoire, number of registers, and addressing modes.