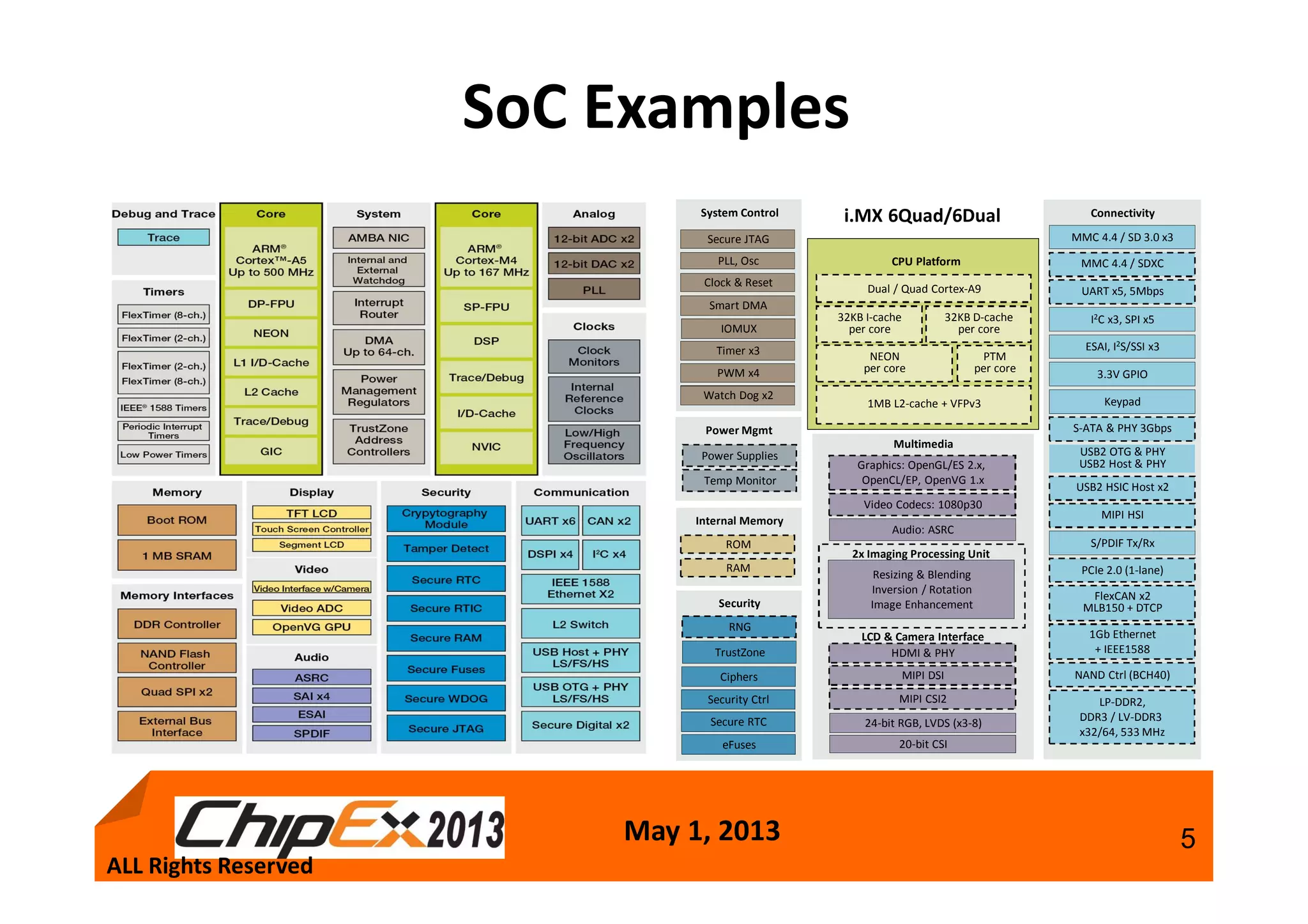

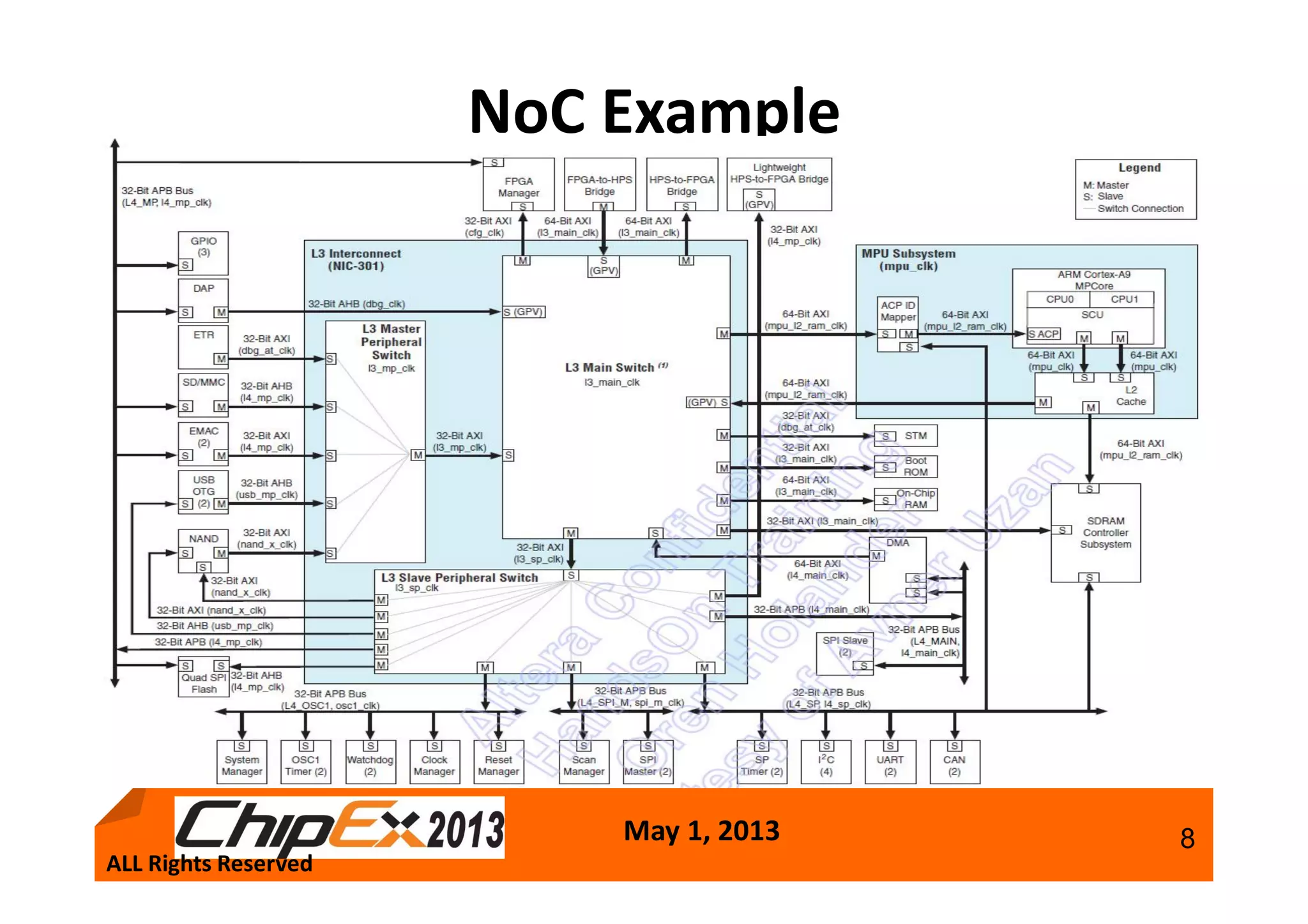

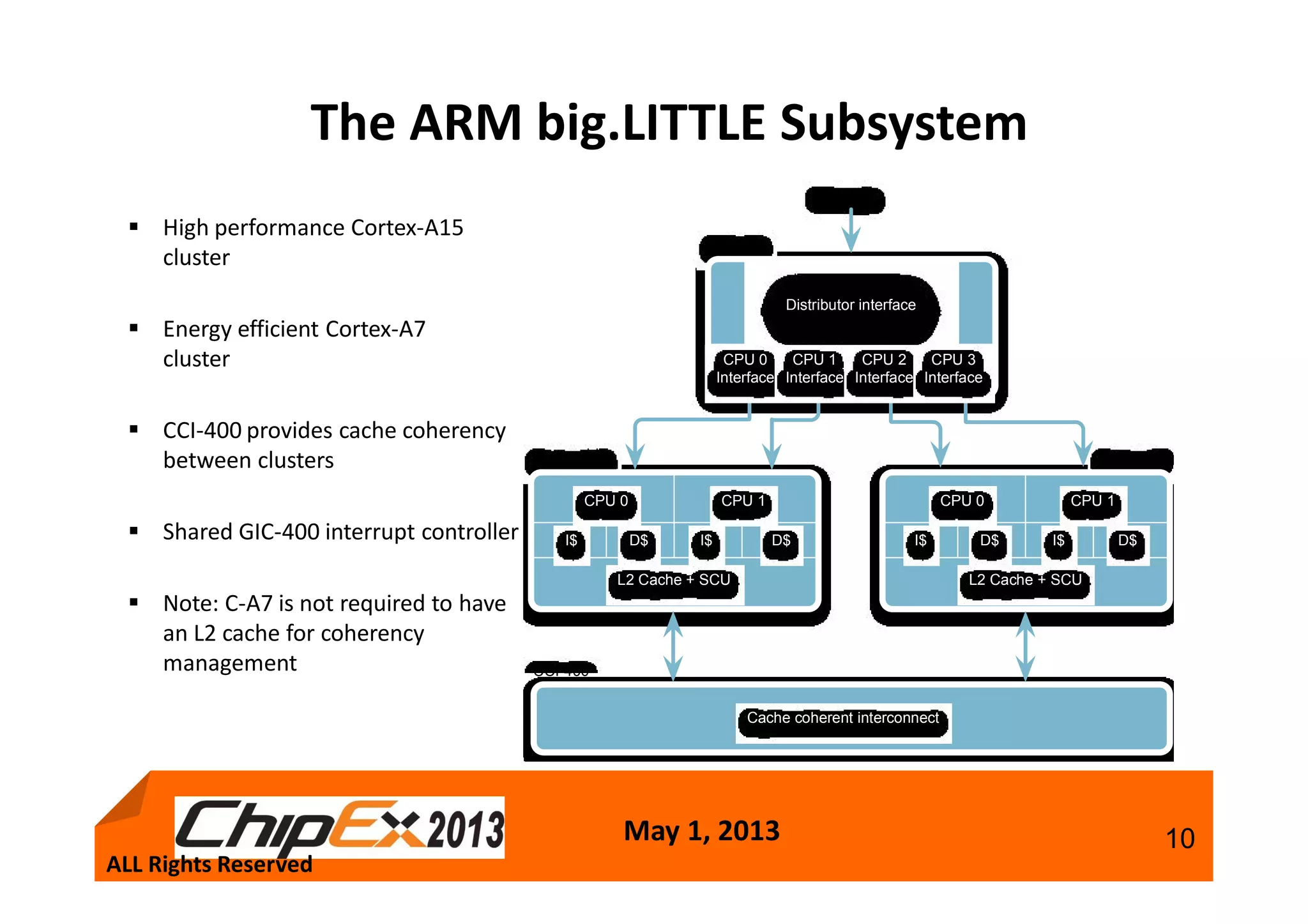

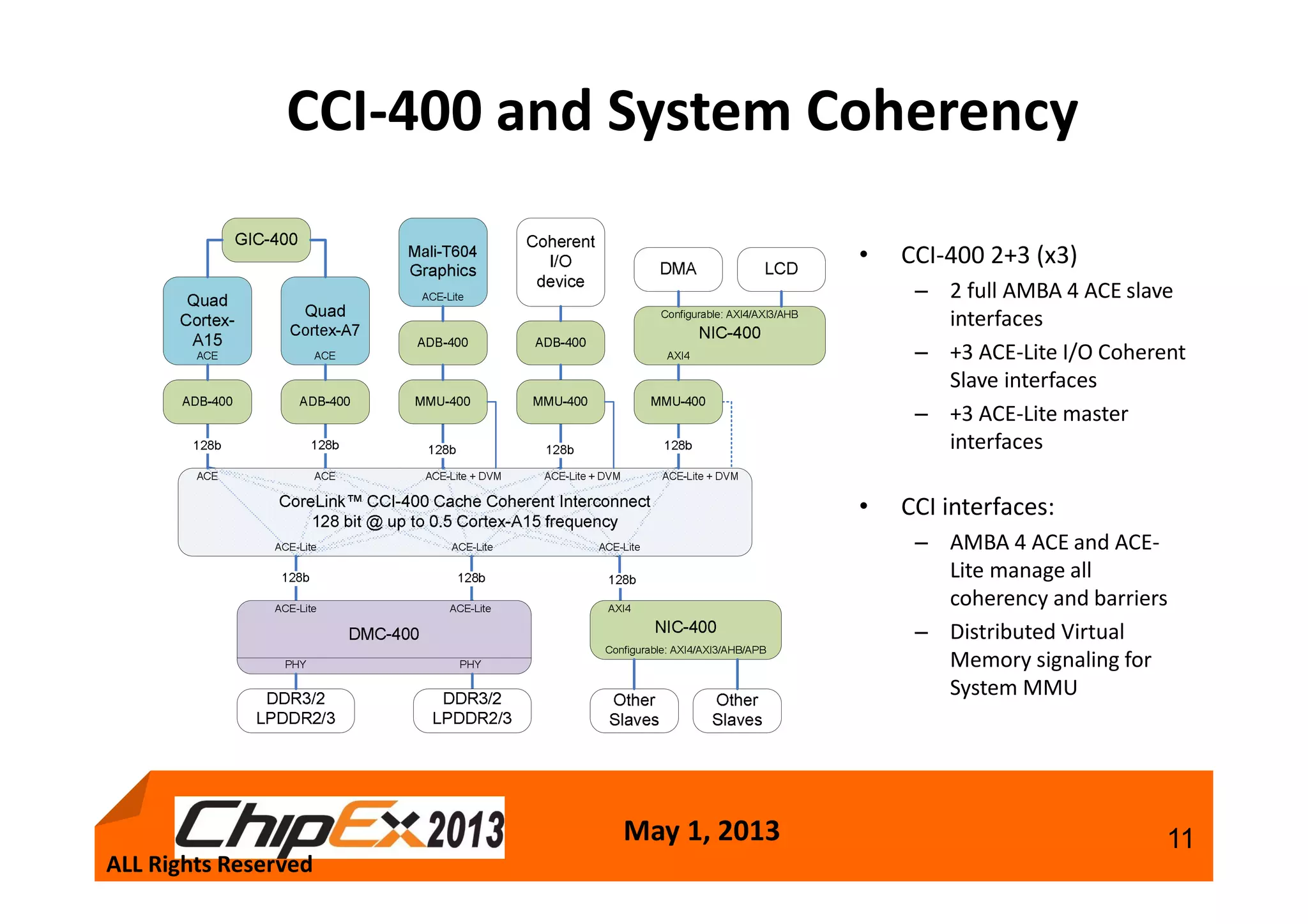

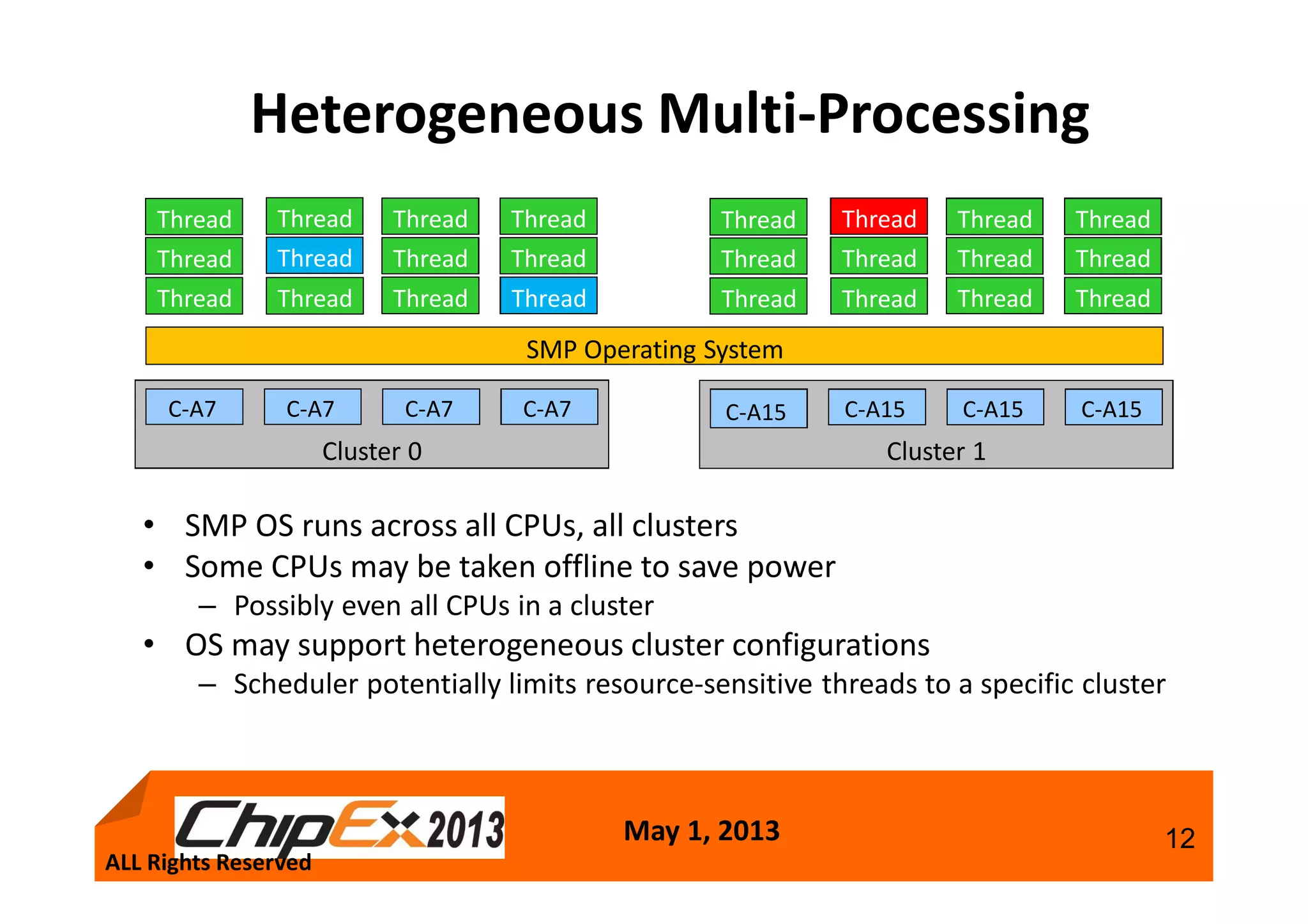

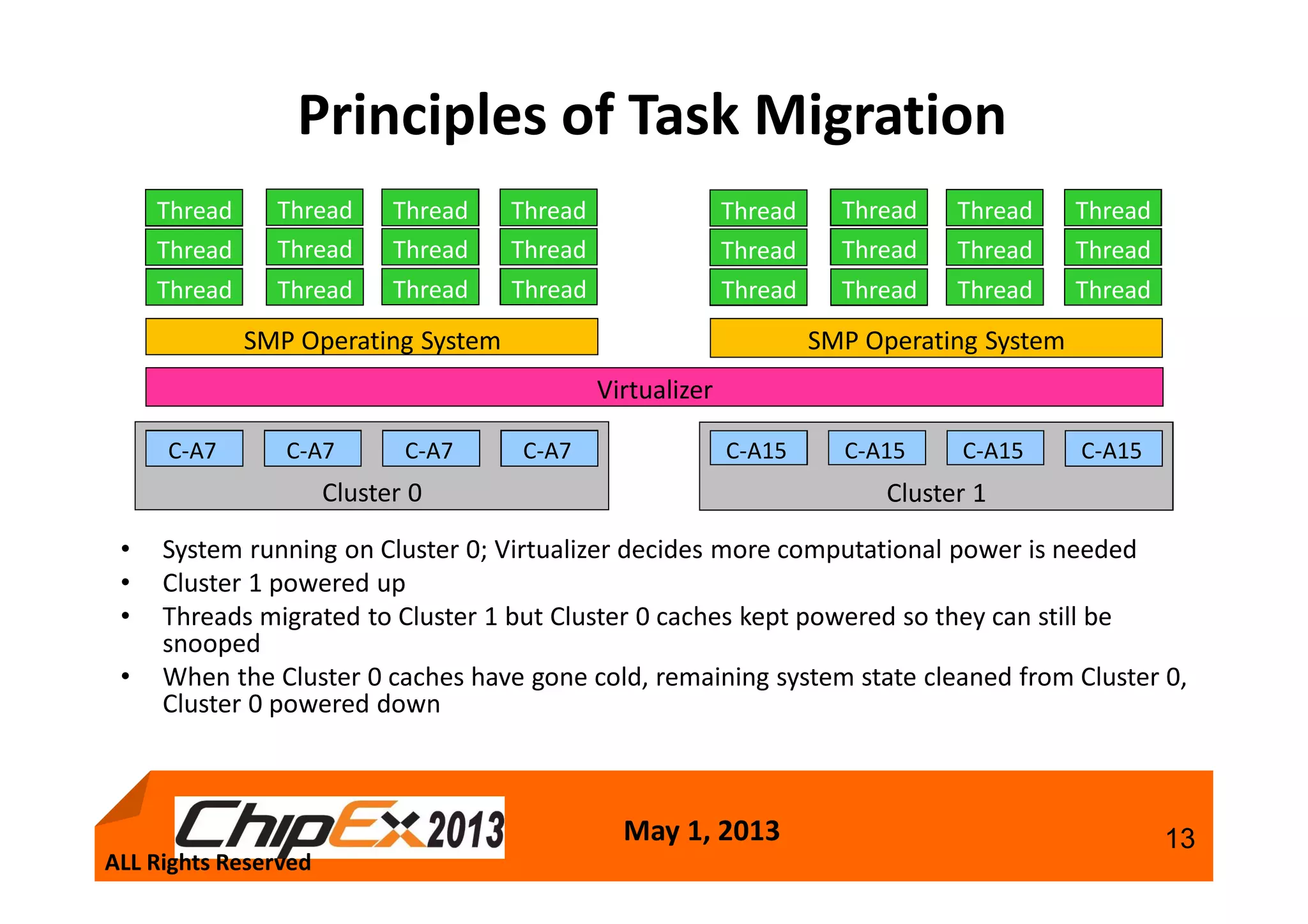

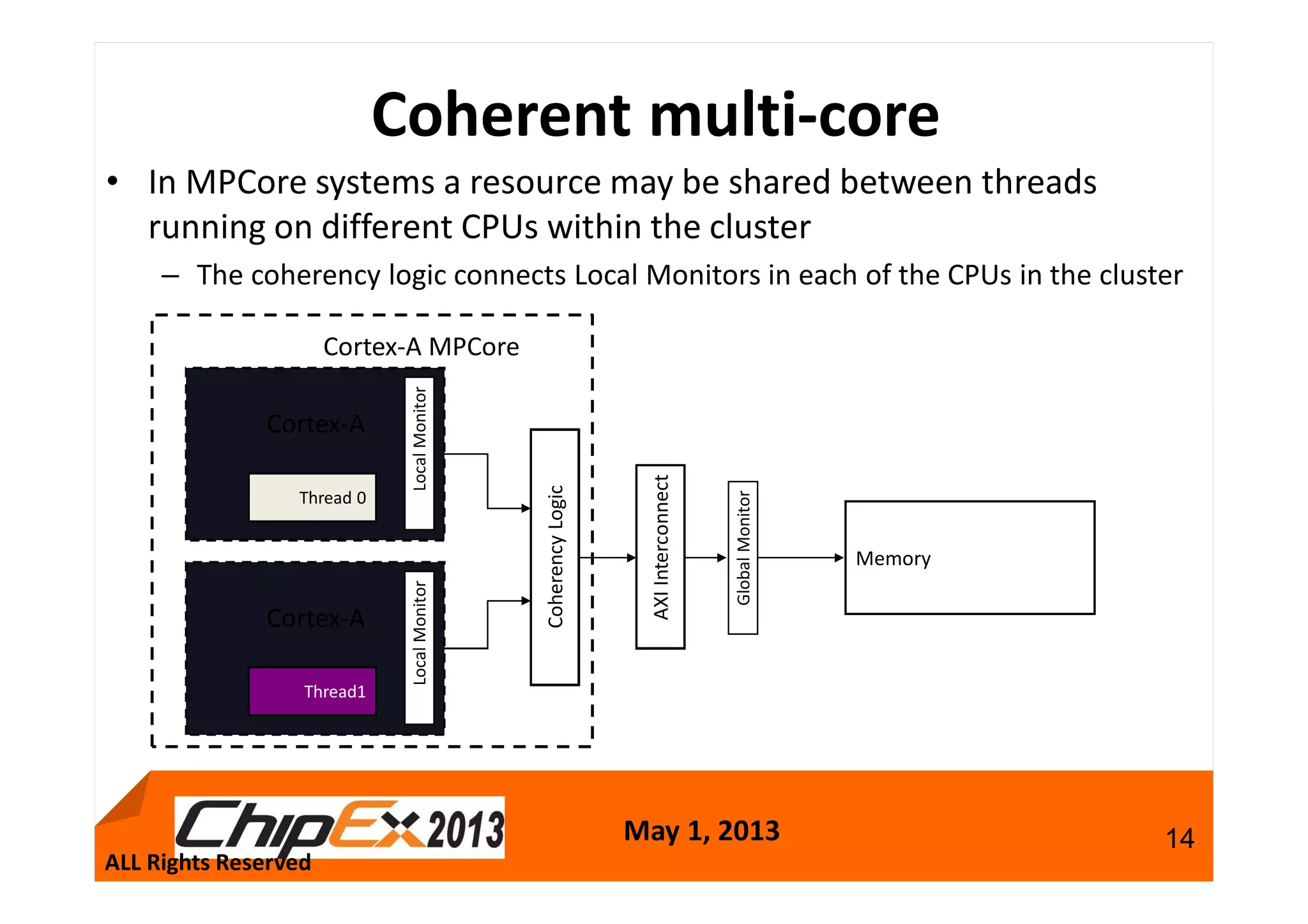

The document discusses trends in system-on-chip (SoC) and network-on-chip (NoC) architectures, including the integration of multiple CPU cores, hardware accelerators, and peripherals on a single chip connected by an on-chip network. NoCs are presented as a scalable solution to connect the growing number of computational resources in modern SoCs. Examples of ARM-based multicore SoCs including the big.LITTLE subsystem are provided to illustrate the challenges of cache coherency, interrupts, and task migration in multicore systems.