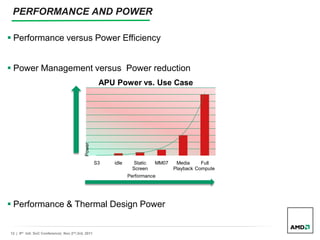

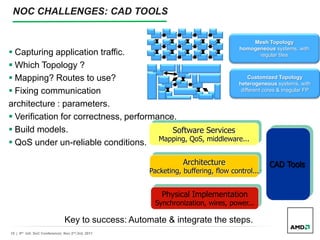

This document summarizes a presentation given at the 9th International SoC Conference on November 2nd-3rd, 2011. The presentation discusses trends in processor design, including the transition to multi-core and heterogeneous systems. It introduces Fusion System Architecture (FSA), which combines CPU and GPU capabilities on a single die. The presentation also discusses challenges in areas like power management, high-speed interconnects, 3D stacking, verification efforts, IP integration, and TLM-RTL co-simulation.

![14 | 9th Intl. SoC Conference| Nov 2nd,3rd, 2011

NOC’S: FROM BUSES TO NETWORKS:

[Friedman Harel:10]

Note: This slide presents industry specific information does not relate to AMD NoC status](https://image.slidesharecdn.com/amd9thintlsocconf-130713202956-phpapp01/85/FUSION-APU-TRENDS-CHALLENGES-IN-FUTURE-SoC-DESIGN-14-320.jpg)

![16 | 9th Intl. SoC Conference| Nov 2nd,3rd, 2011

Synchronous Delay Insensitive

Global None

Timing Assumptions

Less Detection

Local Clocks, Interaction

with data (becoming aperiodic)

A complete spectrum of approaches to system-timing exist

[Mullins06-07]

NOC CHALLENGES: BEYOND GLOBAL SYNCHRONY

Delay Insensitive](https://image.slidesharecdn.com/amd9thintlsocconf-130713202956-phpapp01/85/FUSION-APU-TRENDS-CHALLENGES-IN-FUTURE-SoC-DESIGN-16-320.jpg)

![21 | 9th Intl. SoC Conference| Nov 2nd,3rd, 2011

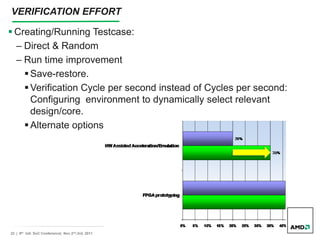

VERIFICATION EFFORT

Debugging

– Seamless debug across

h/w and software[especially SW]

Testbench Development:

– Several methodologies

VMM,OVMUVM.

New developments

[Unified strategy]

– UCIS,UVM TLM2.0

– Coverage trend

Address Gaps in VHDL,

System C coverage](https://image.slidesharecdn.com/amd9thintlsocconf-130713202956-phpapp01/85/FUSION-APU-TRENDS-CHALLENGES-IN-FUTURE-SoC-DESIGN-21-320.jpg)

![30 | 9th Intl. SoC Conference| Nov 2nd,3rd, 2011

REFERENCES

[1] Wilson Research Group-MGC study blog 2011.

[2] AMD Coolchip2011 presentation. Denis Foley, AMD Sr. Fellow.

[3] Fusion Processors and HPC-2011, Chuck Moore, AMD Corporate

Fellow & Technology Group CTO

[3] AMD Fusion Developer Summit 2011. Phil Rogers, AMD Corporate

Fellow

[4] Fully Asynchronous framework for GALS network on chip. Friedman H

[5]Future of EE, NoC’s presentation. Dr. Srinivasan Murali

[6] Analog IP integration in SoC, IP reuse’09. Mixed language IP integration

DVCoN 2010. Extending Fucntional coverage to SystemC, VHDL-IP’10.

Pankaj S](https://image.slidesharecdn.com/amd9thintlsocconf-130713202956-phpapp01/85/FUSION-APU-TRENDS-CHALLENGES-IN-FUTURE-SoC-DESIGN-30-320.jpg)